ICC II 6 CTS setup(时钟树综合之前的设置)

本章介绍的CTS setup应该在 最前面就设置好的,最晚placement之前 也需要设置好了;

object

设置时钟树平衡约束;

解决 预先存在的clock tree elements;

指定时钟树布线的非默认的规则NDRs

指定时序和DRC 的约束;

clock tree balancing

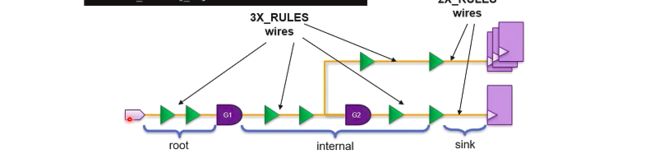

时钟树的开始点和结束点

时钟开始于他们的时钟源,是由 create_clock 定义的;

时钟的终点在于 寄存器 或者宏单元的 时钟引脚;

时钟树综合平衡的点 就是 sink 以及不做平衡的点 ignore pin

默认就做balance 的pin 称作: implicit sink pin, 就是寄存器的时钟端 以及宏单元的时钟端 是默认就做balance的

默认不做balance 的pin 称作: implicit ignore pin, 时序器件的非clock端 三态器件的enable端;

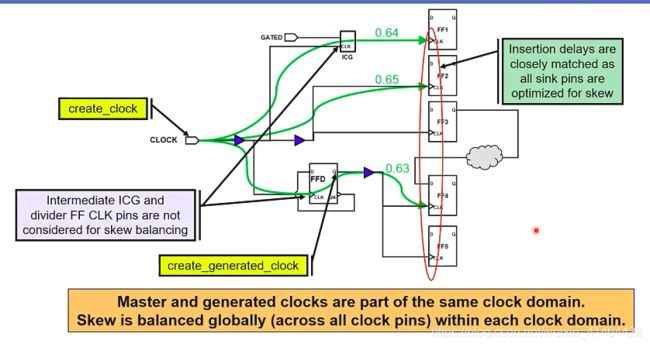

generated clock & gated clock (衍生时钟 门控时钟)

master 和generated clock 是相同时钟域的 那么skew的平衡是全局的 贯穿每个时钟域的所有时钟引脚;

用户定义的 或者 explicit(名确的) sink pins

scenario: 如果一个宏单元明确定义了他的市中医叫 CTS 就会将它视为明确的sink pin 而不是追踪到其内部的寄存器clk端;

如何为宏单元定义一个明确的sink pin:

set_clock_balance_points \

-balance_points [get_pins IP/IP_clk]

# 允许CTS 针对这个pin 去优化skew 以及 insertiondelay targets

#为 IP 的sink pin 附加delay

set_clock_balance_points \

-corner ss125c \

-delay 0.15 -late \

-balance_points IP/IP_CLK

定义clock skew group

如果你想平衡一组从clock tree中挑出来的clock pin,可以定义clock skew group;

目标skew 和这个skew group所属的主时钟的目标skew是相同的;你不能设置独立的额skew;

create_clock_skew_group -mode TEST -object {FF1/CLK FF@/CLK}

exceptions(例外) - mode specific(指定mode)

时钟树例外应用于当前的mode

应用 例外 到多个modes

set_clock_balance_points \

-mode [get_modes "m1 m2"] \

-clock CLOCK \

-consider_for_balancing false \

-balance_points [get_pins AN2/A]

report_clock_balance_points

## sink 的例外能够是 corner-specific (指定Corner 的)

set_clock_balance_points \

-...

-Corner {c2}

# 如果没有指定Corner name sink 的例外是应用于所有的Corner 的;

(auto exceptions)自动例外

用户定义的constrain可能会不全 或者 在balance时存在困难,ICC 会自动加一些exception (工具期望的一些情况)

CTS 能够自动的解决时钟树平衡的冲突;

cts.common.enable_auto_exceptions

#来控制 默认是打开的

case1: 由于缺失generated clock的标记(只定义了clka 的generate clock), 导致两个时钟之间的冲突;

auto-exception : Derive exclude exception for the clock with missing generated clock;(会自动把clockb 排除掉)

case2: 在cell的内部pin 既是 sink pin 也是output pin

auto-exception : 将sink pin 先排除掉 只考虑clock_out pin的平衡 sink pin 只考虑DRC.在后期再balance skew;

case3: 宏单元内部max_clock_tree_path 与min_clock_tree_path的skew 大于 50ps

auto-exception : 仅考虑max_delay, 不讲内部的skew 考虑进来;

auto exception : 扫描delay requirements 延迟要求

ICC II 能够为那些缺少delay值的Corner 通过扫描用户应用的 “explicit sink pin with delay” (明确的叶子引脚的延迟),例如,你仅对CornerA应用了delay value ICC II 能够依据你的value 将调整后的delay 应用到 Corner B和Corner C;

比例因数是由initial clock时 为所有Corner计算的时序决定的,是先于时钟树优化的;需要确保指定那个最critical的Corner的值 当然这个Corner是在initial clock时 使用过的,除此之外,你还可以通过设置primary Corner,来指定应用delay value的Corner;(cts.comile.primary_Corner)

你要怎样检查exception呢?

auto exception会自动保存到一个文件中, clock_auto_exception_*.tcl

报告 exception 包括自动生成的exception

report_clock_balance_points

#如果你设置了以下的App option 那么日志信息中会包含auto exception的内容

set_app_options -list {cts.common.verbose 1}

控制 CTS 的单元的选择

set cts_libcells [get_lib_cells \

"*/INVX*_LVT */BUFX*_LVT AO CG FF..."]

set_lib_cell_purpose -exclude cts [get_lib_cells]

set_lib_cell_purpose -include cts $cts_libcells

set_dont_touch $cts_libcells false

除了buffer /inverter之外 还需要指定逻辑等价单元(包括mux AND ICG ect) 方便在CCD时 对树上的单元进行sizing;如果设计为MV design 有always-on的需求 还需要 加入AO 单元;

时钟树中已经存在的单元

如果不知道那些单元要在 CTS 的时候使用,可以让ICC II 自己去判断,

set_lib_cell_purpose -include cts

derive_clock_cell_references -output cts_leq_set.tcl

#会生成一个文件 source 这个文件就好了

默认的时钟树综合目标

默认的目标skew和目标latency 对于每一个clock domain都是0ns ;

SDC 约束中的uncertainty以及 network latency 会被忽略;

可以为 不是没有时序紧张的 时钟放松 clock skew 的目标; 这会减少 buffer 的数量 功耗 以及运行时间;

指定network latency 目标帮助CTS之后的时序;

用户定义的时钟树综合目标

remove_clock_tree_options -all -target_skew -target_latency

set_clock_tree_options -target_skew 0.2 -Corner [all_corners]

#在未指定 Corner 的时候 set_clock_tree_options 所设置的target skew & latency 只会应用于当前的Corner 以及所有的mode;

set_clock_tree_options -target_latency 1.2 -clocks [get_clocks "CLK1 CLK2"]

# 如果指定时钟 那么仅会应用于当前mode, 否则 应用于所有的mode

report_clock_tree_options

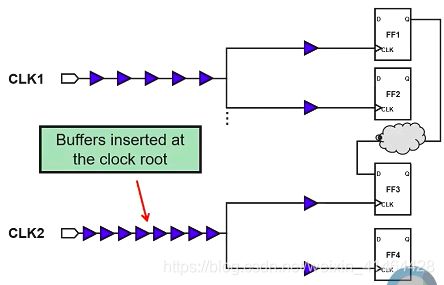

inter-clock skew balancing **时钟的skew平衡

除了为每个时钟指定target latencies ,用平衡 clock domain 来代替可能会更容易一点;

create_clock_balance_group -name grp1 -object [get_clocks "CLK1 CLK2"]

### 你可以让ICC II决定哪些 clock groups 需要被balance;

derive_clock_balance_constraints -slack_less_than -0.3

report_clock_balance_group

# 只有那些 跨时钟的路径 满足 -slack_less_than 条件的 才会被选择;

balance 发生在 clock_opt 阶段

对于CCD 来说 跨时钟的 balance 是非常重要的;

没有 inter-clock balance 的话 CCD 会尽力去满足时序 通过skewing individual sinks;造成更长的运行时间 会插入更多的buffer;

有 inter-clock balance 之后 CTS 会更多的在root 上插buffer,

summary: clock tree balancing setup

#define explicit sink & ignore pin ;

set_clock_balance_point

#specify target skew & latency

set_clock_tree_options

#control CTS cell selection

set_lib_cell_purpose -include cts $cts_cells

set_dont_touch $cts_cells

#OR let ICC II CREATE selection file

derive_clock_cell_reference -output cts_leq_set.tcl

#enable inter-clock balancing

create_clock_balance_group

#OR let ICC II identify

derive_clock_balance_constraints -slack_less_than -0.3

clock_opt

Pre-existing clock elements

移除或者保留 时钟树上预先存在的单元

remove 预先存在的buffer 会被移除;

预先存在的clock buffer/inverter 可能会对 CTS 的QoR产生负面的影响

默认情况下,CTS 会一处条预先存在的 clock buffer/inverters 使用更少的buffer 去创建平衡的时钟树;

cts.compile.remove_existing_clock_trees true (by default)

preserving 保留预先存在的elements

时钟树的Removal Behavior

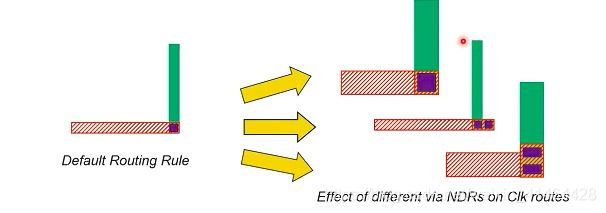

Non-Default routing rules(非默认的布线规则)

非默认的布线规则

ICC II 能够在布时钟线时使用非默认的布线规则, NDR rules

比如 双倍线宽 双倍间距 ,shielding (屏蔽)

NDR rules 经常被用来使时钟网络更严格, 确保时钟布线对于cross-talk (串扰) and electro-migration (EM 电迁移)的影响是更不敏感的

非默认的 via rule (通孔规则)

时钟线网的规则更严格之后 进一步经常需要100% 的通孔优化 去提高可靠性;

将普通的通孔 替换为 multiple-cut via array 或者 更大的 square or bar cuts

这仍然需要定义到 NDR rule中;

定义 NDR routing and via rule

create_routing_rule 2xS_2xW_CLK_RULE \

-widths {M1 0.11 M2 0.11 M3 0.14 ...}\

-spacing {M1 0.4 M2 0.4 M3 0.48 ...}\

-cuts {...VIA3 {Vrect 1}...}

# 使用-cuts option 你使用的是定义在 工艺文件中的 symbolic via name

# 这个简化了NDR 的定义 一个symbolic via 可以对应许多指定的via 和array

手动定义 NDRs 中使用的 vias

需要你指定 额外的 定义在techfile中的contactcode names

reate_routing_rule 2xS_2xW_CLK_RULE \

-widths {M1 0.11 M2 0.11 M3 0.14 ...}\

-spacing {M1 0.4 M2 0.4 M3 0.48 ...}\

-vias{... {VIA34_LV 1x1 NR} {VIA34_LH 1x2 R} {VIA34_LH 1x2 NR} ...}

应用非默认的布线规则

create_routing_rule 2xS_2xW_CLK_rule ...

set_clock_routing_rule -rule 2xS_2xW_CLK_rule \

-min_routing_layer M4 \

-max_routing_layer M5

## 对于底层金属来说 应用的是soft rule

## NDR 也会被应用到 M1-M3,尽管 时钟树会优先使用 M4/M5来布线 但他们仍然需要使用底层金属 连接到标准单元的pin 所以M1-M3 也是应用非默认布线规则 的;

set_clock_routing_rule

/ -nets

/-clocks

/**NONE**

优先级 1>2>3>4 越详细优先级越高

在root internal sink nets上应用不同的布线规则

set_clock_routing_rules \

-net_type sink

-rules 2X_rules

...

sink nets 部分绕线资源更紧张 因为一般使用更底层的 routing metal;

放松spacing 的要求

通过NDR promotion 预防时钟网络 crosstalk;

timing & DRC constraints

是否所有时钟的drivers & loads 是被指定了的

确保所有的时钟输入都有slew constraint 在CTS之后计算时钟delay用的

# 使用

report_port -verbose [get_ports *clk]

#来查看clock 端口的约束情况:

定义CTS专用的 DRC 值;

max_transition & max_capacitance 的设计规则 能够通过两种方式定义 : 库 和 SDC

ICC 会使用两者中最小的那个值;

#你可以指定自己的CTS 专用 的DRC 值:

set_max_transition -clock_path [all_clocks] 默认是0.5ns

set_max_capacitance -clock_path [all_clocks] 默认是0.6pf

# 设计规则能够选择的应用到 每个失踪 每个scenarios

set_max_transition 0.2 -clock_path \

-scenarios "S1 S2" \

[get_clocks SYS_CLK]

将SDC中的skew 从uncertainty 中移除;

SDC 的约束经常包括 uncertainty 而uncertainty 包含: skew jitter margin

为了避免在clock_opt 阶段 过于悲观的 时序分析,移除或者减小 uncertainty ;

set_clock_uncertainty -scenarios S1 -setup | -hold CLK1

# 可以为不同的额scenario 设置不同的值;

报告设置情况

# 报告时钟树的额max_tran /cap/reference /在所有的时钟和mode下

report_clock_settings

[-clock clocks]

[-type type]

# type can be configuration routing_rule reference spacing_rule all

#报告时钟树的 skew latency 目标

report_clock_tree_options

# 报告明确的balance points & group

report_clock_balance_points

report_clock_balance_groups

# 报告非默认的布线规则

report_clock_routing_rules