跨时钟域(Clock Domain Crossing,CDC)

本文参考:http://t.csdnimg.cn/VHga2

【数字IC基础】跨时钟域(CDC,Clock Domain Crossing)_ReRrain的博客-CSDN博客

同步设计:所有设计使用同一时钟源,频率相位可预知。

异步设计:设计中有两个或以上的时钟,且时钟之间是同频不同相或不同频的关系。

亚稳态:如果D在Tsu和Th时间内不断变化(非定值),导致触发器在触发沿时不知道应该输出高电平还是低电平,输出端处于不确定状态,这便是亚稳态,当输出端恢复稳定之后,这个输出值是随机的,与输入没有逻辑关系。常常出现在跨时钟域信号传输(时钟相移未知)、异步复位信号(任意时间到达寄存器)、异步信号采集等。

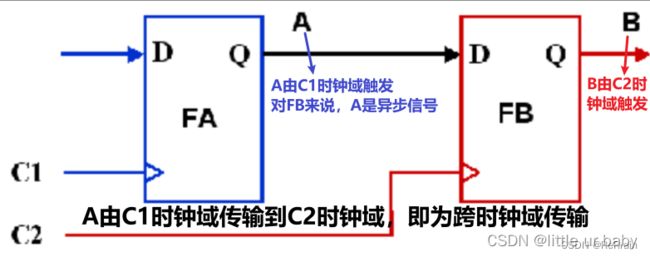

通俗来讲,一个时钟源就代表一个时钟域,跨时钟域就是把数据从一个时钟域传输到另一个时钟域。

跨时钟域的本质问题是:亚稳态。(还是建立时间、保持时间的问题),分为单比特亚稳态与多比特亚稳态。注意:组合逻辑才有竞争冒险,时序逻辑为亚稳态。

解决亚稳态问题的常用方法为用寄存器打拍,但是只能保证后续电路输出的稳定性,不能保证正确性。

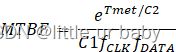

打拍通常打两拍,解释:引入一个MTBF(平均失效时间间隔),即触发器采样失败的时间间隔:

MTBF越大,亚稳态对电路产生的影响越小。文献指出,对于一个采样频率为200MHz的系统,不做同步MTBF=2.5us,一级同步MTBF=23年,二级同步MTBF=640年。一级同步不太稳定,二级同步够用,三级同步会增加面积且可能影响系统性能,没必要。所以常常打两拍来消除亚稳态。跨时钟域常见以下场景:

①多路扇出:如果一个时钟域A的信号同时输出到时钟域B去驱动多个触发器,由于经过不同路径,多路扇出的值不一定相同。(如一个使能信号使能后续多个模块)

解决方法:在时钟域B打两拍后再多路扇出。

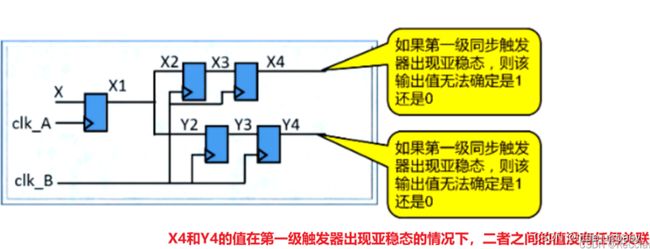

②数据丢失:信号长度太短,采样时钟频率太快,导致没踩到数据,或者漏采样。

解决方法:展宽信号。

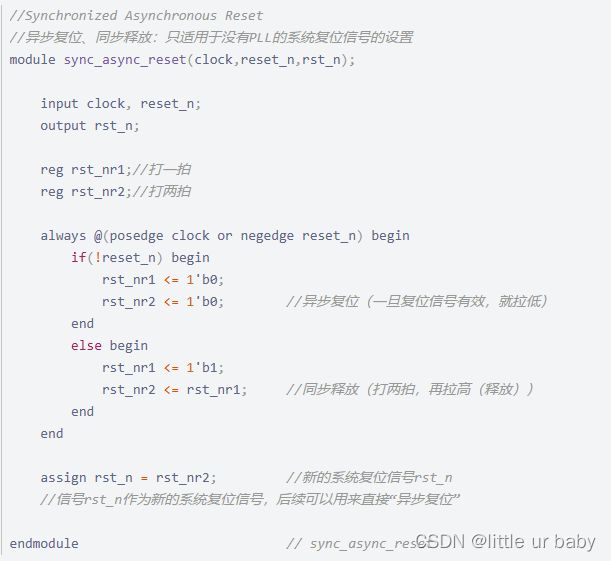

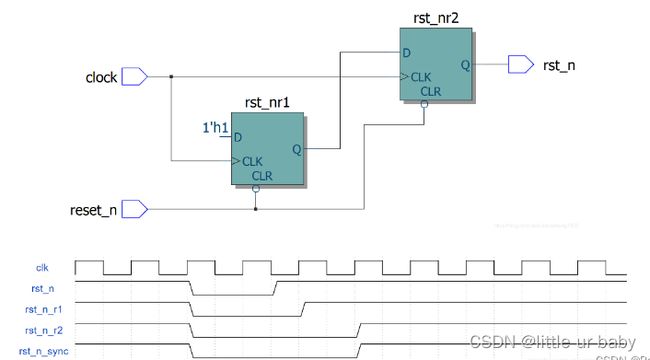

③异步复位:异步复位信号释放时不满足recovery time 和 removal time,产生亚稳态。

解决方法:异步复位同步释放,即通过寄存器改变释放的时间,同步处理。

①单bit亚稳态:用两级D触发器做同步处理。如果时钟域A发出的信号经过了组合逻辑电路再传输到时钟域B,那么需要先在组合逻辑后先接一级时钟域A的寄存器,再打两拍时钟域B的寄存器进行同步。

②多bit亚稳态:数据收敛,确保一组相关联的同步信号在经过不同的路径后可以在某一相同的时钟周期正确到达另一个时钟域。

单比特电平信号:用两级D触发器做同步处理

单比特脉冲信号:

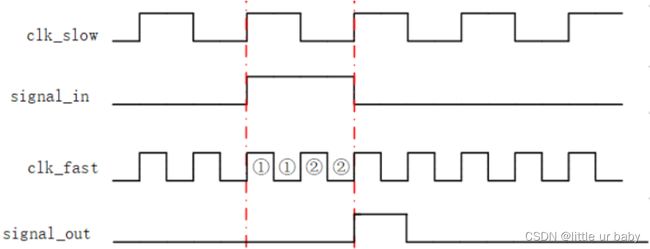

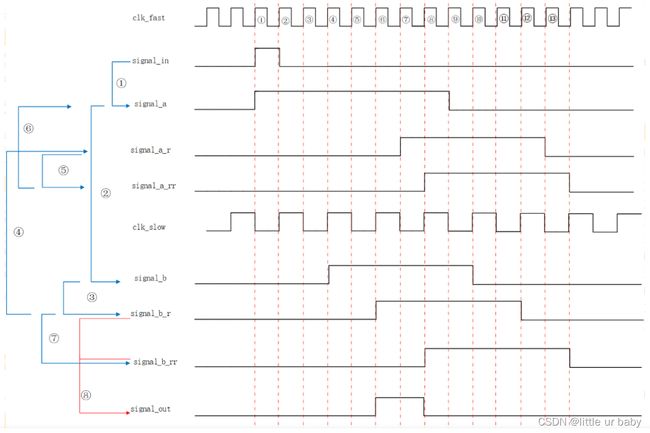

①从慢时钟域到快时钟域:打两拍(两级D触发器),再边沿检测

②从快时钟域到慢时钟域:先在快时钟域进行脉冲展宽,同步后再传输到慢时钟域进行边沿检测。

多比特信号:

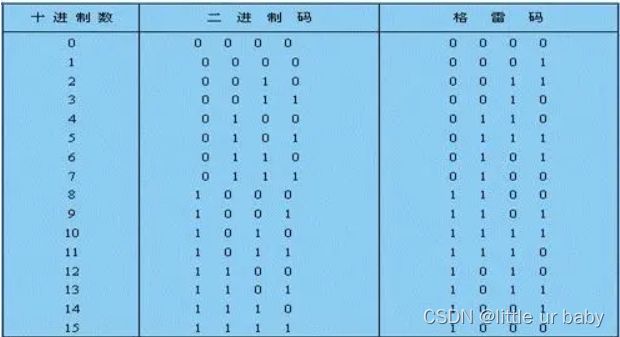

1.格雷码+双DFF(即打两拍):常用于异步FIFO中读写地址的跨时钟域传输。

如图,格雷码两个连续值仅相差一位,所以在FIFO读写地址的增减过程中,每次地址位只变化一位,本身出现亚稳态的几率就比二进制低了不少。此外,可以保证FIFO数据安全写入读出的标准。当然,应用格雷码时必须保证首尾只有1bit不同,即数据个数必须为2^n,否则首尾不满足只差1位。

二进制转格雷码一般通过组合逻辑实现,所以输出后要先加一级DFF,保证输出数据的稳定性。

2.握手协议:讲多比特数据的跨时钟传输问题转换成单个信号的跨时钟传输,即引入请求信号req和应答信号ack进行同步,只对req和ack进行同步。数据准备好了再发出req,就只有req可能有亚稳态问题,因为data已经稳定不变了。握手即req+ack。

3.DMUX(D触发器加二选一选通器):通过使能信号判断多比特data是否已经稳定,稳定则选通当前data;不稳定则选通之前的data。所以需要暂存前一时刻的data。