PCB知识补充

系列文章目录

文章目录

- 系列文章目录

- 参考文献

- PCB知识

-

- 互连线电阻

- 过孔/铜箔电流能力

-

- 铜箔载流能力

- 过孔载流能力

- 热设计

- 电磁兼容及部分要求

参考文献

[1]牛森,张敏娟,银子燕.高速PCB多板互联的电源完整性分析[J].单片机与嵌入式系统应用,2023,23(09).

[2]陈之秀,刘洋,张涵舒等.高频率高密度电力电子系统PCB的优化设计研究[J].电气传动,2023,53(01):

[3]凌林玉.试析PCB设计中的电磁兼容问题[J].长江信息通信,2023,36(02):

[4]付可心,曾敏华.一种提升PCB载流能力的设计方法[J].工业控制计算机,2023,36(06):

PCB知识

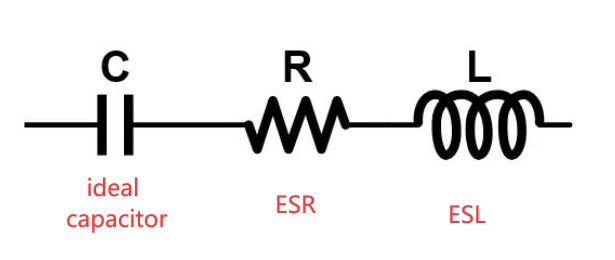

ESR:等效串联电阻(寄生电阻)(Equivalent Series Resistance)

ESL:等效串联电感(寄生电感)

常在大功率/高频中考虑

IR Drop:(V=I*R)压降,电源和地网络上电压的下降或者升高的现象,电路在直流电阻造成的压降。

常见的过压问题:

1.器件由于过压或者欠压而不能正常工作;

2.局部区域电流密度过大,引起此区域温度持续升高甚至烧毁;

3.I/O网络中的电阻过大,导致有用信号严重衰减;

copper covering area:敷铜区域

through-hole: 过孔

semiconductors:半导体

copper foil area:铜箔区域

parasitic:寄生的

互连线电阻

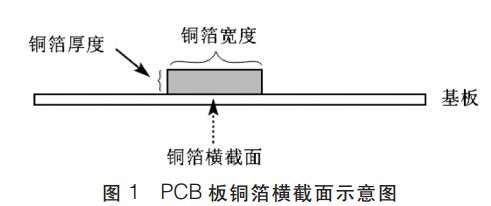

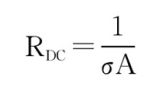

PCB上的互联体是铜导体,也有电阻,单位长度的直流电阻为:

σ表示电导率,A表示过流面积。铜的电导率为5.8×107 S/m(S:西门子),最后得出:0.269欧姆/米(10mil宽度)

1mil=0.0254mm

改变互连线线宽或者增加覆铜面积都可以有效减小走线的直流电阻。

过孔/铜箔电流能力

电流能力计算公式:

I为最大通流,单位为安培(A);

K是与环境相关的常量,分别为内层线和外层线,内层线的取值为0.024,外层线的取值为0.048;

T为通流路径上最大容许的温升,单位为℃;

A为通流路径的横截面积,单位是平方密耳(mil2)

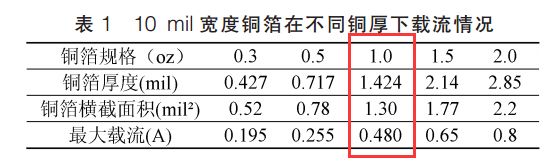

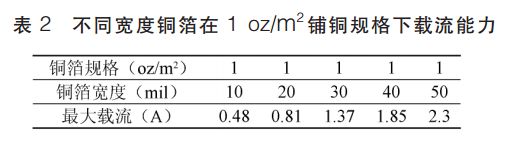

铜箔载流能力

所以这也是为什么铺铜的时候是按照最窄处计算的。

按照10mil的线宽,在内层布线,1oz的铜厚,计算可得大概在0.4A左右。

1oz=0.0356mm=1.2mil

可以看到10mil的情况下过电流也不是很大

可以通过加宽线宽的方式。

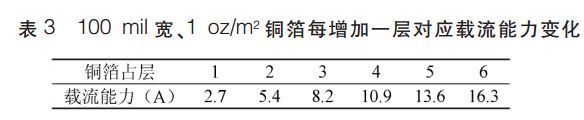

铜厚影响载流能力,还影响整板的阻抗匹配,所以可以通过增加层数的方式,增加铺铜层数

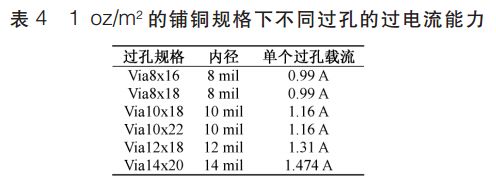

过孔载流能力

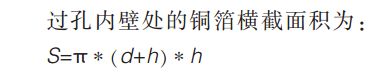

过孔的横截面与外径无关,铜厚主要是过孔内径铺在表面,一般铺1oz厚的,算出横截面后还是用上面的电流能力公式计算。

d 为孔径,h 为孔内壁的沉铜厚度,假设在过孔处控制沉铜规格为 1 oz/m2

10mil孔径情况下,温升10°,同流能力为1.16A,一般取1A。

过孔优化:(部分过孔电流过大)

1.增加过孔的数量,但要放置得当;

2.增大过孔的孔径,但会影响走线;

3.在大电流过孔靠近GND引脚处,增加回流过孔,共同分担电流;

4.删除非功能性过孔,可以让出更多的铺铜区域

在信号1GHz以上且需要过孔变层,过孔会产生ESR、ESL的问题,可通过降低PCB的厚度,在信号附近放置GND过孔优化。

热设计

过孔阵列中,过孔间距越小,单位热阻越小,越有利于散热,但一般看制造商允许多少吧

常见的PCB介质材料是环氧玻璃布基FR4,FR4的导热率只有0.29 W/(m·K),而铜的导热率为393 W/(m·K),因此电路板上的热量主要是依靠铜箔传递。发热元件最好放在铜箔中心,影响的面积大概是20mm*20mm。而在增加了过孔的情况下,散热情况大幅度提高。

热设计准则:

1.过孔间距尽可能的小;

2.过孔无填充时,过孔直径0.25 mm散热效果最佳;

3.当填充物的导热率小于60 W/(m·K)时,会有对应的最佳过孔直径,当导热率大于60 W/(m·K)时,直径越大越好;

4.仅通过铜箔进行散热时,散热铜箔面积小于10 cm2时,可以在节约面积的情况下有效散热。(不加过孔阵列)

电磁兼容及部分要求

电磁兼容(EMC):电子设备(系统)在所处电磁环境中能够正常、稳定的工作,并且自身工作不会对同一环境中的其他电子设备(系统)造成干扰。电磁兼容包含电磁抗扰(EMS)和电磁干扰(EMI)。

减少关键信号(尤其是电源信号)的回路面积是提升 PCB电磁兼容性最有效的方法,如:尽可能缩短地线与信号线间的距离,使二者间的距离等于 PCB 的层间距离。这样便可最大限度减小板上信号的回路面积,从而达到减小 PCB差模辐射,提高电磁抗扰能力。

PCB 时钟频率≥5MHZ 或者脉冲上升时间小于5ns 时,必须选用多层板。同时,为提升 PCB 的电磁兼容性,应优先选用基板材料相对介电常数较大的多层板。

避免电磁兼容问题:

1.电源、功率输出器等易发热元件远离关键电路,设置在 PCB 边缘区域或偏上方区域,以便更好散热;

2.敏感元件远离 CPU 时钟发生,在其周围的电源铜箔上蚀刻出马蹄形;

3.为了减小共模电流辐射,将所有连接器元件统一设置在 PCB 的一侧;

4.引线长度超过的噪声频率波长的 1/20产生天线效应,带来明显电磁干扰,缩短高速器件的走线长度,并尽量将其设置在远离连接器的地方。采用 I/O 驱动器与连接器相邻布置的方式,减少 I/O 信号的走线距离,以此耦合干扰信号;

5.对于动作电平差异大或者工作频率接近的元件,应增大元件的间距,避免工作中相互干扰。对于振荡器、时钟发生器等运行噪声较大的元件,可集中设置在远离逻辑电路部分的地方;

6.设置 EMI滤波器

串音:串音一般可以分为由于电磁场耦合引起的串音,或者由于公共阻抗耦合引起的串音。公共阻抗耦合引起的串音,是不同信号在共用相同返回路径时产生的,这种耦合常常在低频时起到较大的作用

地弹跳的内在原理。地弹跳一般是指在 PCB 系统运行时,某集成电路开关时,由于地线、集成电路的接地引线具有电感,引起器件内部的电位短暂下降,此时来自其他器件内的输出驱动信号是以外部系统作为参考的,参考电位的不一致会引起器件输入、输出电平的变化,从而引起信号稳定性的问题