【翻译】ModelSim指南 III (ModelSIM)(Verilog)(Digital Logic)

5

多库协作

简介

本课将练习使用多个库。通过使用第三方的库,使设计包含多个库。

本课先创建一个包含counter设计单元的资源库。然后,创建一个项目并编译测试台,链接包含counter的库,最后运行仿真。

本课用到的设计文件

范例是一个8位二进制递增计数器和相关的测试台。路径如下:

Verilog – <install_dir>/examples/tutorials/verilog/libraries/counter.v and tcounter.v

扩展阅读

用户手册章节—Design Libraries。

创建资源库

在创建资源库前,确认安装目录里的modelsim.ini文件的属性是“只读”的。这样就防止资源库和主文件modelsim.ini永久映射。

1. 为资源库创建一个目录。

创建一个名为resource_library的目录。拷贝counter.v到其。

2. 为测试台创建一个目录。

创建一个名为testbench的目录,用来存放测试台和项目文件。拷贝tcounter.v到其。

本课创建的2个文件夹用来模拟使用第三方资源库的情况。如前所述,稍后将链接第一个文件夹里的资源库。

3. 启动ModelsSim并切换文件夹至resource_library目录。

如果刚完成上课,ModelSim应该已经打开了,否则,启动ModelSim。

a) 选择File > Change Directory并切换到第一步创建的resource_library目录。

4. 创建资源库。

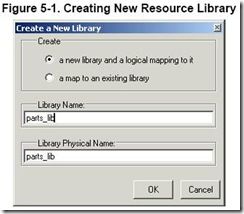

a) 选择File > New >Library。

b) 在库名栏输入parts_lib(图5-1)。

而Library Physical Name区将自动填充。

单击OK, ModelSim为这个库创建一个目录,在Library窗口列出来,并通过修改modelsim.ini文件来记录这个库。

5. 编译counter到资源库。

b) 从Library列表选择parts_lib库(图5-2)。

c) 双击counter.v编译。

d) 单击Done。

到此,一个包含编译好的counter设计单元的资源库完成。

6. 切换至testbench目录。

a) 选择File > Change Directory并切换至第二步创建的testbench目录。

创建项目

创建一个包含tcounter.v的项目。

1. 创建项目。

a) 选择File > New >Project。

b) 在Project Name栏输入counter。

c) 不要修改Project Location栏或Default Library Name栏。(缺省库名是work)

d) 确定“Copy Library Mappings”已选择。将使用缺省的modelsim.ini文件。

e) 单击OK。

2. 给项目添加测试台。

a) 单击Add Existing File 。

b) 单击Browse按钮并在“Select files to add to project”选择tcounter.v。

c) 单击Open。

d) 单击OK。

e) 单击Close以忽略“Add items to the Project”对话框。

在Project窗口列出tcounter.v文件。

3. 编译测试台。

a) 右击tcounter.v并选择Compile > Compile Selected。

链接资源库

接下来链接先前创建的parts_lib库。但先试试不链接就加在测试台,看看会怎样。

加载Verilog测试台

1. 加载一个缺乏资源库的的Verilog设计。

a) 在Library窗口,单击work库前的‘+’并双击test_counter。

在主窗口脚本报告一个警告(图5-4)。当看到类似“Warning: (vsim-3473)”的信息,可用verror命令查看更多细节。

b) 在VSIM提示符后输入verror 3473。

提示详细信息。

c) 输入quit –sim退出仿真。

链接资源库

当仿真时链接到资源库需要指定一个“search library”。

1. 在仿真时指定一个查找库。

b) 单击work库前的‘+’并选择test_counter。

c) 单击Libraries标签。

d) 单击Search Libraries栏附近的Add按钮并在先前创建的resource_library库里浏览parts_lib。

e) 单击OK。

对话框的Search Libraries栏列出parts_lib(图5-5)。

f) 单击OK。

成功加载设计。

本课小结

继续下一课之前,需要结束当前仿真并关闭项目。

1. 选择Simulate > End Simulation。单击Yes。

2. 选择Project窗口已激活。

选择File > Close。单击OK。