EDMA的组成及其作用简介

EDMA是什么?

答:EDMA(Enhanced Direct Memory Access)是一种增强型的直接内存访问技术,用于高效地实现数据传输和处理。它是在传统的DMA(Direct Memory Access)基础上进行改进和扩展的。DMA是一种用于数据传输的技术,可以绕过CPU,直接在内存和外设之间进行数据传输,提高系统的数据传输效率。传统的DMA通常具有一些限制,如只能进行简单的内存到外设或外设到内存的数据传输,无法支持多通道操作和链式传输等高级功能。

1.EDMA控制的组成

图1展示了EDMA的系统组成,EDMA包括EDMACC(EDMA通道控制)和EDMATC(EDMA传输控制)两部分,其中每个EDMACC包含多个EDMATC,数量差异因为不同的硬件型号而有所不同,另外不同型号的硬件拥有的EDMACC数量也有不同。例如:基于TI的AWR1843传感器雷达包含2个EDMA,其中每个EDMA控制器中包含4个EDMACC,另外每个EDMACC包含4个EDMATC。为了更直观的认识EDMA,在分别对EDMACC和EDMATC进行叙述。

注:图中EDMACCm中的m表示EDMACC的数量为m,EDMA_m_TCn中的m表示对应第m个EDMACC,n则表示每个EDMACC包含n个EDMATC。

1.1EDMACC(EDMA通道控制)

从图1中不难得知,大体上EDMACC主要包括DMA/QDMA channel logic、Event queues、PaRam、Transfer request submission、Completion detection和Completion and error interrupt logic五大模块组成,它们的主要作用分别为:

- DMA/QDMA channel logic:用于捕获外设事件,这些事件用于启动事件触发的传输,以及允许配置DMA/QDMA通道(队列映射,PaRAM条目映射)的寄存器。此外还包括用于启用或者禁用事件的不同触发器类型(手动、外部事件、链式和自动触发)的所有寄存器,并监视事件状态。

- Event queues:事件检测逻辑和传输请求提交逻辑之间的接口。

- PaRam:用于维护通道和重新加载或者更新参数集的参数集组成的列表。

- Transfer request submission:该模块根据提交给事件队列的触发事件处理PaRAM集,并向与事件队列关联的传输控制器提交传输请求(TR)。

- Completion detection:该模块用于检测EDMATC和(或)从外设的传输完成情况。传输的完成可以选择性地用于链式触发新的传输或断言(assert)中断。逻辑包括中断处理寄存器,用于启用或者禁用中断(发送到DSP),中断状态/清除寄存器。

- Completion and error interrupt logic:产生传输完成或者传输错误后的中断。

图2展示了EDMACC的系统组成框图。注意:图2中m表示EDMACC的数量,p表示支持的DMA通道数量,通常根据硬件不同各有差异,n表示EDMACC对应的EDMATC的数量。EDMACC包含两种通道类型,分别为DMA通道和QDMA通道。每个通道都与给定的事件队列、传输控制器和给定的PaRAM集相关联。DMA信道和QDMA信道的主要区别在于系统如何触发传输。触发事件是启动传输所必需的。对于DMA通道,触发事件可能是由于外部事件(external event)、手动写入事件集寄存器(Manual trigger)或链式事件(Chain trigger)。当对用户编程的触发字执行写操作时,QDMA通道自动触发。所有这些触发事件都在识别时记录到适当的寄存器中。

一旦识别出触发事件,事件类型及通道将在适当的EDMACC事件队列中排队。每个DMA/QDMA通道到事件队列是可编程的。每个队列深度为16,因此EDMACC中在同一时刻最多可以对16个事件进行排队(在单个队列上)。当事件队列空间可用时,映射到完整队列的其它挂起事件将排队。如果同时检测到不同通道上的事件,则基于固定优先级仲裁方案对事件进行排队,其中DMA通道的优先级高于QDMA通道。事件队列中的每个事件都按FIFO顺序处理。在到达队列的头部时,将读取与该通道关联的PaRAM以确定传输细节。TR提交逻辑评估TR的有效性,并负责向适当的EDMA3TC提交有效的传输请求(TR)。

1.2 EDMATC(EDMA传输通道)

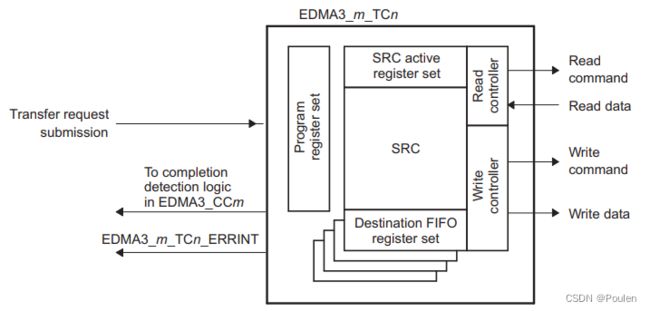

图3展示EDMATC的系统框图。EDMATC主要包括:

- DMA program register set:DMA程序寄存器集,用于存储从EDMA通道控制器(EDMACC)接收的传输请求。

- DMA source active register set:DMA源活动寄存器集,用于存储当前在读控制器中进行的DMA传输请求的信息。

- Destination FIFO register set:目的地(DST) FIFO寄存器集,用于存储当前在写控制器中正在进行的DMA传输请求的信息。

- Data FIFO:数据 FIFO 存在是为了暂时保存正在传输中的数据。

- Completion interface:完成接口在传输完成时向 EDMA3CC 发送完成代码,并生成中断和链接事件

当 EDMATC 空闲并接收到第一个传输请求时,传输请求被接收到 DMA 程序寄存器组中,然后立即转移到 DMA 源激活寄存器组和目的地 FIFO 寄存器组。源激活寄存器组跟踪传输的源端命令,目的地 FIFO 寄存器组跟踪传输的目的地端命令。第二个传输请求(如果来自于 EDMACC)被加载到 DMA 程序寄存器组,确保在活动传输(源激活寄存器组中的传输)完成时尽快启动。一旦当前的激活寄存器组用尽,传输请求将从 DMA 程序寄存器组加载到 DMA 源激活寄存器组,并相应地加载到目的地 FIFO 寄存器组的适当条目中。

读控制器根据命令分割和优化规则发出读取命令。只有在数据 FIFO 有可用空间用于读取数据时才会发出这些命令。发出的读取命令数量取决于 TR 传输大小。一旦数据 FIFO 中读取到足够的数据,使得写控制器可以根据命令分割和优化规则发出最佳大小的写入命令,写控制器就会开始发出写入命令。

2.EDMA传输类型

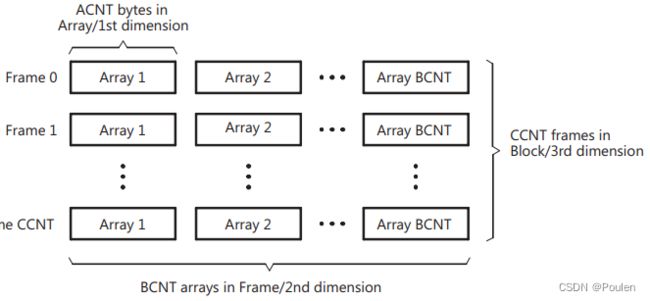

EDMA3传输始终以三个维度来定义(EDMA传输是按照这三个维度来完成的)。图4显示了EDMA传输使用的三个维度。这三个维度被定义为:

- 1st Dimension or Array (A):传输中的第一个维度包含ACNT个连续字节(通俗的理解是:第一维度的传输类似于传输一个一维数组,一维数组的大小为ACNT个字节,如果是int类型,长度则等于ACNT/4,因为int类型占用4个字节)。

- 2nd Dimension or Frame (B):传输的第二维包含BCNT个长度为ACNT的一维数组。第二维中的每个数组传输都是通过使用SRCBIDX或DSTBIDX编程的索引来分隔的。

- 3rd Dimension or Block (C): 传输的第三维包含CCNT个长度为BCNT大小为ACNT的数组,称为字节帧或者帧。第三维中的每个传输都是通过使用SRCCIDX或DSTCIDX编程的索引与前一个传输分隔开的。

请注意,索引的参考点取决于同步类型。在接收到触发/同步事件时传输的数据量由同步类型(OPT中的SYNCDIM位)控制。在三个维度中,只支持两种同步类型:A同步传输和AB同步传输。

2.1 A同步传输模式

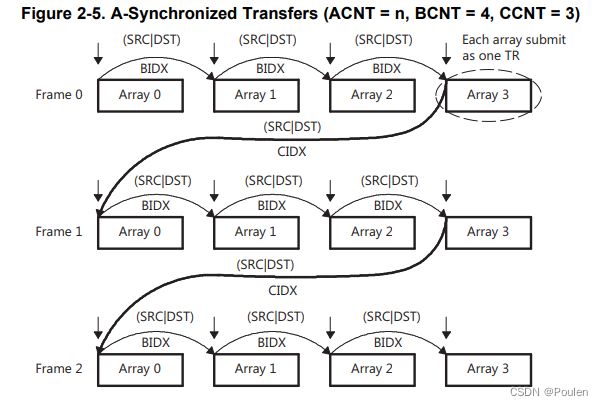

图2-5显示了一个3个(CCNT)帧、每帧4个(BCNT)数组、每个数组n(ACNT)字节的A-同步传输。在这个例子中,总共有12个同步事件(BCNT × CCNT),用尽了一个PaRAM设置。A同步传输的大致过程如下:

1.在A同步传输中,每个EDMA3同步事件都会启动ACNT字节的第一维传输,或者ACNT字节的一个数组的传输。换句话说,每个事件(图2-5中向下的黑色箭头表示一个触发事件)或TR数据包只传递一个数组的传输信息。因此,需要BCNT × CCNT个事件来完全服务一个PaRAM设置。数组总是由SRCBIDX和DSTBIDX分隔,如图2-5所示,其中数组N的起始地址等于数组N-1的起始地址加上源(SRC)或目的地(DST)BIDX。

2.帧(第三维度)之间始终由SRCCIDX和DSTCIDX分隔。对于A-异步传输,在当前Frame传输完成后,地址会通过将SRCCIDX/DSTCIDX添加到当前帧中最后一个数组的起始地址来进行更新。如图2-5中所示,SRCCIDX/DSTCIDX是Fream 0和Array 3的起始地址到Frame 1 和 Array 0的起始地址之间的差异。

- SRCBIDX索引:表示源数组的开始到下一个源数组的开始的字节地址偏移量。适用于A同步传输和AB同步传输。

- DSTBIDX索引:表示当前帧内目的地数组的开始到下一个目的数组的开始的字节地址偏移量。

- SRCBIDX和DSTBIDX的区别在于:

1.SRCBIDX(Source Address Index):指定了在源数据中进行传输时的地址增量。也就是说,它定义了在从源地址中传输数据时,每次传输后源地址应该增加多少。

2.DSTBIDX(Destination Address Index):类似于SRCBIDX,它指定了在目的地数据中进行传输时的地址增量。它定义了在将数据传输到目的地地址时,每次传输后目的地地址应该增加多少。

总的来说,SRCBIDX和DSTBIDX都是用来定义在数据传输期间源地址和目的地地址的增量,以便EDMA能够有效地处理数据传输。

- SRCCIDX:它提供了一个字节地址偏移量,从当前数组的开头(由SRC地址指向)到下一帧中第一个源数组的开头。

- DSTCIDX:它提供了一个字节地址偏移量,从当前数组的开头(由DST地址指向)到下一帧中第一个目标数组TR的开头

- SECCIDX和DSTCIDX的区别:

1.SRCCIDX是用于源地址修改的参数,它提供了一个字节地址偏移量,从当前数组的起始位置到下一帧中第一个源数组的起始位置的距离。这个参数通常用于指定源数据在多维数组中的位置,以便在数据传输中进行适当的偏移。

2.DSTCIDX则是用于目标地址修改的参数,它提供了一个字节地址偏移量,从当前数组的起始位置到下一帧中第一个目标数组的起始位置的距离。这个参数通常用于指定目标数据在多维数组中的位置,以便在数据传输中进行适当的偏移。

因此,SRCCIDX和DSTCIDX在EDMA中的区别在于它们分别用于源地址和目标地址的修改,以实现对数据在多维数组中位置的调整。

2.2 AB同步传输模式

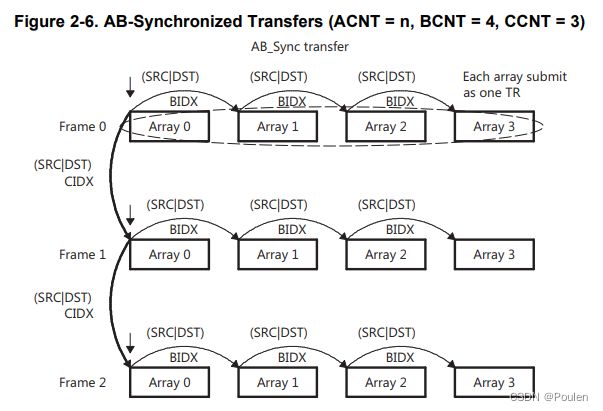

图2-6显示了3个(CCNT)帧、4个(BCNT)数组、每个数组包含n个(ACNT)字节的AB同步传输。在这个例子中,总共3个同步事件(CCNT)用完了一个PaRAM设置;也就是说,总共进行了3次传输,每次传输4个数组完成了传输。

在AB同步传输中,每个EDMA同步事件会启动2个维度或者一个帧的传输。换句话说,每个事件或TR数据包传递了BCNT个数组,每个数组包含ACNT个字节的信息。因此,需要CCNT个事件来完全处理一个PaRAM设置。请注意,对于AB同步传输,在提交帧的TR之后,地址更新是将SRCCIDX/DSTCIDX添加到帧中第一个数组的起始地址。这与A同步传输不同,A同步传输中地址的更新是通过将SRCCIDX/DSTCIDX添加到帧中最后一个数组的起始地址来实现。

3.Parameter RAM(PaRAM)

EDMA控制器是一种基于RAM的架构。DMA或QDMA通道的传输用到的信息(源/目的地址、计数、索引等)被编程到EDMACC内的参数RAM表中,称为PaRAM。PaRAM表被分成多个PaRAM sets(集)。每个PaRAM set包括八个4字节的PaRAM set条目(每个PaRAM set总共32字节),其中包括典型的DMA传输参数,如源地址、目的地址、传输计数、索引、选项等。

PaRAM结构支持灵活的ping-pong、循环缓冲、通道链接和自动重载(链接)。前n个PaRAM集直接映射到DMA通道(其中n是特定设备中EDMACC支持的DMA通道数)。其余的PaRAM集可以用于链接条目或与QDMA通道关联。此外,如果DMA通道未被使用,与未使用的DMA通道相关联的PaRAM集也可以用于链接条目或QDMA通道。

PaRAM的内容包括以下内容:

- 多个PaRAM集。

- 任何PaRAM条目都可以用于DMA、QDMA或链接集。

3.1 PaRAM set

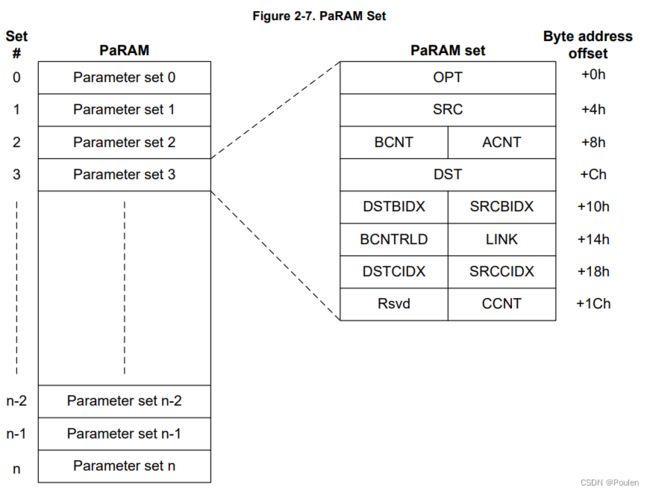

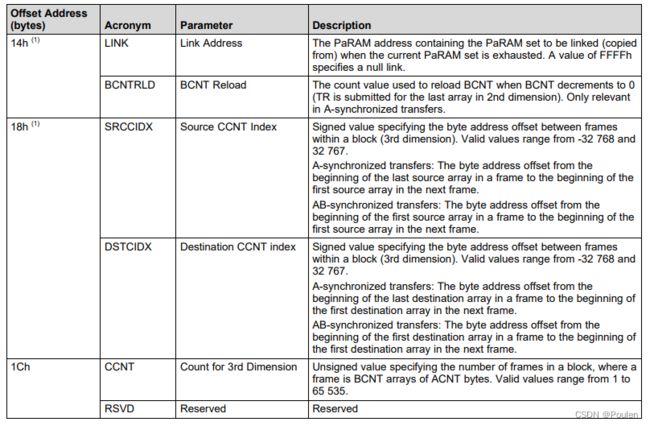

每个PaRAM的参数集都被组织成8个片段,每段32比特(bit),或可以说每个PaRAM set 的大小为32字节(byte),如图2-7所示,并在表2-2中描述。每个PaRAM集由16位和32位参数组成。

4.总结

本文分享的是博主学习EDMA的一些笔记,希望对大家有所帮助。EDMA对于DSP或者基于TI毫米波雷达架构进行编程开发的人员来说,把它学通透是相当重要的,本文主要参考TI的官方文档《KeyStone Architecture Enhanced Direct Memory Access (EDMA3) Controller User's Guide》,想要了解关于EDMA的更多细则,可以去阅读原文档。