计算机组织与结构知识点,【笔记】计算机组成与结构复习笔记

最后一门,来辣老弟!

Computer Organization & Architecture

ppt浏览

CH0 知识点总结

Overview

Computer system

CPU

CU

Parallel organization

CH1 Overview

结构Architecture偏逻辑,组成Organization偏实现

透明Transparency:对于一个存在的东西,从一个角度看就好像不存在一样.

功能Functions:结构中部分组件的操作

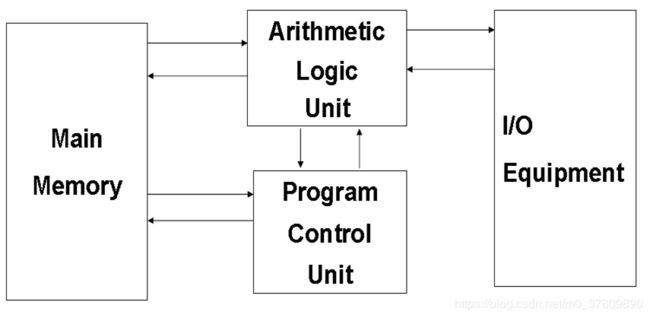

计算机包括:CPU(Central Processing Unit),主存Main Memory,System interconnection,IO

CPU包括:Registers, Arithmetic and logic unit(ALU), Control Unit(CU), Internal CPU interconnection

CU包括:Sequencing Logic, Control Unit Registers and Decoders, Control Memory.

CH2 Computer Evolution and Performance

ENIAC - first computer

冯诺依曼机的特性和结构

特性:

数据和程序存放在可读写的存储器中

存储器按位置寻址

指令顺序执行

寄存器包括:

MBR: Memory Buffer Register

MAR: Memory Address Register

IR: Instruction Register

IBR: Instruction Buffer Register

PC: Program Counter程序计数器

AC: Accumulator

MQ:Multiplier Quotient

摩尔定律:芯片上的晶体管数量每18个月翻一倍。

发展史:电子管计算机,晶体管计算机Transistor Computer,集成电路计算机Integrated Circuits Computer

经典分类:单片机chip microcomputer, 单板机single board computer,嵌入式计算机Embedded computer, 微型计算机Microcomputer, 服务器Server, 超级计算机SuperComputer

CH3 A Top-Level View Of Computer Function And Interconnection

KeyPoint

Interrupt and instruction cycles

Multiple interrupts

一个中断句柄被中断了。

System bus

连接计算机主要组件的总线。

data,address,control

Multiple bus hierarchy

Key elements of bus

自由总结

计算机的基础功能是执行程序

指令周期:处理一个指令的cpu时间

指令执行分为两步:fetch,execute(包括一步:数据处理)

中断

一种允许其他模块中断CPU执行序列的机制。

可以提高CPU利用率,便于处理紧急事件。

类别有程序,定时器,IO,硬件错误。

在一个指令周期之后才会检查中断。

总线

连接两个或多个组件的通信路径,通常打包。

同一时刻只能有一个部件发送信息,可以有多个部件接受信息。

系统总线system,外围总线peripheral,内部总线internal

数据总线:指令也是数据,数据总线宽=机器字长=主要寄存器长度

地址总线:决定内存的最大容量

多总线:防止长总线带来的延迟?

总线要素

类型:专用/复用

仲裁方法:分布式,集中式:

链式轮询chain polling:扩展性强;敏感易损坏

计数器定时轮询counter polling:灵活的优先级,故障不敏感;控制较复杂

分立请求separate request:优先级灵活,速度快;线太多,控制复杂

时序:(??)

Synchronous同步:容易实现;不灵活

Asynchronous异步:反应快;控制复杂;非互锁interlock,半互锁,全互锁

Half-Synchronous半同步:允许各种速度的模块和谐通信

Separate分离:避免总线空闲等待,用于大型机

宽度

数据总线宽度:系统性能

地址总线宽度:内存容量

带宽bandwidth:传输速率,B/s

传输类型

写复用

读复用

读改写

写后读

写(不复用)

读(不复用)

PCI:外围设备互连

CH4 Cache Memory

标识符约束

自由总结

数据存储方法:顺序,直接,随机,关联

存取时间Access Time:将数据取出的时间

内存周期时间Memory Cycle Time: 地址变化时间+数据取出时间

局部性原理Principle of locality of reference

CPU访问数据或指令时,访问的存储单元趋于一个较小的数据区域中

90/10规则:10%的代码执行90%的时间

时间局部性Temporal,空间局部性Spatial

Cache

少量,快速的存储。接近CPU的速度。

Cache的一个line和内存的一个block相等,C个line,M个block

命中率h = Nc/(Nc+Nm),总时间T = T1+(1-h)*T2

size

小:便宜;命中率低

大:命中率高;贵,门多访问慢,占CPU空间

1k-512k均可

映射函数

直接映射 direct mapping

i=j%m,

内存地址->Tag+Line+Word

简单,易实现

敲击thrashing,如果多次取不同块的同一地址

完全关联映射full associative mapping

tag完全标识内存块,检查每个line

内存地址 = Tag + Word

可以任意映射,灵活

需要并联比较电路,昂贵

组关联映射set associative mapping

分为许多个块,外部直接映射,内部完全关联映射

内存地址 = Tag + Set + Word

替换算法(非直接映射)

Least Recently Used(LRU):替换最远使用的

First In First Out(FIFO)

Least frequently Used(LFU):替换使用次数最少的

Random,和LRU效率相近

Optimized:替换最远到来的

Cache写

回写write back:被替换时写入内存

写直达wirte through:直接写入内存;

CH5 Internal Memory

KeyPoint

Differences between SRAM and DRAM?

Comparing EPROM and Flash memory!

What is SDRAM? what applications need it?

Parallel DRAM techniques

分类

RAM(Random Access Memory)

读写时间相同

直流电源DC Supplies保持数据

临时存储

动静态

DRAM(Dynamic RAM)

结构简单

需要刷新

低成本

慢

主存

SRAM(Static RAM)

通电后不用刷新

更贵

快

cache

使用寄存器

ROM(Read Only Memory)

只能写,不能读

PROM(Programmable ROM)

只能写入一次,需要特殊设备

灵活便利

Read Mostly Memory

Erasable Programmable ROM(EPROM),多次写入,紫外线,贵,20分钟写入

Electronically EPROM (EEPROM),任意时刻写入,更贵,密度低,写慢

Flash Memory,快速重新编程,逐块写入。U盘

模块组织

字长扩展

字数扩展

同时扩展

现代存储

Synchronous DRAM(SDRAM)

访问与外部时钟同步,CPU可以在内存取数据时做别的事

Double-data-rate SDRAM (DDR)

单个时钟周期可以发送两次数据(上升沿,下降沿)

Parallel DRAM

用于大型计算机

CH6 External Memory

KeyPoint

Organization of Disk System

Disk Performance Parameters

Common characteristics of RAID and different applications of different RAID levels

Types of optical memory

自由记录

类型

磁盘

硬盘/软盘

RAID(Redundant array of independent Disks,独立磁盘冗余阵列)

可移动硬盘

光学设备

CD-ROM

CD-Writable(WORM)

CD-R/W

DVD: Digital video disk

Magnetic Tape磁带

物理存储

tracks inter-track gap

sectors inter-sector gap

CAV(constant angular velocity,恒定角速度旋转),Multiple zoned recording

控制字段,间隔很多

磁头head:Fixed,每个track一个;Movable,每个side有一个机械臂

多面side磁盘,垂直叠加;track->cylinder,数据由cylinder划分

类型

Floppy Disk软盘,容量小,慢,便宜

Winchester Hard Disk,通用便宜大

磁盘系统的组织

Disks, Disk Driver, Disk Controller(电子集成驱动器IDE,SCSI)

性能

取决于:计算机系统,操作系统,输入输出机制,磁盘控制器硬件

存取时间Ta = Ts + 1/(2r) + b/(rN)

寻道时间seek time

旋转延迟rotational delay = 1/(2r)

传动时间transfer time = b/(rN)

标识符定义

r 磁盘旋转速率

b 传送字节数,最少一个sector,最多一个track

N 每个磁道的字节数

RAID,7个级别

RAID 0 (non-redundant),无冗余

RAID 1(mirrored),存两个,读一个

RAID 2,海明纠错,大量冗余

RAID 3,奇偶校验

RAID 4,写入惩罚?

5 循环分配

6 两种方法,循环分配

光驱动器

CD-ROM

CAV恒定角速度 CLV恒定线速度

寻址:粗调,设置速度,读取地址,细调

优点:便宜,大量生产,可移动,鲁棒

缺点:慢,只读,脆弱

WORM-CD 可以写一次

DVD -> Digital Versatile(而非Video) Disk

physical records, 由inter-record gaps分隔。

CH7 Input/Output

自由记录

简单分类:人类可读/机器可读/控制

ASCII: American Standard Code for Information Interchange,小写&0xdf编程大写

Programmed I/O

CPU issues commands: Control, Test, Read, Write

发送命令,等待;执行命令,设置位;

浪费时间

完全控制,类似于访问内存

Interrupt Driven I/O

中断分辨:多中断线/软件轮询/链式轮询/总线仲裁

DMA(Direct Memory Access),直接内存存取

CPU外部,总线上的附加模块,在没有CPU干预的情况下将数据传输到内存中

方式:

Block Transfer Mode,垄断模式

Cycle stealing mode,循环窃取

Transparent mode,分时交替使用

步骤

CPU告诉DMA信息,然后去干别的事情

DMA进行数据传输

传输完成后发送中断

配置

单总线分离DMA:IO到DMA,DMA到memory,cpu挂起两次

单总线集成DMA:cpu挂起一次

分离IO总线:COU挂起一次

I/O 通道

步骤与DMA类似

CH9 Computer Arithmetic

补码:取反加一

好处:0只有一个表示,算术更简单,取反更容易

扩展规则:向左扩展符号位

溢出判断:同号相加,符号改变

IEEE754标准

第1位符号,后面8位指数,后面23位底数.

CH10 Instruction Sets: Characteristics and Functions

MMX——MultiMedia eXtension

原来这个东西上课讲过啊。。。

punpcklbw 解包

packuswb 打包

SSE——Stream SIMD Extension

CH11 Instruction Sets: Addressing Modes and Formats

立即数

直接

间接

寄存器

寄存器间接

偏移

栈

隐含

CH12 CPU Structure and Function

寄存器分类

用户可见

控制状态

指令周期

Fetch instruction 取指

Decode instruction 译码

Calculate operands address

Fetch operands

Execute instructions

Write operand

标识符约定

n 指令数量

k 阶段数

τ \tauτ 最长阶段的执行时间

性能评价

加速比SpeedUp: s k = n ∗ k / ( k + n − 1 ) s_k = n*k/(k+n-1)sk=n∗k/(k+n−1)

吞吐量ThroughPut: T p = n / ( k + n − 1 ) / τ T_p = n/(k+n-1)/\tauTp=n/(k+n−1)/τ

条件转移的处理

多指令流

预取分支目标

循环缓冲

分支预测

延迟分支

spatio-temporal diagram

CH13 Reduced Instruction Set Computers

精简指令集计算机(RISC)

CISC与RISC

CISC

简化编译器,程序更小

RISC

编译器优化更有效,更好的响应中断,有效利用流水线,指令简单执行效率高。

图染色算法

找到哪些变量可以放在寄存器

寄存器窗口

Parameter registers 参数

Local registers 局部变量iang

Temporary registers 参数调用,返回值

CH14 Instruction Level Parallelism and Superscalar Processors