Intel® 64 and IA-32 Architectures Software Developer's Manual:Vol 3 Section 10

第十章

高级可编程中断处理器(APIC)

高级可编程中断处理器(参考以下章节的本地APIC)在IA-32的Pentium处理器上被引入(参照22.27节,高级可编程中断处理器),同时包含在P6家族,Pentium 4,Intel 志强处理器和其他较新的Intel 64和IA-32处理器家族中(参照10.4.2章节,本地APIC的存在)。本地APIC为处理器提供两项主要功能:

- 接收来自处理器中断引脚、内部源、外部I/O APIC(或者其他外部中断处理器)的中断。发送中断到处理器内核去处理

- 在多处理器系统(MP)中,把核间中断(IPI)消息发送至或者接收从其他逻辑处理器通过系统总线。IPI消息被分配至系统中处理器间的中断或者执行整个系统的功能(例如,启动处理器或者在一组处理器间分配工作)。

外部的I/O APIC是Intel系统芯片组的一部分。它的主要作用是接收来自系统外部和它相关I/O的中断事件然后作为中断消息传达到本地APIC。在MP系统中,I/O APIC也提供了一个机制去把外部中断通过系统总线分配至可选处理器或者处理器组的本地APIC。

这一章描述了本地APIC和它的编程接口。同时也总揽了本地APIC和I/O APIC之间的接口。获取关于I/O APIC更多信息请联系Intel。

当一个本地APIC发送一个中断到它处理器核心去处理时,处理器使用中断或者异常处理机制,在第6章有描述,中断和异常处理。参照6.1节,中断和异常总揽,获取中断和异常处理的介绍。

10.1 本地和I/O APIC 总揽

每一个本地APIC包含一套APIC寄存器(参照表10-1)集合和控制中断分发至处理器核心、IPI消息生成的相关硬件。而APIC寄存器被内存映射,并且可以使用MOV指令进行读写。

本地APIC可以通过以下源接收中断:

- 本地连接的I/O设备

这些中断产生于由一个直接连接到处理器本地中断引脚(LINT0和LINT1)的I/O设备发起的边沿或水平信号。该I/O设备可能也连接到一个8259类型中断控制器,而该控制器反过来再通过一个本地中断引脚连接到处理器。- 外部连接的I/O设备

这些中断产生于由一个连接到I/O APIC中断输入引脚的I/O设备发起的边沿或水平信号。中断会被当做I/O中断消息从I/O APIC发送到一个或更多的处理器。- 核间中断(IPI)

一个Intel 64或者IA-32处理器可以通过系统总线使用IPI机制去中断另一个或者一组处理器。IPI也被用于软中断、中断转发或者抢占式调度。- APIC定时器生成中断

当可编程的APIC定时器到期时,定时器可以被编程去发送一个本地中断给它相关的处理器(参照10.5.4,APIC定时器)。- 性能监视计数器中断

当一个性能监视计数器溢出时,P6家族,Pentium 4,和Intel至强处理器提供了发送一个中断到相关处理器的能力(参照18.15.5.8节,当溢出时生成一个中断)。- 热传感器中断

当内部热传感器失效时,Pentium 4和Intel至强处理器提供了发送一个中断给自己的能力(参照14.7.2,热监视器)。- APIC内部错误中断

当一个错误条件在本地APIC内部被触发(例如尝试访问未实现的寄存器),APIC可以编程去发送一个中断给相关的处理器(参照10.5.3节,错误处理)。

这些中断源:处理器LINT0和LINT1引脚,APIC 定时器,性能监视计数器,热传感器,内部APIC 错误检测器都被称为本地中断源。在接收到一个来自本地中断源的信号,本地APIC分发该中断到处理器核心,而这是使用一个被设置好的中断分发协议,通过被称为本地向量表或者LVT(参照10.5.1,本地向量表)的一组APIC寄存器完成的。本地向量表中的一项对应于一个本地中断源,而这允许一个指定的中断分发协议设置于每个源。例如,LINT1引脚被用作NMI引脚,本地向量表里的LINT1项被设置成用向量号2(NMI 中断)分发一个中断给处理器核心。

本地APIC处理来自其他两个中断源(外部连接的I/O设备和IPI)的中断是通过它的IPI消息处理机制。

一个处理器可以通过给它的本地APIC上的中断命令寄存器(ICR)编程来生成IPI(参照10.6.1章, 中断命令寄存器(ICR))。写ICR的行为可以触发一个IPI消息并且派发到系统总线(对于奔腾4和Intel至强处理器)或者APIC总线(对于奔腾和P6家族处理器)。参照10.2节,系统总线VSAPIC总线。

IPI可以被发送给系统中其他的处理器或者发起者处理器(自中断)。当目标处理器接到一个IPI中断后,它的本地APIC自动处理该消息(使用例如向量号和触发模式的信息)。参照10.6节,派发核间中断,详细说明本地APIC的IPI消息传递和处理机制。

本地APIC同时也可以接收通过I/O APIC连接的外部设备的中断(参照图10-1)。I/O APIC负责接收由系统硬件和I/O设备生成的中断,并且把它们以中断消息的形式发给本地APIC。

[图10-1,在单核系统本地APIC和I/O APIC的关系]

I/O APIC上的一个特定引脚可以被编程生成一个特定的中断向量,当assert时。I/O APIC也有一个“虚拟线模式”,该模式允许自己与一块标准的8259A类型外部中断控制器通讯。记住,本地APIC可以被关闭(参照10.4.3节,打开或关闭本地APIC)。这就允许了相应的处理器核心能够直接接收来自一个8259A中断控制器的中断。

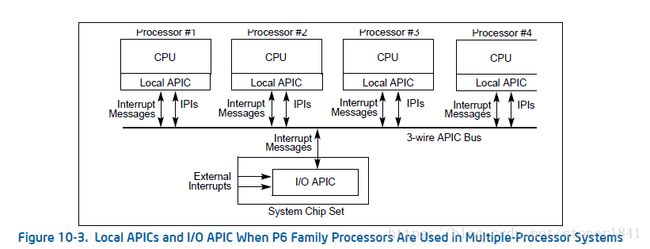

本地APIC和I/O APIC被设计用于多核系统(参照图10-2和10-3)。每个本地APIC处理来自I/O APIC的中断,来自系统总线上处理器的IPI,和来自自己生成的中断。中断也可以通过本地中断引脚分发给单独的处理器;然而,这个机制在多核系统上并没有广泛使用。

[图10-2,用于多核系统Intel至强处理器的本地APIC和I/O APIC]

[图10-3,用于多核系统P6家族处理器的本地APIC和I/O APIC]

IPI机制通常被用在多核系统中去发送固定中断(指定了中断向量号的中断)和给系统总线上的处理器发送特定中断。例如,一个本地APIC可以使用一个IPI去把一个固定中断发给另一个处理器来寻求服务。特定IPI(包括NMI、INIT、SMI和SIPI IPI)允许一个或多个总线上的处理器去执行全系统启动,以及控制功能。

下面章节关注本地APIC并且它已经实现于奔腾4,Intel至强,P6家族处理器。在以下章节中,术语“本地APIC”和“I/O APIC”就指的是用在P6处理器家族的本地和I/O APIC,用在P4和至强处理器的本地和I/O xAPIC(参照10.3节,Intel 82489DX 外部 APIC,APIC,xAPIC)。

10.2 系统总线 VS. APIC总线

对于P6家族和奔腾处理器,I/O APIC和本地APIC通过3位APIC内部总线通讯(参照图10-3)。本地APIC也使用该APIC总线发送和接收IPI。该APIC总线和它上面的消息对于软件是不可见的,并且没有归类到体系结构中去。

从奔腾4和至强处理器开始,I/O APIC和本地APIC(使用xAPIC架构)的通讯通过系统总线(参照图10-2)。I/O APIC给系统总线上的处理器发送中断请求是通过桥接硬件完成的,而它是Intel芯片组的一部分。该桥接硬件生成要路由给本地APIC的中断消息。在本地APIC之间的IPI是可以直接在系统总线上传送的。

10.3 Intel 82489DX 外部 APIC, APIC, xAPIC

P6家族和奔腾处理器中的本地APIC是Intel 82489DX 外部 APIC的架构子集。参照 17.26.1,本地APIC与82489DX之间的软件可见差异。

用在奔腾4和Intel至强处理器(称为xAPIC架构)的APIC架构是用在P6家族处理器APIC架构的扩展。APIC和xAPIC架构的主要 差异是,在xAPIC架构中本地APIC和I/O APIC通过系统总线通讯,而APIC架构中他们通讯是靠APIC总线(参照10.2,系统总线 VS. APIC总线)。同时,一些APIC架构的特性也被扩展或者修改在xAPIC架构之中。这些扩展和修改写在下面章节的注意事项当中。

10.4 本地 APIC

以下章节描述了本地APIC的架构和怎么检测它,识别它,查看它的状态。怎样给本地APIC编程的描述在10.5.1节,本地向量表,和10.6.1节,中断命令寄存器。

10.4.1 本地 APIC 结构图

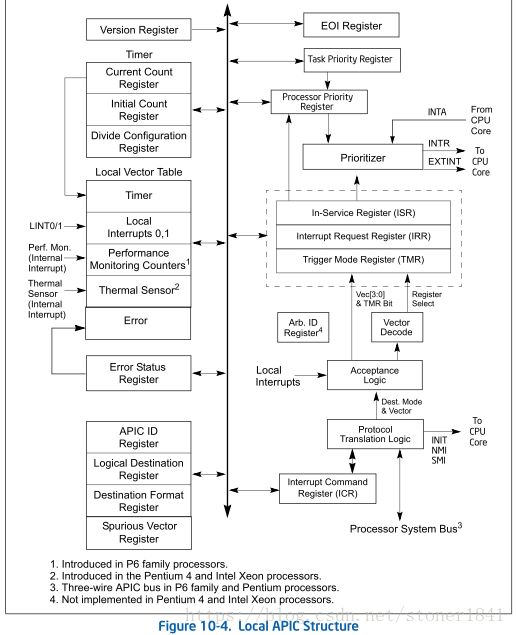

图10-4给出了一张本地 APIC的功能结构图。可以通过读写它的寄存器实现本地APIC的软件交互。APIC寄存器被映射到了物理内存起始地址0xFEE00000的4K区域中。对于正确的APIC操作,内存映射地址必须指定为强不可缓存。参照10.3节,缓存访问模式。

在多核系统配置中,Intel 64或者IA-32的APIC寄存器在系统总线上最初被映射成同样的4K区域。软件可以选择去更改初始的不同4K区域给所有的本地APIC,或者把每一个本地APIC的寄存器映射到它自己的4K区域。参照10.4.5节,重定位本地APIC寄存器,描述了如何重定位APIC寄存器的基址。

对于P6家族,奔腾4,和Intel至强处理器,APIC处理所有4K APIC内部寄存器地址的内存访问,并且不会产生额外的总线周期。对于有片上APIC的奔腾处理器,总线周期是当访问APIC寄存器空间时被产生。因此,对于要运行在奔腾处理器上的软件,系统软件不应该直接映射APIC寄存器到常规系统内存。如果这么做,可能会导致一个#UD异常或者不可预期的行为。

图10-4, 本地APIC结构

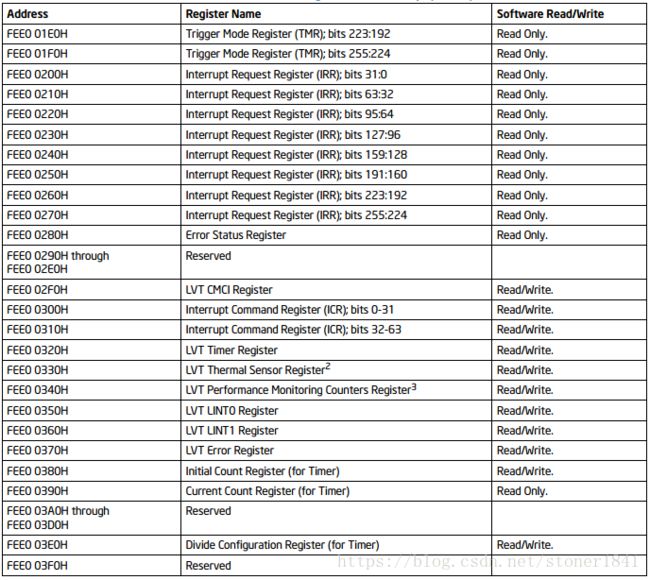

表10-1描述了APIC寄存器怎样被映射进4K的寄存器空间。寄存器有32位,64位或者256位宽度;所有的均128位对齐。所有32位寄存器应当使用128位对齐的32位load和store进行访问。一些处理器可能支持小于32位的load或者store到部分APIC寄存器。这个只是特定模式的行为,并不能保证在所有处理器上都工作。大宽度寄存器(64位或者256位)必须使用多个load或者store进行访问,而每一次访问必须128位对齐。

表10-1中的本地APIC寄存器并不是MSR寄存器。与本地APIC编程相关的MSR寄存器只有IA32_APIC_BASE_MSR(参照10.4.3节,打开或者关闭本地APIC)。

表10-1,本地APIC寄存器地址映射

注意事项:

1. 奔腾4和Intel至强处理器不支持;

2. 奔腾4和Intel至强处理器引入。APIC寄存器和它相关的功能独立实现,并且可能不在以后的IA-32或者Intel 64位处理器上;

3. 奔腾Pro处理器引入。APIC寄存器和它相关的功能独立实现,并且可能不在以后的IA-32或者Intel 64位处理器上。

10.4.2 本地 APIC 的打开

从P6家族处理器开始,片上本地APIC的打开和关闭可以被CPUID指令检测到。当CPUID指令以源操作数EAX=1执行后,返回的EDX第9位表示是打开(1)或者关闭(0)。

10.4.3 本地 APIC 的启动或者停止

本地APIC可以用以下两种方式被启动或者停止:

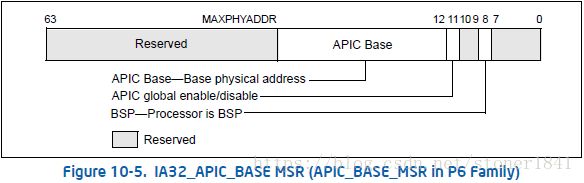

1. 使用IA32_APIC_BASE MSR(MSR地址0x1B,参照图10-5)中的全局APIC打开/关闭标记:

- 当 IA32_APIC_BASE[11] = 0时,处理器从功能上等同于没有片上APIC的IA-32处理器。CPUID的APIC(参照10.4.2,本地 APIC 的打开)特性位也被置成了0。

- 当 IA32_APIC_BASE[11] = 0时,基于3位总线APIC的处理器APIC通常不能重新启动,除非系统冷启动。这3位总线将丢弃可能有必要完成重新启动的仲裁。某一APIC的功能可能被打开(例如:性能和热检测的中断生成)。

- 对于使用前端总线(FSB)分发中断的处理器,软件可以通过设置和重置IA32_APIC_BASE[11]来关闭或者打开APIC。一次硬件重置并不需要重新启动APIC功能。

- 当IA32_APIC_BASE[11]被置0后,最先对APIC的初始化可能失效并且APIC可能返回到10.4.7.1节描述的状态,上电或者重置之后的本地APIC状态。

2. 使用APIC软件打开或者关闭在伪中断向量寄存器中的标记(参照图10-23):

- 如果IA32_APIC_BASE[1]为1,软件可以通过清除在伪中断向量寄存器(参照图10-23)中的APIC软件启动/关闭标志临时停止本地APIC。当在软件停止态下的本地APIC的状态描述在10.4.7.2章节,软件停止后的本地APIC状态

- 当本地APIC在软件停止状态时,可以通过设置APIC软件启动/停止标志为1来重新启动

对于奔腾处理器,APICEN引脚(与PICD1引脚共用)在上电或者重置停止本地APIC时被用到。

请记住,LVT里每一项都有一个标记位,该标记被用于禁止中断被分发到所选本地中断源的处理器上(LINT0和LINT1引脚,APIC计时器,性能监视计时器,热传感器,内部APIC错误检测器)。

10.4.4 本地 APIC 状态和基址

本地APIC的状态和基址保存在IA32_APIC_BASE的MSR(参照图10-5)。MSR位的功能描述见下:

- BSP 位, 第8位 ——表明该处理器是否为引导处理器(BSP)。参照 8.4节,多处理器(MP)初始化。随着上电或者重置,被选的BSP该标记会被置为1,同时其他的处理器(AP)该标记被置为0

- APIC 全局使能标记, 第11位 ——启动或停止本地APIC(参照10.4.3节,启动或停止本地APIC)。这个标记在奔腾4,Intel志强和P6家族处理器上是可用的,但是并不能保证在以后的Intel 64或者IA-32处理器上还是在这个位置。

- APIC基址,第12位至35位 ——指定了APIC寄存器的基址。这24位拼接上低端12位的扩展后组成基址。自动页对齐。随着上电或者重置,基址被设为FEE0 0000H。

- 第0到7位,第9和10位,第36(MAXPHYADDR)到63位为保留位

图10-5 IA32_APIC_BASE MSR(P6家族的APIC_BASE_MSR)

10.4.5 重定位本地APIC寄存器

奔腾4,Intel志强,P6家族处理器允许APIC寄存器的起始地址从FEE0 0000H重定位到其他的物理地址,这个通过修改IA32_APIC_BASE MSR的24位基址地址位即可。APIC架构的这个扩展解决了在内存映射时的冲突问题,它允许MP系统中的单个处理器能够映射他们的APIC寄存器到屋里内存上的不同位置。

10.4.6 本地APIC ID

上电以后,系统硬件分配一个唯一的APIC ID给系统总线(对于奔腾4和Intel志强处理器)或者APIC 总线(对于P6家族和奔腾处理器)上的每一个APIC。硬件分配APIC ID是基于系统拓扑和包括了插口位置和簇信息的解码内容(参照图8-2)。

在MP系统中,本地APIC ID也被BIOS和操作系统用作处理器ID。一些处理器允许软件修改APIC ID。然而,修改APIC ID软件的能力是由处理器模式规定的。因此,系统软件应该避免写本地APIC ID寄存器。EBX寄存器的第24到31位的值(当执行CPUID EAX[1])总是为APIC ID的初值(由平台初始化)。即使软件改变了本地APICID寄存器该值也是正确的,

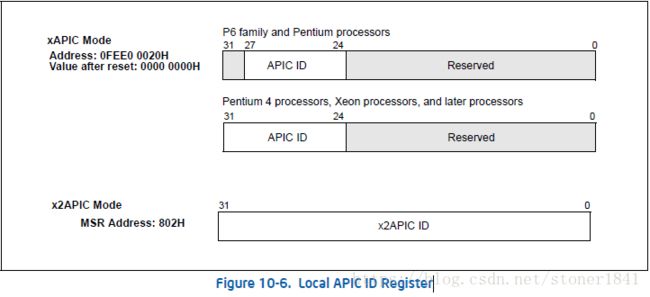

处理器收到硬件分配的APIC ID(或初始APIC ID)是通过A11#引脚,A12#引脚,BR0#到BR3#引脚(对于奔腾4,Intel至强和P6家族处理器),BE0#到BE3#引脚(对于奔腾处理器)。由这些引脚组成的APIC ID被存在本地APIC ID寄存器的APIC ID域(参照图10-6),同时被用于处理器的初始APIC ID。

图10-6 本地APIC ID寄存器

对于P6家族和奔腾处理器,本地APIC ID寄存器中APIC ID域一共4位。从0H到EH编码可以唯一标识连接到APIC总线的15个处理器。对于奔4和Intel至强处理器,xAPIC规范扩展到了8位。这可以标识系统中的255个处理器。

10.4.7 本地APIC 状态

以下章节描述了本地APIC的状态和寄存器,场景有:上电或者重置之后,本地APIC被软件设为停止,一次INIT重置,一次INIT-deassert消息。

x2APIC将引入32位ID;参照10.12节。

10.4.7.1 上电或重置之后的本地APIC 状态

随着上电或者 重置处理器,本地APIC的状态和寄存器如下:

- 以下寄存器被重置为全0:

- IRR,ISR,TMR,ICR,LDR和TPR

- 计时器初始计数和当前计数寄存器

- 划分配置寄存器

- DFR寄存器被重置为全1

- LVT寄存器被重置为0,标记位为1

- 本地APIC版本寄存器不受影响

- 本地APIC ID寄存器被设置上唯一APIC ID。(奔腾和P6家族处理器)。Arb ID寄存器也被设置为APIC ID寄存器的值。

- 伪中断向量寄存器被初始化成000000FFH。通过设置第8位成0,软件可以停止本地APIC。

- 如果是单核心处理器或者多核中的BSP(参照8.4.1节,BSP和AP处理器);本地APIC将正常地响应INIT和NMI消息,INIT#信号和STPCLK#信号。如果处理器是多核系统并且是AP,本地APIC也将响应,这点和BSP一样。此外,还能响应SIPI消息。对于P6家族处理器,AP不会响应STPCLK#信号。

10.4.7.2 被停止之后的本地APIC 状态

当伪中断向量寄存器中的APIC软件启动或停止标记被显示清除(不同于在上电或者重置期间清除),本地APIC被临时停止(参照10.4.3节,启动或停止本地APIC)。当处于软件停止状态下,操作和本地APIC的响应如下:

- 本地APIC正常响应INIT、NMI、SMI、SIPI消息

- 等待IRR和ISR寄存器的中断被拿到,并且请求标记或者被CPU处理

- 本地APIC依然可以发出IPI。如果不希望通过IPI机制发送中断,软件有责任去避免通过该机制和ICR寄存器发出IPI

- 当本地APIC停止,本地APIC进入软件停止态之前,正在进行中的中断接收或者IPI广播会被完成

- 所有LVT项的标记位被置。尝试重置这些标记位被忽略

- (对于奔腾和P6家族处理器)本地APIC继续监听所有的总线消息以便于保持Arb ID同步于其他

10.4.7.3 INIT重置(等待SIPI状态)之后本地APIC 状态

处理器的一次INIT重置可被初始为两种方式:

- 通过使能处理器的INIT#引脚

- 通过给该处理器发送一个INIT IPI(一次投递模式的IPI设给INIT)

在通过以上一种机制接收到INIT,处理器响应开始初始化处理器核心和本地APIC。随着INIT重置本地APIC的状态和它上电或者重置之后一样,而APIC ID和Arb ID寄存器不受影响。这个状态也被称为等待SIPI状态(也可以参照8.2节,多核系统初始化协议的要求和限制)

10.4.7.4 在接收到一个INIT-deassert IPI之后本地APIC 状态

只有奔腾和P6家族处理器支持INIT-deassert IPI。一个INIT-deassert IPI并不影响APIC的状态,除了用APIC ID寄存器填充Arb ID寄存器。

10.4.8 在接收到一个INIT-deassert IPI之后本地APIC 状态

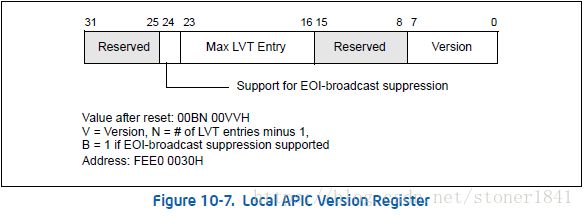

本地APIC包含一个硬件直连的版本寄存器。软件可以使用该寄存器去识别APIC版本(参照图10-7)。此外,寄存器根据规范规定了本地向量表(LVT)项的个数。

本地APIC 版本寄存器的域如下:

- Version 本地APIC的版本号:

- 0XH 82489DX 不连续 APIC

- 10H - 15H 集成APIC

- 其他值保留

- Max LVT Entry

- LVT项个数减1。对于奔腾4和Intel志强处理器(有6个LVT项),Max LVT域的值为5;对于P6家族处理器(有5个LVT项),这个值为4;对于奔腾处理器(有4个LVT项),这个值为3。对基于Intel微码Nehalem处理器和之前的(有7个LVT项),该值为6。

- 抑制EOI广播

- 表明软件是否可以通过设置伪中断向量寄存器的第12位来抑制EOI消息广播;参照10.8.5节和10.9节

图10-7 本地APIC 版本寄存器

10.5 处理本地中断

以下章节讲解了在本地APIC机制下的本地中断的处理。本地APIC机制包括:处理器的LINT0和LINT1引脚,APIC计时器,性能监视计数器,热传感器,内部APIC错误检测器。本地中断处理机制包括:LVT,错误状态寄存器(ESR),划分配置寄存器(DCR),初始和当前计数寄存器

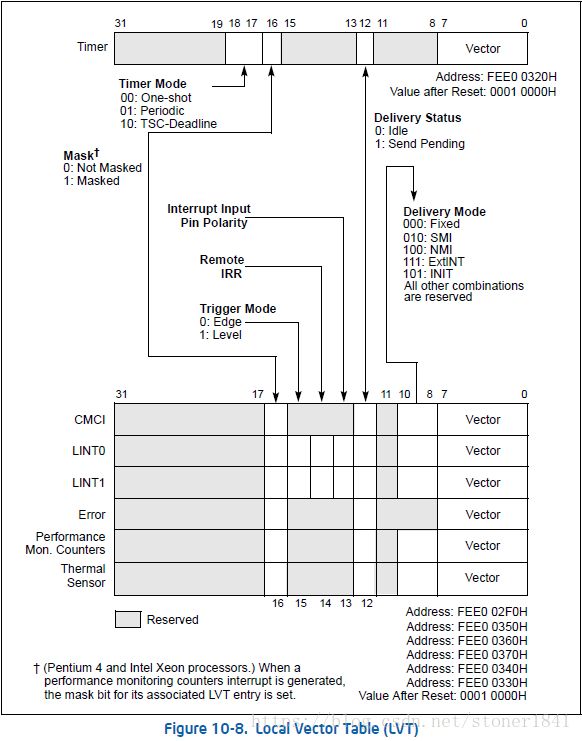

10.5.1 本地向量表

本地向量表(LVT)允许软件去规定本地中断以哪种方式派发给处理器核心。它包括以下32位APIC寄存器(参照图10-8)

- LVT CMCI 寄存器(FEE0 02F0H)

- 当在支持CMCI的机器检查库中的修正机器检查错误计数达到阈值时,规定了中断的分发(参照15.5.1节,CMCI 本地APIC 接口)

- LVT 计时器寄存器(FEE0 0320H)

- 当APIC 计时器发出一个中断时,规定了中断的分发(参照10.5.4节,APIC 计时器)

- LVT 热监视器寄存器(FEE0 0330H)

- 当热传感器生成一个中断时,规定了中断的分发(参照14.7.2节,热监视器)。LVT的这一项是执行规范,并不是架构上的。如果执行,它会被定位在FEE0 0330H基址

- LVT 性能计数寄存器(FEE0 0340H)

- 当性能计数器发生一个溢出中断时,规定了中断的分发(参照18.15.5.8节,生成一次溢出中断)。该LVT项是执行规范,并不是架构上的。如果执行,它会被定位在FEE0 0340H基址

- LVT LINT0 寄存器(FEE0 0350H)

- 当LINT0引脚信号态发出中断时,规定了中断的分发

- LVT LINT1 寄存器(FEE0 0360H)

- 当LINT1引脚信号态发出中断时,规定了中断的分发

- LVT 错误寄存器(FEE0 0370H)

- 当APIC检测到一个内部错误时,规定了中断的分发(参照10.5.3节,错误处理)

LVT性能计数寄存器和它相关的中断在P6处理器上被引入,同时也在奔腾4和Intel至强处理器上。LVT热监视器寄存器和它相关的中断在奔腾4和Intel至强处理器上被引入。LVT CMCI寄存器和它相关的中断在Intel至强5500处理上被引入。

如图10-8所示,部分域和标志是不可见的。

LVT表寄存器的设置规范如下:

- Vector

- 中断向量号

- 分发模式

- 规定了哪种中断类型被送到处理器。一些分发模式只在与特定的触发模式下才生效。有如下分发模式:

- 000(Fixed) —— 分发规定在向量域内的中断

- 010(SMI) —— 通过处理器的逻辑SMI信号路径分发一个SMI中断给处理器核心

- 100(NMI) —— 分发一个NMI中断给处理器。向量信息被忽略

- 101(INIT) —— 分发一个INIT请求给处理器核心,而这会让处理器执行一次INIT。当使用该分发模式,向量域应当被设为00H以向前兼容。对于LVT CMCI寄存器, LVT热监视寄存器,LVT性能计数寄存器,这是不支持的

- 111(ExtINT) —— 使处理器响应中断,类似于该中断源于外部连接着的(8259A-兼容模式)中断处理器。一次特殊的INTA总线周期,相当于ExtINT,会被路由给外部控制器。同时,外部控制器期望能够提供向量信息。APIC的架构在一个系统中只有一个ExtINT源,通常在兼容模式桥中。系统中应该只有一个处理器有一个LVT项被配置使用该ExtINT分发模式。LVT CMCI寄存器,LVT热传感器寄存器,LVT性能计数寄存器不支持该模式

- 分发状态(只读)

- 以下表示了中断分发状态:

- 0 (Idle) —— 该中断源当前不活跃或者该源的前中断已经分发到了处理器核心上,并且被接收到

- 1 (Sending Pending) —— 表明该源的中断已经被分发给了处理器核心,但还没有被接收(参照10.5.5节,本地中断的接收)

- 中断输入引脚的极性

- 规定了对应中断引脚的极性:(0)拉高活跃、(1)拉低活跃

- 远程IRR标记(只读)

- 对于Fixed mode,水平触发中断,本地APIC接收中断去服务时该标志被设置,而收到一个来自处理器的EOI命令时被重置。对于边缘触发中断和其他分发模式,该标志的含义未定义

- 触发模式

- 本地LINT0和LINT1引脚可以选择触发模式:(0)边缘触发;(1)水平触发。只有分发模式是Fixed mode时,该标志才有效。当分发模式为NMI,SMI或者INIT时,触发模式保持边缘触发。当分发模式为ExtINT时,为水平触发。计时器和错误中断可以等同于边缘触发

- 如果本地 APIC 不与 I/O APIC 连接使用,则为Fixed mode;奔腾4,Intel至强和P6家族处理器保持使用水平触发,不管是否边缘触发被选

- 软件应当把LVT LINT1寄存器的触发模式设为0(边缘触发)。LINT1不支持水平触发

- 标志

- 中断标志:(0)打开中断接收;(1)禁止接收中断。当本地 APIC 处理性能监视计数器中断时,它会自动设置LVT性能监视计数寄存器的标志。该标志在重置时会被设置为1。可以被软件清除

- 计时器模式

- 第17到18位表示时钟模式(参照10.5.4节)

- 00 ——

- 01 ——

- 10 ——

- 11 ——

图10-8 本地向量表(LVT)

10.5.2 有效的中断向量

Intel 64和IA-32架构定义了256个中断向量号,从0到255(参照6.2节,异常和中断向量)。本地和I/O APIC支持其中的240(16到255)个为有效中断

当0到15的中断向量通过本地APIC被发送或者接收,APIC会在它的错误状态寄存器表明一个无效的向量(参照10.5.3节,错误处理)。Intel 64和IA-32架构保留16到31为预定义中断,异常,Intel保留编码(参照表6-1)。然而,本地APIC并不把这个范围内的向量作为无效向量

当一个无效向量值(0到15)被写到LVT项并且分发模式为Fixed(第8到11位为0)时,APIC可以激发一个无效向量错误,不论是否设置了标记位还是有中断输入

10.5.3 错误处理

本地APIC记录了在错误状态寄存器(ESR)中的错误,而该错误是在中断处理过程中被检测到的。ESR的格式如图10-9;它包含以下标记:

- 第0位:发送校验和错误

- 当本地APIC检测到发送至APIC总线上消息的一个校验和错误时设置。仅在P6家族和奔腾处理器上被使用

- 第1位:接收校验和错误

- 当本地APIC检测到接收到APIC总线上消息的一个校验和错误时设置。仅在P6家族和奔腾处理器上被使用

- 第2位:发送确认错误

- 当本地APIC检测到APIC总线上任意的APIC没有确认发送的消息时设置。仅在P6家族和奔腾处理器上被使用

- 第3位:接收确认错误

- 当本地APIC检测到APIC总线上任意的APIC没有确认接收到的消息时设置。仅在P6家族和奔腾处理器上被使用

- 第4位:可重定向IPI

- -