vivado交通灯设计verilog代码ego1板红绿灯时间可修改

名称:vivado交通灯设计verilog代码ego1板红绿灯时间可修改

软件:VIVADO

语言:Verilog

代码功能:

十字路口红绿灯设计;

1、每次通行时间可在0-99秒内设定,可以通过按键修改通行时间。

2、路口四边均设红黄绿三色信号灯和用于计时的两位数码管显示时间(十进制数)。

3、黄灯亮时,要求每秒闪亮一次。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

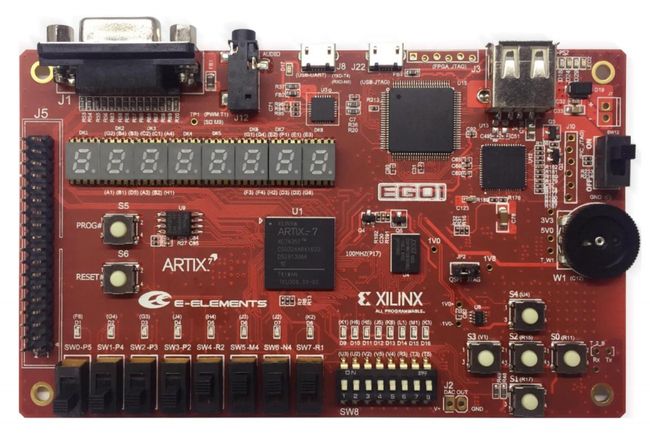

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

代码下载:vivado交通灯设计verilog代码ego1板红绿灯时间可修改名称:vivado交通灯设计verilog代码ego1板红绿灯时间可修改(代码在文末下载)软件:VIVADO语言:Verilog代码功能:十字路口红绿灯设计;1、每次通行时间可在0-99秒内设定,可以通过按键修改通行时间。2、路口四边均设红黄绿三色信号灯和用于计时的两位数码管显示时间(十进制数)。3、黄灯亮时,要求每秒闪亮一次。FPGA代码Verilog/VHDL代码资源下载:www.hdlcod![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=307

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=307

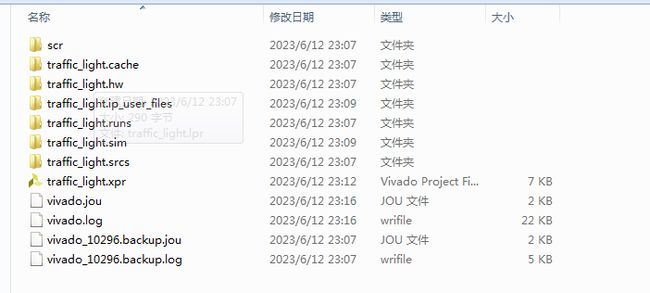

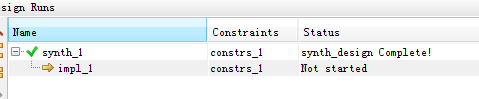

1. 工程文件

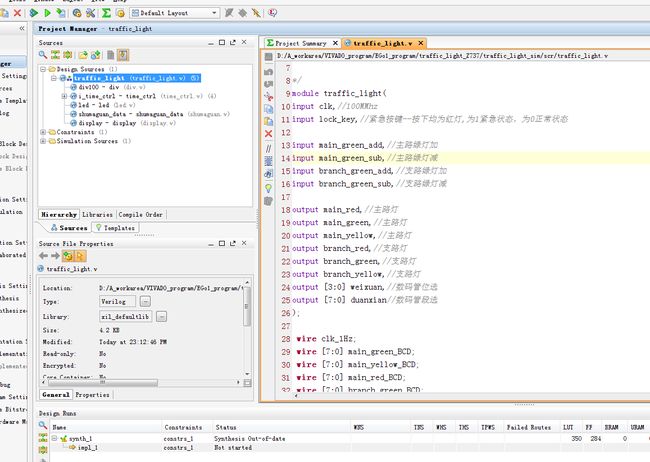

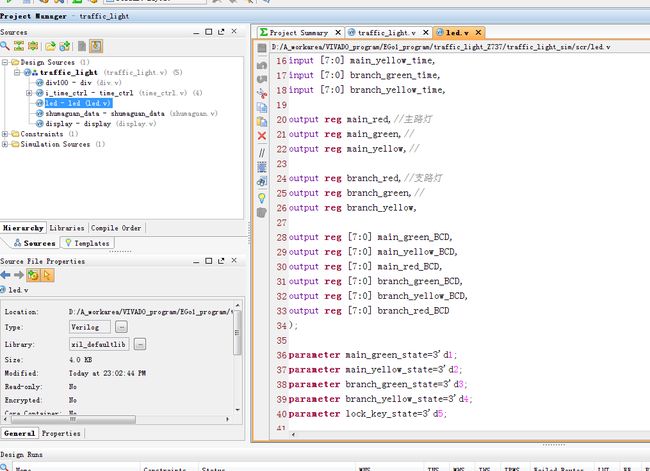

2. 程序文件

3. 程序编译

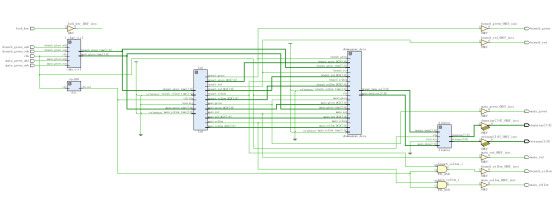

4. RTL图

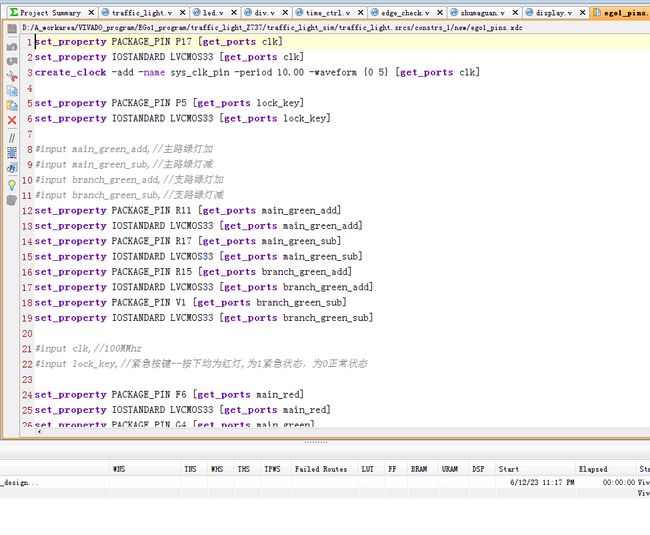

5. 管脚分配

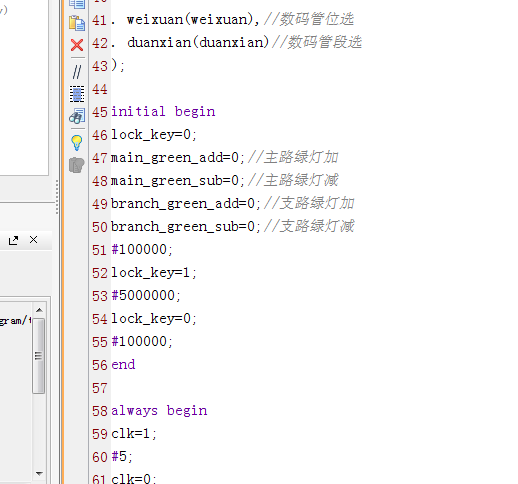

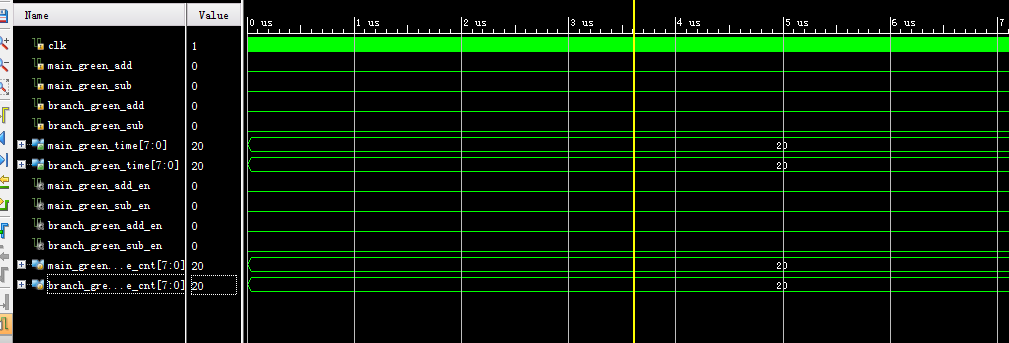

6. Testbench

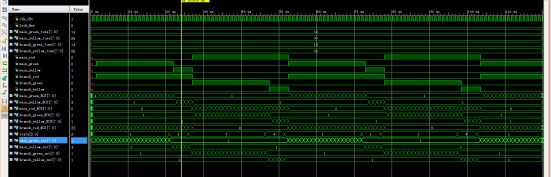

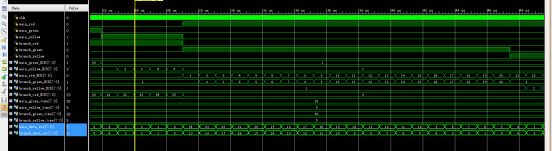

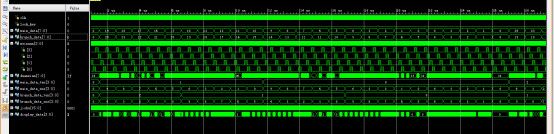

7. 仿真图

整体仿真图

分频模块

时间控制模块

交通灯控制模块

倒计时模块

显示模块

部分代码展示:

/* 红->绿 绿->黄 黄->红 1、红--计时main_red_times------------------------绿--计时main_green_times---main_yellow_times黄灯---------------红 2、绿--计时branch_green_times---branch_yellow_times黄灯--------------------红--计时branch_reg_times-------------------绿 */ module traffic_light( input clk,//100MMhz input lock_key,//紧急按键--按下均为红灯,为1紧急状态,为0正常状态 input main_green_add,//主路绿灯加 input main_green_sub,//主路绿灯减 input branch_green_add,//支路绿灯加 input branch_green_sub,//支路绿灯减 output main_red,//主路灯 output main_green,//主路灯 output main_yellow,//主路灯 output branch_red,//支路灯 output branch_green,//支路灯 output branch_yellow,//支路灯 output [3:0] weixuan,//数码管位选 output [7:0] duanxian//数码管段选 ); wire clk_1Hz; wire [7:0] main_green_BCD; wire [7:0] main_yellow_BCD; wire [7:0] main_red_BCD; wire [7:0] branch_green_BCD; wire [7:0] branch_yellow_BCD; wire [7:0] branch_red_BCD; wire [7:0] main_data_out; wire [7:0] branch_data_out; wire main_red_led;//主路灯 wire main_green_led;//主路灯 wire main_yellow_led;//主路灯 wire branch_red_led;//支路灯 wire branch_green_led;//支路灯 wire branch_yellow_led;//支路灯 assign main_red=main_red_led;//主路灯 assign main_green=main_green_led;//主路灯 assign main_yellow=main_yellow_led & clk_1Hz;//主路灯 assign branch_red=branch_red_led;//支路灯 assign branch_green=branch_green_led;//支路灯 assign branch_yellow=branch_yellow_led & clk_1Hz;//支路灯 //分频模块 div div100 ( . clk(clk), . clk_out(clk_1Hz) ); //按键调整时间 wire [7:0]main_green_time; wire [7:0]main_yellow_time; wire [7:0]branch_green_time; wire [7:0]branch_yellow_time; //时间控制模块 time_ctrl i_time_ctrl( . clk(clk), . main_green_add(main_green_add),//主路绿灯加 . main_green_sub(main_green_sub),//主路绿灯减 . branch_green_add(branch_green_add),//支路绿灯加 . branch_green_sub(branch_green_sub),//支路绿灯减 . main_green_time(main_green_time),//主路绿灯时间 . branch_green_time(branch_green_time)//支路绿灯时间 ); assign main_yellow_time=8'd5;//主路黄灯时间设置为5秒 assign branch_yellow_time=8'd5;//支路黄灯时间设置为5秒 /// reg [7:0] display_main; reg [7:0] display_branch; //交通灯控制模块 led led( . clk_1Hz(clk_1Hz), . lock_key(1'b0),//紧急按键,为1紧急状态,为0正常状态 . main_red(main_red_led),//主路灯 . main_green(main_green_led),//主路灯 . main_yellow(main_yellow_led),//主路灯 . branch_red(branch_red_led),//支路灯 . branch_green(branch_green_led),//支路灯 . branch_yellow(branch_yellow_led),//支路灯 . main_green_time(main_green_time), . main_yellow_time(main_yellow_time), . branch_green_time(branch_green_time), . branch_yellow_time(branch_yellow_time), . main_green_BCD(main_green_BCD),//绿灯时间计数 . main_yellow_BCD(main_yellow_BCD),//黄灯时间计数 . main_red_BCD(main_red_BCD),//红灯时间计数 . branch_green_BCD(branch_green_BCD),//绿灯时间计数 . branch_yellow_BCD(branch_yellow_BCD),//黄灯时间计数 . branch_red_BCD(branch_red_BCD)//红灯时间计数 ); //显示数据生成模块 shumaguan_data shumaguan_data( . clk(clk), . main_red(main_red_led),//主路灯 . main_green(main_green_led),//主路灯 . main_yellow(main_yellow_led),//主路灯 . branch_red(branch_red_led),//支路灯 . branch_green(branch_green_led),//支路灯 . branch_yellow(branch_yellow_led),//支路灯 . main_green_BCD(main_green_BCD),//绿灯时间计数 . main_yellow_BCD(main_yellow_BCD),//黄灯时间计数 . main_red_BCD(main_red_BCD),//红灯时间计数 . branch_green_BCD(branch_green_BCD),//绿灯时间计数 . branch_yellow_BCD(branch_yellow_BCD),//黄灯时间计数 . branch_red_BCD(branch_red_BCD),//红灯时间计数 . main_green_time(main_green_time), . main_yellow_time(main_yellow_time), . branch_green_time(branch_green_time), . branch_yellow_time(branch_yellow_time), . main_data_out(main_data_out),//主路数码管数据显示 . branch_data_out(branch_data_out)//支路数码管数据显示 ); display display ( . clk(clk), . lock_key(1'b0), . main_data(main_data_out),//主路数码管数据显示 . branch_data(branch_data_out),//支路数码管数据显示 . weixuan(weixuan),//位选,高电平亮 . duanxian(duanxian)//段选,高电平亮 ); endmodule