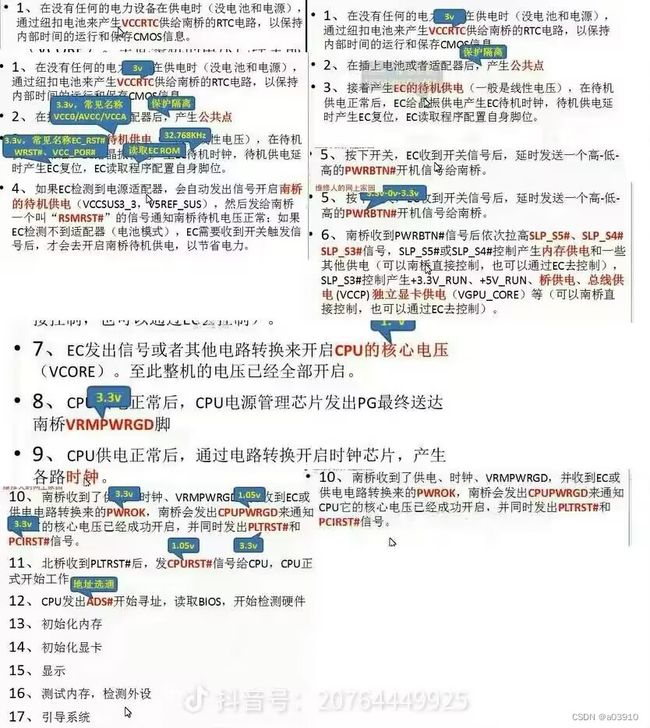

amd平台的amd芯片组的时序。

以amd_dell_m4040的板子为例,单桥。

1.,南桥有两个待机电压VDDCR_11_S和VDDIO_33_S,这和上面的光达的时序图的名字有一点不一样,不管了。

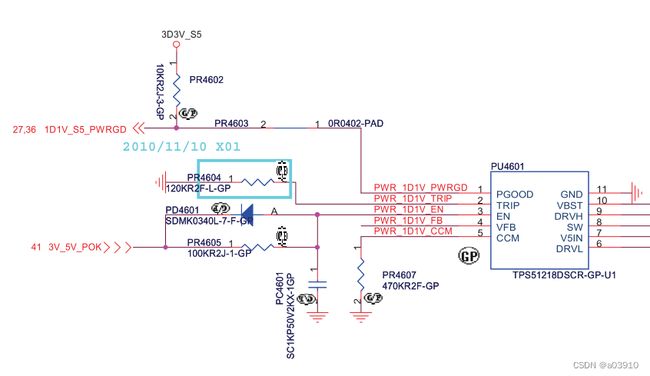

1.1.,VDDCR_11_S信号由1D1V_PWR信号转化而来,1D1V_PWR信号来自芯片TPS51218DSCR-GP-U1,受到3V_5V_POK控制,3V_5V_POK信号来自芯片TPS51125ARGER-GP。

看芯片TPS51125ARGER-GP的数据手册,分析时序。

TPS51125ARGER-GP时序:

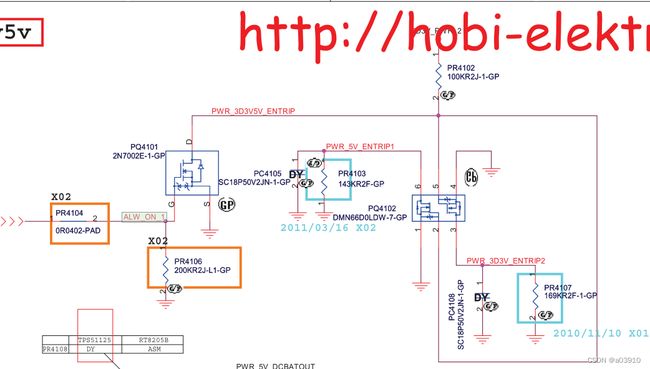

输入vin(芯片的供电)----》输入高电平e0(开启线性供电3.3v和5v)----》输出vreg3,vreg5(3.3v供电和5v供电)----》ENTRIP1,ENTRIP2处于高阻态,或接100k电阻接地(开启pwm的3.3v供电和5v供电)----》输出pwm3.3v,pwm5v(3.3v供电和5v供电)----》输出高电平vo1,vo2(同时芯片内部vo1,vo2替换原来的ldo的3,3v供电和5v供电给reg3.3和vreg5)----》输出PGOOD。

ENTRIP是复合功能引脚。直接接地,是关闭pwm供电,通过100k电阻接地是极限电流限定脚,高电平是开启pwm供电。

现在看PWR_5V_ENTRIP1和PWR_3D3V_ENTRIP2的来源,同时受控于PWR_3D3V5V_ENTRIP信号,最终受控于ALW_ON_1。

当ALW_ON_1为高电平的时候,场管PQ4101PQ4101导通,PWR_3D3V5V_ENTRIP为低电平,场管组PQ4102PQ4102均截止,所以PWR_5V_ENTRIP1和PWR_3D3V_ENTRIP2均为高阻,开启了pwm供电。ALW_ON_1就是3V_5V_EN。

3V_5V_EN来自S5_ENABLE,S5_ENABLE来自ec,何时产生的呢?

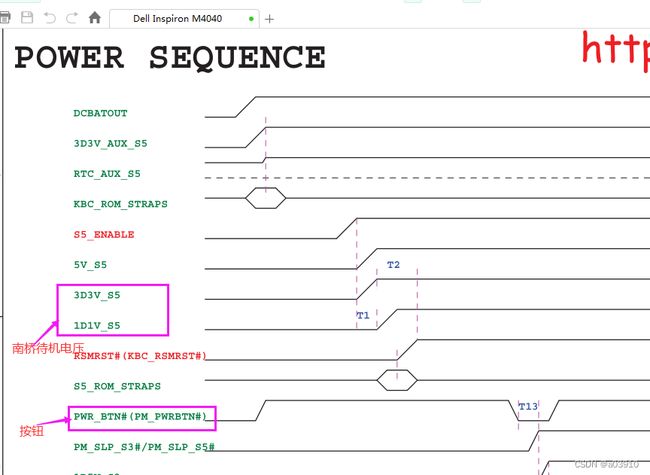

从时序图上看,s5_enable在kbc_rom_straps产生之后自动产生。

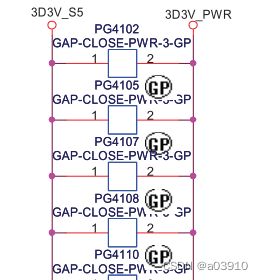

1.2.,现在看南桥的另一个待机电压3D3V_S5,来自3D3V_PWR,3D3V_PWR来自芯片TPS51125ARGER-GP的pwm电压输出。

所以南桥的两个待机电压最终由ec控制产生。

2.,现在看ec的待机条件:供电,时钟,复位,bios,acin。

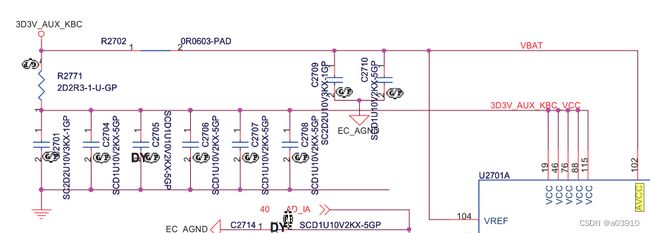

2.1.,ec的待机供电,信号为3D3V_AUX_KBC。

2.2.,ec的时钟。这里没有使用晶振,来自南桥,不过这个板子是单桥,还是称之为南桥,是因为习惯。

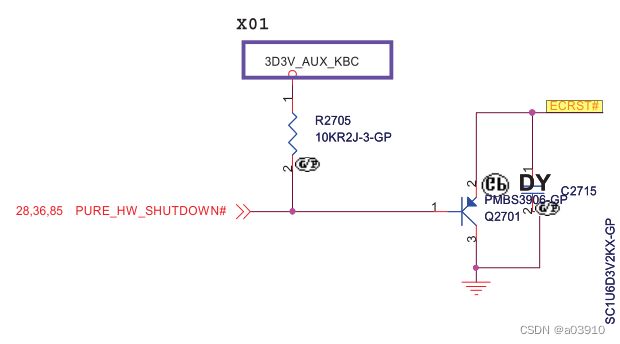

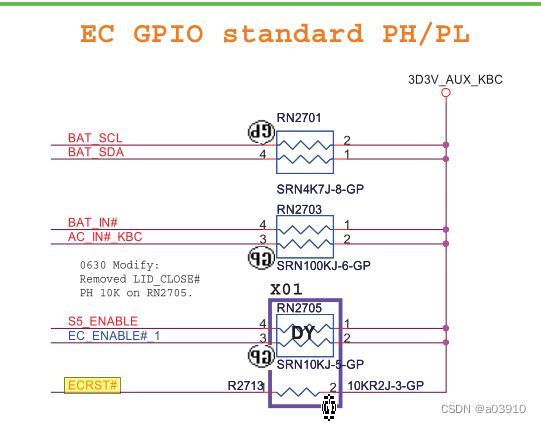

2.3.,ec的复位引脚vcc_por#,接了信号ecrst#。ecrst#来自如图所示。

2.3.,ec的复位引脚vcc_por#,接了信号ecrst#。ecrst#来自如图所示。

ecrst#要高电平,才能触发复位。那么PURE_HW_SHUTDOWN#要为高电平,3D3V_AUX_KBC也要为高电平。3D3V_AUX_KBC和PURE_HW_SHUTDOWN#先不管。

2.4.,现在看适配器检测信号acin。

充电芯片BQ24707ARGRR-GP开漏输出acok#,当检测到适配器的时候,输出高阻信号AC_IN#。

ac_in高阻,场管pq4003截止,PWR_CHG_ACOK为高电平,

PWR_CHG_ACOK高电平给信号PSL_IN1,PSL_IN1给ec。

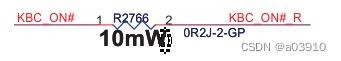

但是继续还有高电平PSL_IN1给了AC_IN#_KBC,AC_IN#_KBC,当没有按电源开关的时候,AC_IN#_KBC高电平产生高电平KBC_ON#,这是无效的。

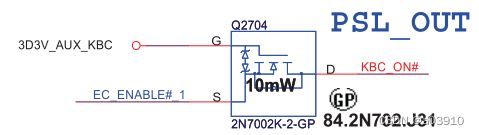

当按下电源之后,产生低电平KBC_ON#,KBC_ON#转化为低电平KBC_ON#_R,KBC_ON#_R导通场管Q2703Q2703,产生供电3D3V_AUX_KBC,这是ec的待机供电。

当ec发出有效EC_ENABLE#_1的时候,场管Q2704导通,产生低电平KBC_ON#,也产生供电3D3V_AUX_KBC。这是什么意思呢?因为按下电源开关产生的是触发信号,所以只会提供一会儿的ec待机供电3D3V_AUX_KBC,但是这一会儿,ec发出低电平EC_ENABLE#_1,使得输出kbc_on#为低电平,所以,kbc_on#不会被AC_IN#_KBC拉高,那么就持续输出ec的待机电压了。

那么,可以因此确定PSL_IN1给ec就是acin信号给ec。

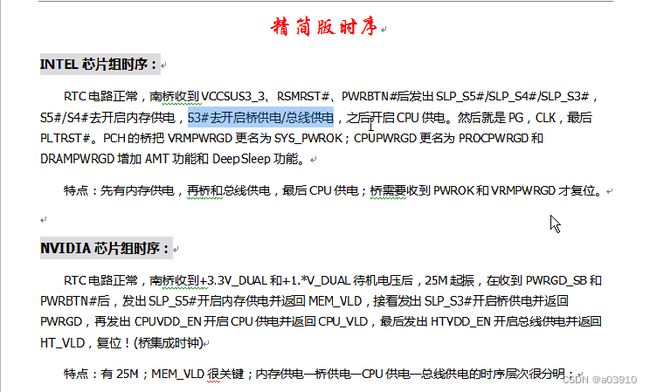

接下来的步骤我懒得写了,我给出笔记本电脑一般的上电时序的步骤。

值得提到的是到底是按按钮之后ec发出信号开启南桥待机电压,还是在ec的条件都满足之后,自动发出信号开启南桥待机电压,这在不同的板子是不一样的,所以这个时候需要观察板子自带的时序图。这个板子的时序说了是自发产生,不过,这是适配器模式的时序,还有电池模式,前面的时序一般会稍微不同,按照一般的笔记本标准上电图的说法,但是我懒得看电池模式了。

fch内部集成了时钟芯片。