I2C-双向二线制同步串线总线-IIC-详细理解整理

1、简介

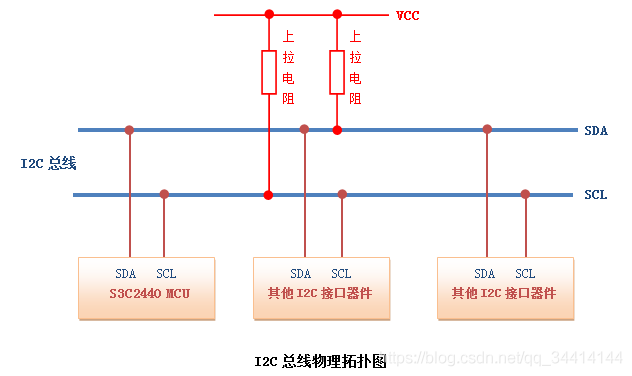

I2C总线是由Philips(飞利浦)公司开发的一种简单、双向二线制同步串行总线。

它只需要两根线即可在连接于总线上的器件之间传送信息。

SDA(串行数据线) ----> 双向 I/O 线,需通过上拉电阻接电源VCC。

SCL (串行时钟线) ----> 总线空闲时,两根线都是高电平。

每个连到总线的器件都有 唯一的地址。

I2C总线是一个多 master 总线,通过仲裁防止数据破坏,但同一时刻只允许有一个 master 。

可编程器件既可作为 master 也可作为 slave。任何器件都可以作为transmitter 或 receiver。

2、术语

master (主机) :初始化start数据传送,产生时钟信号,stop数据传送的器件。

slave (从机) :被寻址的器件均被认为是从器件

transmitter(发送器):发送数据到总线的器件

receiver (接收器):从总线接收数据的器件

仲裁:多个主机同时想控制总线,只允许一个主机控制总线并使报文不被破坏的过程

在总线上主和从、从和收、发的关系不是恒定的,取决于此时数据传送方向。

I2C通信方式为半双工,只有一根SDA线,同一时间只可以单向通信。

3、仲裁

I2C总线上的仲裁分两部分:SCL线的同步和SDA线的仲裁。

3.1、SCL线的同步(时钟同步)

SCL同步,是由于总线具有线“与”的逻辑功能。

只要有一个器件发低电平时,总线就为低电平。

所有的器件都发高电平时,总线才为高电平。

SCL 时钟的低电平周期由低电平时钟周期最长的器件决定,

SCL 时钟的高电平周期由高电平时钟周期最短的器件决定。

(1)、SCL 线的高->低切换会使器件开始数它们的低电平周期,而且一旦器件的时钟变低电平,它会使 SCL 线保持这种状态直到到达时钟的高电平。

(2)、如果另一个时钟仍处于低电平周期,这个时钟的低到高切换不会改变 SCL 线的状态,因此SCL 线被有最长低电平周期的器件保持低电平。此时低电平周期短的器件会进入高电平的等待状态。

(3)、当所有有关的器件数完了它们的低电平周期后,时钟线被释放并变成高电平。所有器件会开始数它们的高电平周期,首先数完成高电平周期的器件会再次SCl线拉低。

3.2、SDA仲裁

SDA线的仲裁也是建立在总线具有线“与”逻辑功能的原理上的。节点在发送 1 bit数据后,比较总线上所呈现的数据与自己发送的是否一致。一致,就继续发送;不一致,退出竞争。

SDA线的仲裁可以保证I2C总线系统在多个master同时企图控制总线时通信正常进行并且数据不丢失。总线系统通过仲裁只允许一个master可以继续占据总线。

说明:

DATA1和DATA2分别是两个master向总线所发送的数据信号,SDA为总线上所呈现的数据信号,SCL是总线上所呈现的时钟信号。

仲裁过程:

当master1、2同时发送start时,两个主机都发送了高电平信号。这时总线上呈现的信号为高电平,两个主机都检测到总线上的信号与自己发送的信号相同,继续发送数据。

第2个T,2个主机都发送低电平信号,在总线上呈现的信号为低电平,仍继续发送数据。在第3个T ,主机1发送高电平信号,而主机2发送低电平信号。根据总线的线“与”的逻辑功能,总线上的信号为低电平,这时主机1检测到总线上的数据和自己所发送的数据不一样,就断开数据的输出级,转为从机接收状态。这样主机2就赢得了总线,而且数据没有丢失,即总线的数据与主机2所发送的数据一样,而主机1在转为从机后继续接收数据,同样也没有丢掉SDA线上的数据。因此在仲裁过程中数据没有丢失。

4、常见的器件

| 器件名 | 主机/从机 | 发送器/接收器 |

|---|---|---|

| 微控制器 | master、slave | transmitter、receiver |

| 存储器 | slave | transmitter、receiver |

| es8388 | slave | transmitter、receiver |

| LCD驱动器 | slave | receiver |

5、特征

数据单位:以字节(8位)为单位进行双向传输,高位在前。

传输字节数量:不受限制。

器件地址:7bit,还有1个bit预留给读写标志位,代表传输方向。

传输速率:

标准模式 100 kbit/s,

快速模式 400 kbit/s,

高速模式 3.4 Mbit/s。

6、传输条件

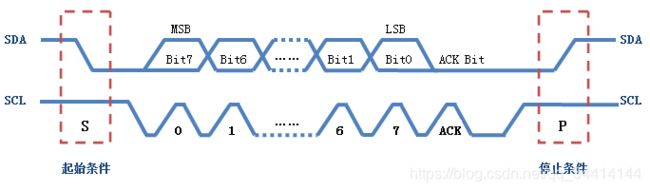

传输必须以一个起始信号(start)作为开始条件。当SCL为高电平而SDA由高到低的跳变,表示产生一个起始条件。

传输必须以一个结束信号(stop)作为停止条件。当SCL为高电平而SDA由低到高的跳变,表示产生一个停止条件。

start和stop都是由master产生的。

起始条件后总线被认为处于忙(busy)的状态, 在停止条件后总线被认为再处于空闲(idle)状态。

7、数据传输

master在SCL产生单个时钟脉冲,transmitter将在SDA上传输一个bit。一个byte按高位到低位的顺序传完后,紧接着receiver回复ACK。每个字节后必须跟一个响应位。

ACK (acknowledge 告知已收到) : receiver已经成功地接收了该字节。

NACK(not acknowledge 告知未收到) :一般表示receiver没有成功接收该字节。

7.1、响应(ACK)如何产生?

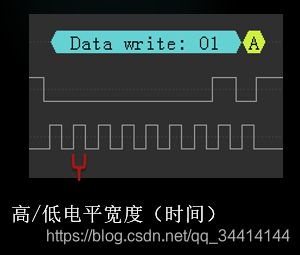

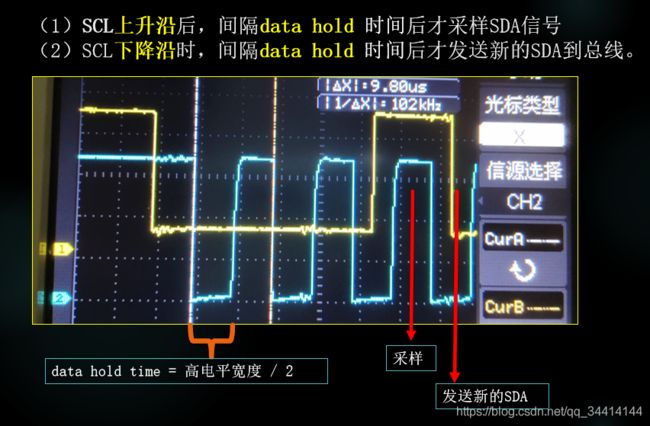

传送数据时,SCL高电平期间,SDA上电平必须稳定。

低电平为数据0,高电平为数据1。

在SCL为低电平期间,才允许SDA上的电平改变状态。

在响应的时钟脉冲期间transmitter释放SDA线,receiver将 SDA 线拉低(ACK)。

7.2、不响应(NACK)如何产生?

当slave不能响应address时,slave必须使SDA保持高电平(NACK)。

当slave响应了address,但不能接收更多字节,需slave 在last byte后产生NACK。

当有master receiver,它必须在接收完last byte后产生一个NACK,向slave transmitter通知结束。

7.3、slave如何响应从机address?

当master发送slave地址到总线上,系统中的每个器件都在起始条件后,将总线上前7 位与自己的地址比较,如果一样器件会认为被寻中,回复ACK,至于是从机 receiver还是从机transmitter都由 R/ W 位决定。

例如:上图发出的地址数据是0x40,前7位是0x20,被寻址的器件做从机 receiver

8、时序

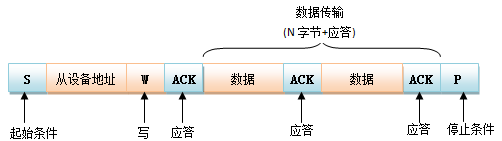

第1种:master往slave写数据

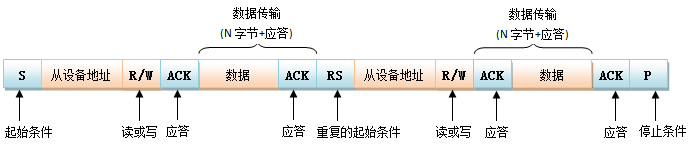

第2种:master往slave写数据,再从slave读数据

第3种:master从slave读数据

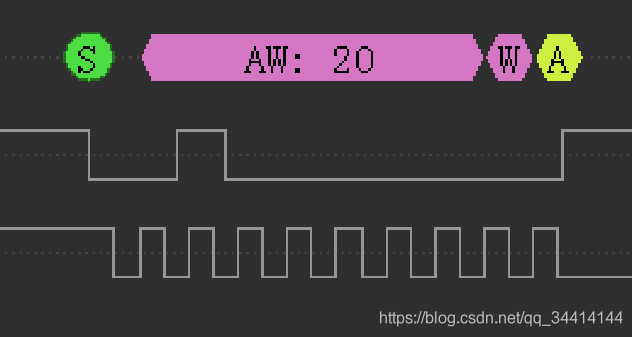

8.1、master往slave写数据(传输方向不变)

假设微控制器 A ,发送数据到,微控制器 B,传输数据过程如下:

规则:

slave地址 : 0x20

写标志 : 0x00

寄存器地址 : 0x03

数据 : 0x00 , 0x01

byte1 = ( slave地址<< 1 ) | 写标志 = 0100 0000 = 0x40

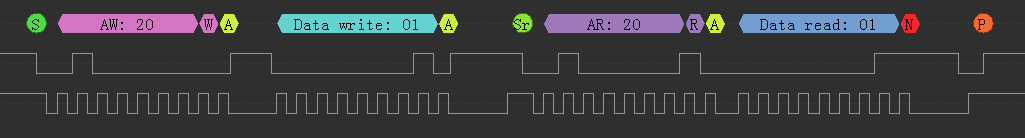

8.2、master往slave写数据,再从slave读回数据(传输方向改变)

假设微控制器 A ,想先往微控制器 B写数据,再从微控制器 B接收信息,传输数据过程如下:

slave地址 : 0x20

数据 : 0x01

寄存器地址 : 0x01

读写标志 : 0x00(写),0x01(读)

Sr : 重复开始

byte1 = ( slave地址<< 1 ) | 写标志 = 0100 0000 = 0x40

byte3 = ( slave地址<< 1 ) | 读标志 = 0100 0001 = 0x41

8.3、master从slave读数据

假设微控制器 A ,想直接从微控制器 B,接收信息,传输数据过程如下:

假如slave地址 : 0x20

读标志 : 0x01

byte1 = ( slave地址<< 1 ) | 读标志 = 0100 0001 = 0x41

9、IIC控制器描述

支持 IIC Master/Slave 模式,master时支持7位和10位寻址;

支持 IIC transmitter 和 receiver 功能;

Controller slave 为7位地址,可配置,支持地址广播呼叫;

IIC 总线速率可配置;

支持中断和查询操作方式操作。

9.1、寄存器分类

(1)控制寄存器

(2)参数寄存器

(3)中断相关寄存器

(4)状态寄存器

(5)数据发送寄存器、数据接收寄存器

(6)Slave地址寄存器