【USTC】verilog 习题练习 41-45

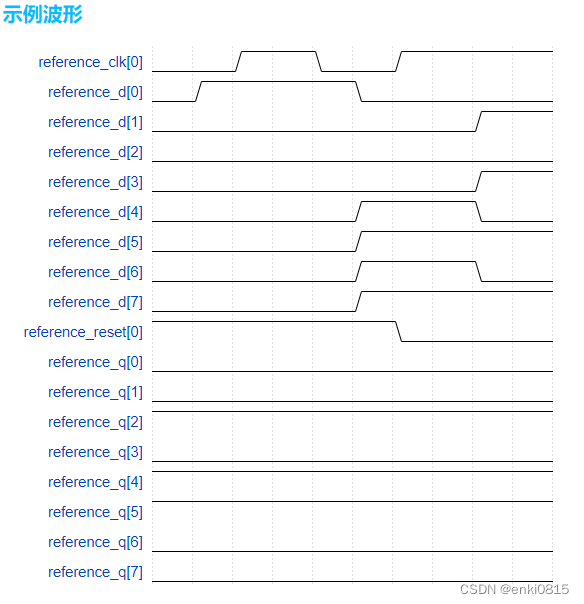

41 下降沿触发的寄存器

题目描述

在时序逻辑电路中,敏感变量不但可以是触发信号的上升沿(posedge),也可以是下降沿(negedge),试创建 8bit 位宽的寄存器,所有 DFF 都应该由 clk 的下降沿(负边缘)触发。同时采用高电平有效的同步复位方式,复位值为 0x34 而不是零。

输入格式

输入信号 clk,时钟信号。 输入信号 reset,复位信号,高电平有效(复位)。 输入信号 d,位宽 8bit,任意数据信号。

输出格式

输出信号 q,位宽 8bit,在时钟下降沿取输入信号 d 的值,若复位信号有效则复位为值 0x34,复位方式为同步复位。

module top_module (

input clk ,

input reset ,

input [7:0] d ,

output reg [7:0] q

);

// Write your code here

always @(negedge clk) begin

if(reset) begin

q <= 8'h34;

end else begin

q <= d;

end

end

endmodule

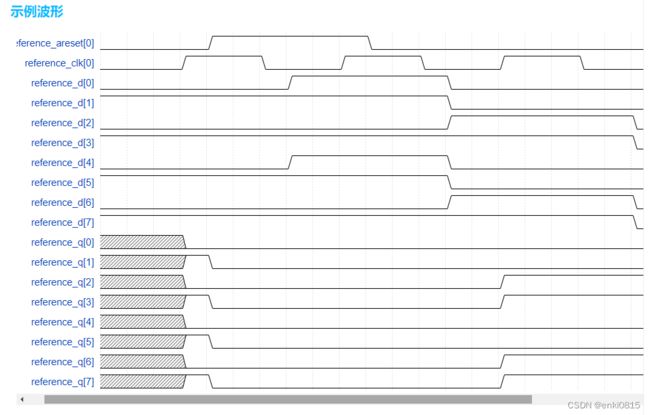

42 异步复位的寄存器

题目描述

在前面的例子中,复位信号只能在触发信号的触发边沿才能起作用,也就是说如果没有触发边沿就无法对电路复位,这大大限制了复位的功能,因此还有一种经常使用的复位方式,称为异步复位。

为了使复位信号不依赖于时钟边沿,则复位信号也应该放在always进程块的敏感变量列表中。复位信号高电平有效和低电平有效在编码时稍有不同,对于高电平有效的复位信号来说,可以写成如下形式:

always@(posedge clk or posedge reset)

begin

if(reset) …

else …

end

如果是低电平有效的复位信号,则应写成如下形式:

always@(posedge clk or negedge reset)

begin

if(~reset) …

else …

end

试创建Verilog模块,实现一个时钟上升沿触发的,支持高电平有效的异步复位功能的8bit寄存器,寄存器复位值为0。

输入格式

2个 1bit 位宽的信号 clk、areset 1个 8bit 位宽的信号 d

输出格式

1个 8bit 位宽的信号 q

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output reg [7:0] q

);

// Write your code here

always@(posedge clk or posedge areset)

begin

if(areset) q <= 8'b0;

else q <= d;

end

endmodule

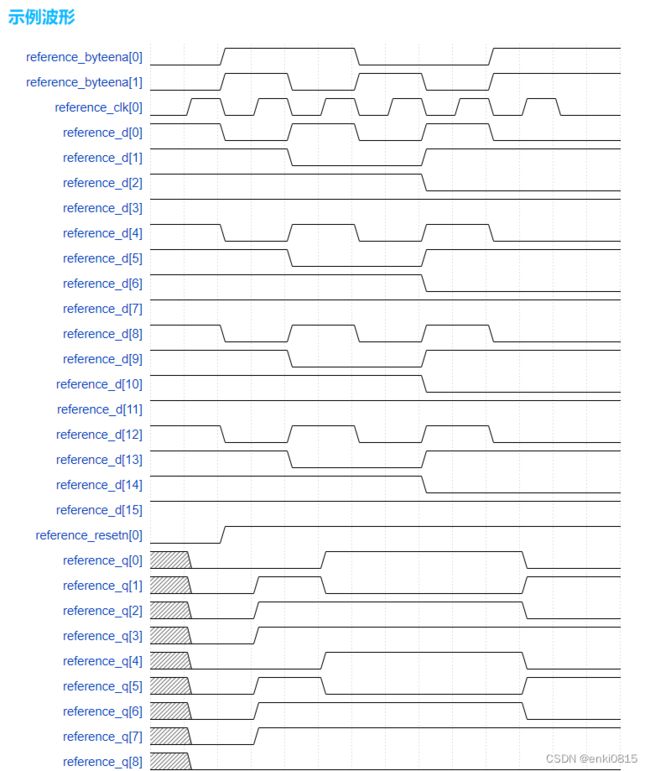

43 带使能的寄存器

题目描述

在前面的电路中,寄存器输出端 q 在每个时钟的上升沿都会更新一次,但有时候我们可能需要使输出端保持不变,这时就需要加入使能信号,创建一 16bit 位宽(2byte)的寄存器,其中每字节都由一个使能信号控制,使能为 0 时,输出保持不变,使能为 1 时更新 q。时钟上升沿触发,同步复位,复位低电平有效,复位值为 0。

输入格式

任意有效的 16bit 位宽数据

输出格式

每个字节都由一个使能信号控制:使能为0时输出保持不变,使能为1时更新q

module top_module(

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output reg [15:0] q

);

always @(posedge clk) begin

if (~resetn)

q <= 16'd0;

else

case(byteena)

2'b11 : q <= d;

2'b10 : q[15:8] <= d[15:8]; //byteena[1] 控制上字节 d[15:8]

2'b01 : q[7:0] <= d[7:0]; //byteena[0] 控制下字节 d[7:0]

default : q <= q;

endcase

end

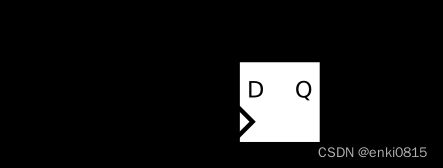

endmodule44 触发器+逻辑门

题目描述

输入格式

1

输出格式

1

module top_module (

input clk,

input in,

output reg out);

//your code

wire res;

assign res = in ^ out;

always @(posedge clk) begin

out <= res;

end

endmodule

45 寄存器+逻辑门

题目描述

编写Verilog代码,实现下图所示的电路功能,假设所有D触发器的初始复位值为0

输入格式

clk,x

输出格式

z

module top_module (

input clk,

input x,

output z

);

reg Q1=0,Q2=0,Q3=0;

wire D1,D2,D3;

assign D1 = x ^ Q1;

assign D2 = x & ~Q2;

assign D3 = x | ~Q3;

always @(posedge clk) begin

Q1 <= D1;

Q2 <= D2;

Q3 <= D3;

end

assign z = ~(Q1|Q2|Q3);

endmodule