Icarus Verilog的使用

本来打算搞VHDL的,但是怎么都没有找到个好的小巧的编译器+模拟器.Verilog跟VHDL差不多就试试它啦o(∩_∩)o .直接看的是http://www.asic-world.com/verilog/veritut.html这里的教程.

Icarus Verilog官方地址在http://iverilog.icarus.com/,windows版的在http://bleyer.org/icarus/一共就7M.

安装后有主要的三个工具iverilog.exe--编译工具 vvp.exe模拟运行的 gtkwave.exe显示模拟结果的.

以一个简单的编码程序说明下.输入是 0x0002输出就是1,输入是0x0004输出是2具体可以看http://www.asic-world.com/examples/verilog/encoder.html#Encoder_-_Using_if-else_Statement这里.

同时我也把代码贴出来.

module encoder(binary_out,encoder_in,enable);

output [3:0] binary_out;

input enable;

input [15:0] encoder_in;

reg [3:0] binary_out;

always @ (enable or encoder_in)

begin

binary_out = 0;

if(enable) begin

if(encoder_in == 16'h0002) begin

binary_out = 1;

end if(encoder_in == 16'h0004) begin

binary_out = 2;

end if(encoder_in == 16'h0008) begin

binary_out = 3;

end if(encoder_in == 16'h0010) begin

binary_out = 4;

end if(encoder_in == 16'h0020) begin

binary_out = 5;

end if(encoder_in == 16'h0040) begin

binary_out = 6;

end if(encoder_in == 16'h0080) begin

binary_out = 7;

end if(encoder_in == 16'h0100) begin

binary_out = 8;

end if(encoder_in == 16'h0200) begin

binary_out = 9;

end if(encoder_in == 16'h0400) begin

binary_out = 10;

end if(encoder_in == 16'h0800) begin

binary_out = 11;

end if(encoder_in == 16'h1000) begin

binary_out = 12;

end if(encoder_in == 16'h2000) begin

binary_out = 13;

end if(encoder_in == 16'h4000) begin

binary_out = 14;

end if(encoder_in == 16'h8000) begin

binary_out = 15;

end

end

end

endmodule

编译方法很简单 只要使用 iverilog encoder.v 就可以了.

单独的这一个模块是不能够运行的,得写个测试程序如下.

module encoder_te();

reg enable;

reg [15:0] encoder_in;

wire [3:0] binary_out;

initial begin

$dumpfile("test.vcd"); //这两行主要是给gtkwave这个工具使用的...

$dumpvars(0,encoder_te);

$monitor("%g\t %b %b %b",

$time,enable,encoder_in,binary_out);

enable = 0;

#5 enable = 1;

#5 encoder_in = 16'h0004;

#6 encoder_in = 16'h0040;

#7 encoder_in = 16'h0400;

#8 encoder_in = 16'h1000;

#10 $finish;

end

encoder en(binary_out,encoder_in,enable);

endmodule

编译下iverilog -o dsn encoder.v encoder_te.v 得到文件dsn.使用 vvp运行下 vvp dsn

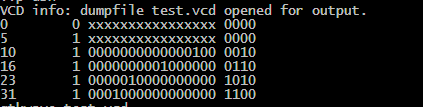

结果如下.

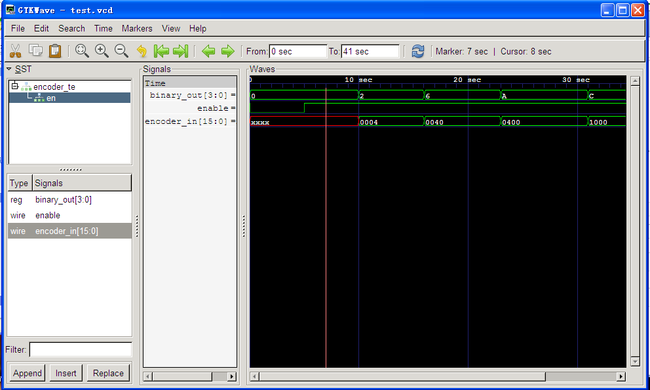

运行后会有文件test.vcd得出 这个文件之间传给gtkwave就可以可. 运行gtkwave test.vcd

结果如下

很好.耶.

当然为了简化中间过程写了个简单的Python脚本

import os

import sys

srcs = "encoder.v encoder_te.v"

out = 'dsn'

verilog = 'iverilog'

vvp = 'vvp'

gtkwave = 'gtkwave'

dumpvcd = 'test.vcd'

(CL,RUN,SIM) = (True,True,True)

if CL:

command = verilog+" -o "+out+" "+srcs

print command

res = os.system(command)

if res != 0: #这句其实不太顶用编译时有误也会返回0 ~>_<~+

sys.exit()

if RUN:

command = vvp + " "+out

print command

res = os.system(command)

if res != 0:

sys.exit()

if SIM:

command = gtkwave+" "+dumpvcd

print command

res = os.system(command)

if res != 0:

sys.exit()

iverilog 还可以将verilog文件转换为VHDL文件 具体看http://iverilog.wikia.com/wiki/User_Guide

每次改变几个变量就可以了.等我把Scons搞定后.试试写用scons扩展.o(∩_∩)o

PS.昨晚下载了个Quartus® II的Web Edition (free) 这版本.搞得有好几个G.可是里面什么乱七八糟的都有

cygwin,tcl,perl.....我找了半天也没找到怎么模拟运行程序,太菜了.o(︶︿︶)o .