《翻译》Intel 64 与 IA-32 架构软件开发者手册卷1翻译

《前言》

翻译自官方的PDF版手册,可以从下述站点下载英文原版:

http://www.intel.com/content/www/us/en/processors/architectures-software-developer-manuals.html

本博文将采用分段中英对照,不定期持续更新的方式进行翻译,

第一卷主要介绍了Intel 64 与 IA-32 的指令集体系结构与编程环境,

不仅对 windows 操作系统的开发人员与应用程序员极有帮助,对于 Unix/Linux 操作系统的开发人员与开源软件程序员而言,也是非常重要的参考资料,

这是因为当今多数 Linux 发行版中自带的大量RPM软件包均是由假设目标运行平台为I386(最早引入IA-32架构概念的Intel处理器)的GCC从源码编译,并且,多数Linux内核也是运行在I386的后继兼容处理器平台上,

这包括了用于桌面娱乐市场的第1~5代 Intel Core处理器,以及用于服务器市场的Intel Xeon系列处理器等。

限于个人知识水平有限,翻译中出现的错误与不妥之处还请广大博友指出并纠正,感激不尽。

下面是翻译正文:

Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn

more at intel.com, or from the OEM or retailer.

Intel 产品的技术特点,由此带来的益处,取决于系统配置,并且可能需要启用硬件,软件,或者服务激活.(即需要前述三者支持)

你可以在 intel.com ,OEM(原始设备制造商),以及零售商处,获取更多信息,

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting

from such losses.

没有任何计算机系统可以保证绝对安全, Intel 不承担任何因数据,系统丢失或被窃取,以及任何由类似前述情形造成的损失引起的法律责任.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

文档中描述的产品可能包含在勘误表中列出的设计缺陷以及错误,从而造成产品偏离公布的标准规格,我们可以根据您的需要提供最新的勘误表。

The Intel 64 and IA-32 Architectures Software Developer’s Manual, Volume 1, describes the basic architecture

and programming environment of Intel 64 and IA-32 processors.

Intel 64 and IA-32 Architectures Software Developer’s Manual, Volume 1 ,描述了 Intel 64 与 IA-32 处理器的基本架构与编程环境

The Intel 64 and IA-32 Architectures Software

Developer’s Manual, Volumes 2A, 2B & 2C, describe the instruction set of the processor and the opcode structure.

These volumes apply to application programmers and to programmers who write operating systems or executives.

The Intel 64 and IA-32 Architectures Software Developer’s Manual, Volumes 2A, 2B & 2C ,描述了处理器的指令集与操作码结构

这些卷(Volumes 2A, 2B & 2C) 适用于应用程序程序员,以及操作系统开发人员,或它们的项目主管.

The Intel 64 and IA-32 Architectures Software Developer’s Manual, Volumes 3A, 3B & 3C, describe the operating-system support environment of Intel 64 and IA-32 processors. These volumes target operating-system and BIOS designers

Intel 64 and IA-32 Architectures Software Developer’s Manual, Volumes 3A, 3B & 3C ,描述了 Intel 64 与 IA-32 处理器的操作系统支持环境

这些卷( 3A, 3B & 3C )的目标读者是操作系统与BIOS的设计师。

手册中描述的信息适用的近代 Intel 64 与 IA-32 处理器列举并解释如下:

(此部分因为与原文重复过多,因此直接给出翻译后的结果,大家可以通过此部分“速查”你的Intel处理器使用的内部微架构和开发代号)

P6 家族处理器是基于P6家族微架构的 IA-32 处理器,包括 PentiumPro, Pentium II, Pentium III, and Pentium III Xeon 处理器.

The Pentium 4, Pentium D, 与 Pentium 处理器至尊版,基于 Intel NetBurst 微架构.

多数早期的 Intel Xeon 处理器 也是基于Intel NetBurst 微架构. 例如, Intel Xeon 处理器 5000, 7100 系列基于Intel NetBurst 微架构.

The Intel Core Duo, Intel Core Solo 与 dual-core Intel Xeon 处理器 LV 基于一个改进的 Pentium M 处理器微架构

The Intel Xeon 处理器 3000, 3200, 5100, 5300, 7200 与 7300 系列, Intel Pentium dual-core, IntelCore2 Duo, Intel Core2 Quad, 与 Intel Core2 Extreme处理器,

基于 Intel Core 微架构

The Intel Xeon 处理器 5200, 5400, 7400 系列, Intel Core2 Quad 处理器 Q9000 系列, 与 Intel Core2 Extreme 处理器 QX9000, X9000 系列, Intel Core2 处理器 E8000 系列,

基于增强版本的 Intel Core 微架构

The Intel Atom 处理器家族,基于 Intel Atom 微架构,并且支持 Intel 64(位) 架构

The Intel Core i7 处理器 与 Intel Xeon 处理器 3400, 5500, 7500 系列,基于开发代号名为 Nehalem 的45纳米 Intel 微架构;

开发代号名为 Westmere 的 Intel 微架构是 Nehalem 的32纳米版本

Intel Xeon 处理器 5600 系列, Intel Xeon 处理器 E7 与各种 Intel Core i7, i5, i3 处理器,基于开发代号名为 Westmere 的 Intel 微架构.这些处理器均支持Intel 64(位) 架构.

The Intel Xeon 处理器 E5 家族, Intel Xeon 处理器 E3-1200 家族, Intel Xeon 处理器 E7-8800/4800/2800 产品家族,

Intel CoreTM i7-3930K 处理器, 与第二代 Intel Core i7-2xxx, Intel Core i5-2xxx, Intel Core i3-2xxx 处理器 系列,

基于开发代号名为 Sandy Bridge 的 Intel 微架构,并且支持 Intel 64(位) 架构.

The Intel Xeon 处理器 E7-8800/4800/2800 v2 产品家族, Intel Xeon 处理器 E3-1200 v2 品家族与

第三代 Intel Core 处理器,基于开发代号名为 Ivy Bridge 的 Intel 微架构,并且支持 Intel 64(位) 架构.

The Intel Xeon 处理器 E5-4600/2600/1600 v2 产品家族, Intel Xeon 处理器 E5-2400/1400 v2

产品家族 与 Intel Core i7-49xx 处理器至尊版, 基于开发代号名为 Ivy Bridge-E 的 Intel 微架构,并且支持 Intel 64(位) 架构.

The Intel Xeon 处理器 E3-1200 v3 产品家族与第四代 Intel Core 处理器,基于开发代号名为 Haswell 的 Intel 微架构,并且支持 Intel 64(位) 架构.

The Intel Xeon 处理器 E5-2600/1600 v3 产品家族与 Intel Core i7-59xx 处理器至尊版,

基于基于开发代号名为 Haswell-E 的 Intel 微架构,并且支持 Intel 64(位) 架构.

The Intel Core M 处理器家族与第五代 Intel Core 处理器,基于开发代号名为 Broadwell 的 Intel 微架构,并且支持 Intel 64(位) 架构.

P6 系列, Pentium M, Intel Core Solo, Intel Core Duo 处理器, dual-core Intel Xeon处理器 LV,

与早一代的 Pentium 4 , Intel Xeon处理器 ,仅支持 IA-32 架构(这些为32位处理器)

The Intel Xeon 处理器 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 系列,

Intel Core2 Duo, Intel Core2 Extreme 处理器, Intel Core 2 Quad 处理器, Pentium D 处理器, Pentium Dual-Core 处理器,

较新一代的 Pentium 4 与 Intel Xeon 处理器系列,支持 Intel 64(位) 架构(这些为64位处理器)

IA-32 架构是 Intel 的32位微架构的"指令集体系结构与编程环境"; Intel 64(位) 架构(指令集体系结构与编程环境)是 Intel 的32位与64位架构的超集,它兼容 IA-32 架构.

NOTATIONAL CONVENTIONS

符号约定

This manual uses specific notation for data-structure formats, for symbolic representation of instructions, and for hexadecimal and binary numbers. This notation is described below.

本手册将特定符号用于数据结构格式,指令的符号表示,以及16进制与2进制数.下面描述这些符号.

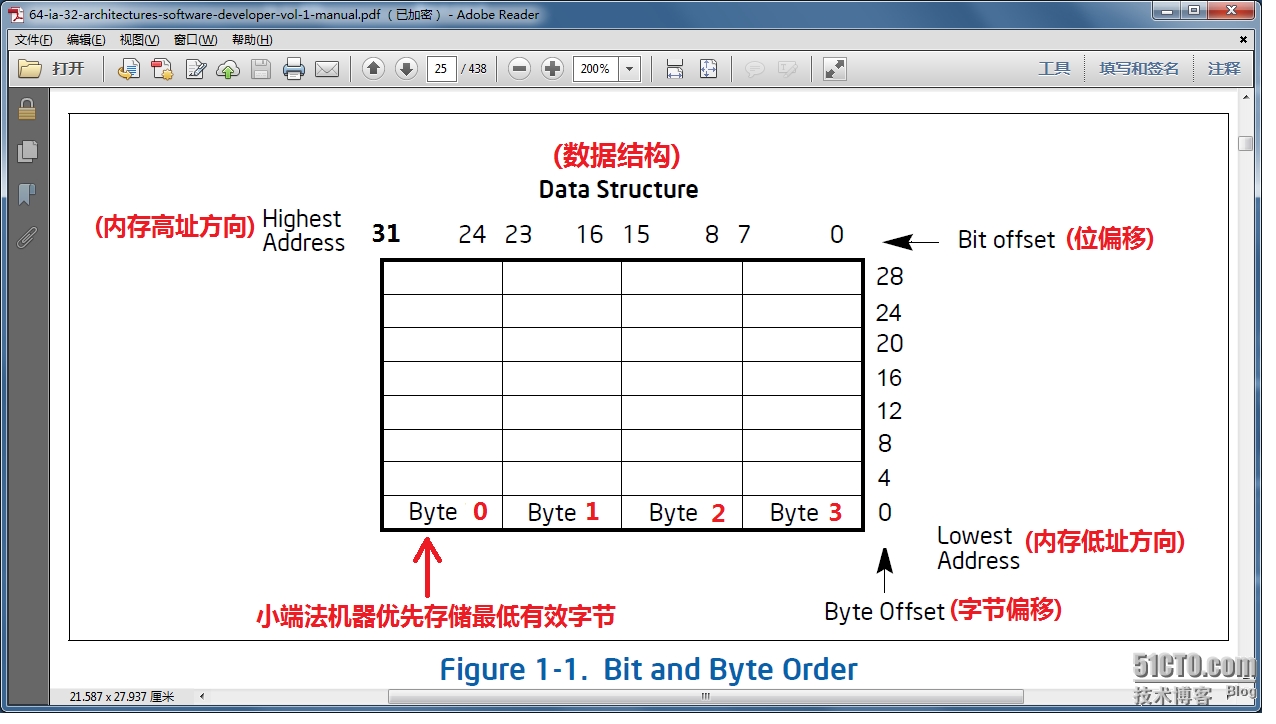

Bit and Byte Order

比特(位)与字节序

In illustrations of data structures in memory, smaller addresses appear toward the bottom of the figure; addresses

increase toward the top. Bit positions are numbered from right to left. The numerical value of a set bit is equal to two raised to the power of the bit position. Intel 64 and IA-32 processors are “little endian” machines; this means the bytes of a word are numbered starting from the least significant byte.

下面的插图示意了内存中的数据结构.更小的内存地址靠近图中的底端,内存地址朝着图中顶端增长.比特位从右向左编号.一组比特的数值等于2个提升阶级的比特位置?

Intel 64 与 IA -32 处理器属于"小端法"机器.这意味着一个"字"的字节,从最低有效字节开始编号。

(下图经我略微修改,因为原图中,位偏移的最左侧应该是31位,并且从最低有效字节即 byte 0 开始存储数据)

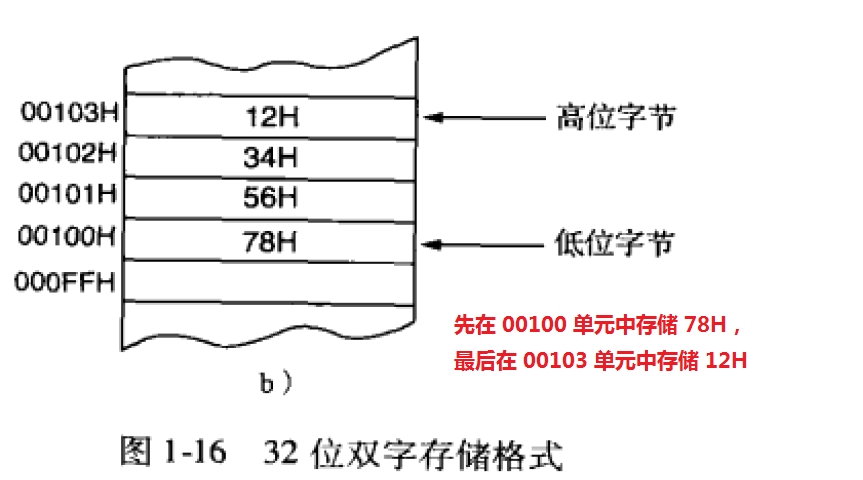

更直观的数据在内存中的存储形式参考下图,假设要存储16进制数(双字)12345678H,其中12是最高位字节;78是最低位字节,采用小端法存储时,这4字节的双字数据,占据4字节的连续内存地址段,12存储在最高的存储单元中,78存储在最低的存储单元中:

Reserved Bits and Software Compatibility

保留位与软件兼容性

In many register and memory layout descriptions, certain bits are marked as reserved. When bits are marked as reserved, it is essential for compatibility with future processors that software treat these bits as having a future,though unknown, effect. The behavior of reserved bits should be regarded as not only

undefined,but unpredictable.

Software should follow these guidelines in dealing with reserved bits:

在许多与寄存器和内存布局相关的描述中,某些位被标记为保留。保留位的行为不仅应该被视为“未定义”,还应该将其视为“不可预测的”。

软件在处理保留位时,应该遵循下面这些原则:

Do not depend on the states of any reserved bits when testing the values of registers that contain such bits.

Mask out the reserved bits before testing.

Do not depend on the states of any reserved bits when storing to memory or to a register.

Do not depend on the ability to retain information written into any reserved bits.

When loading a register, always load the reserved bits with the values indicated in the documentation, if any,

or reload them with values previously read from the same register.

1。当测试包含这些位的寄存器中值时,不要依靠任何保留位的状态。在测试前屏蔽掉保留位。

2。在存储至内存或寄存器中时,不要依靠任何保留位的状态。

3。即便保留位具备保留信息的能力,原则上不向其中写入任何数据

4。当加载寄存器时,总是加载有文档标示其值的保留位(如果有的话),或者用先前从同一个寄存器中读取的值来重载它。

NOTE

Avoid any software dependence upon the state of reserved bits in Intel 64 and IA-32 registers.

Depending upon the values of reserved register bits will make software dependent upon the unspecified manner in which the processor handles these bits. Programs that depend upon

reserved values risk incompatibility with future processors.

注意,在 Intel 64 与 IA -32 寄存器中,避免任何软件对保留位的依赖。取决于保留的寄存器位的值,这会让软件依赖处理器以不确定的方式处理这些位。

依赖保留值的程序将会带来与后续处理器不兼容的风险。

(译注: 也就是说,将来的处理器变更保留位的定义时,该软件在不同时期生产的处理器上运行,将表现出不同的行为)

Instruction Operands

指令的操作数

When instructions are represented symbolically, a subset of the IA-32 assembly language is used. In this subset,

an instruction has the following format:

label: mnemonic argument1, argument2, argument3

where:

A label is an identifier which is followed by a colon.

A mnemonic is a reserved name for a class of instruction opcodes which have the same function

The operands argument1, argument2, and argument3 are optional. There may be from zero to three operands, depending on the opcode. When present, they take the form of either literals or identifiers for data

items. Operand identifiers are either reserved names of registers or are assumed to be assigned to data items

declared in another part of the program (which may not be shown in the example).

当机器指令用符号表示时,使用 IA -32 汇编语言的子集, 其中一个指令的格式如下:

标签:助记符 参数1,参数2,参数3

其中:

标签是后面跟一个冒号的标识符; 助记符是用于一类具有相同功能的指令操作码的保留字。

参数1~3是操作数,它们是可选的。取决于(助记符表示的)操作码,可以有0~3个操作数。当存在操作数时,其形式要么是字面值,要么是数据项的标识符

操作数标识符要么是用于寄存器的保留字,要么假定分配给程序的其它部分声明的数据项目。

When two operands are present in an arithmetic or logical instruction, the right operand is the source and the left operand is the

destination.

For example:

LOADREG: MOV EAX, SUBTOTAL

In this example, LOADREG is a label, MOV is the mnemonic identifier of an opcode, EAX is the destination operand,and SUBTOTAL is the source operand. Some assembly languages put the source and destination in reverse order.

当一个算术或逻辑指令中存在2个操作数时,右侧的操作数是“源”,左侧的操作数是 “目的”

例如:

LOADREG: MOV EAX, SUBTOTAL

在上例中,LOADREG 是标签,MOV 是一个操作码的助记符,EAX是目的操作数,SUBTOTAL是源操作数。一些汇编语言将源和目的操作数以相反的顺序放置。

(译注: 例如AT&T风格的汇编指令)

Hexadecimal and Binary Numbers

16进制和2进制数

Base 16 (hexadecimal) numbers are represented by a string of hexadecimal digits followed by the character H (for example, 0F82EH). A hexadecimal digit is a character from the following set: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F.

Base 2 (binary) numbers are represented by a string of 1s and 0s, sometimes followed by the character B (for example, 1010B). The “B” designation is only used in situations where confusion as to the type of number might arise.

基本的16进制数,通过以大写字符H结尾的16进制数字字符串来表示(例如 0F82EH)。一个16进制数是以下集合中的一个字符:0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F

基本的2进制数,通过形如 1s 与 0s ,有时是字符B结尾的字符串来表示(1010B)。“B”后缀仅用于无法区分可能出现的数字类型的情况。

Segmented Addressing

分段寻址

The processor uses byte addressing. This means memory is organized and accessed as a sequence of bytes.

Whether one or more bytes are being accessed, a byte address is used to locate the byte or bytes memory. The range of memory that can be addressed is called an address space.

处理器使用字节寻址。这意味着内存被组织成按照字节顺序来访问。无论访问一个或多个字节,一个字节地址用于定位字节所在内存。可以寻址的内存范围叫做地址空间。注意,可用物理内存的实际数量并不总是等于地址空间的大小,换言之,并不是因为处理器有36条地址线就一定能够完全支持64GB的物理内存,它只是限定了能支持的物理内存上限为这么多。

The processor also supports segmented addressing. This is a form of addressing where a program may have many independent address spaces, called segments. For example, a program can keep its code (instructions) and stack in separate segments. Code addresses would always refer to the code space, and stack addresses would always

refer to the stack space. The following notation is used to specify a byte address within a segment:

Segment-register:Byte-address

处理器也支持分段寻址。这是当一个程序可能拥有许多独立的地址空间时,采用的寻址形式,它叫做分段。例如,一个程序可以在单独的分段中,保存它的代码(指令)与栈 。

代码地址将总是引用代码空间,而栈地址将总是引用栈空间。下面的符号用于指定一个内存分段中的字节地址。

Segment-register:Byte-address

For example, the following segment address identifies the byte at address FF79H in the segment pointed by the DS register:

DS:FF79H

The following segment address identifies an instruction address in the code segment. The CS register points to the code segment and the EIP register contains the address of the instruction.

CS:EIP

例如。下面的分段地址标识出,DS寄存器指向的分段基址中,偏移为FF79H处的字节。

DS:FF79H

某些软件和调试器在内部将这种标识法称为Far Pointer,即远指针。

下面的分段地址标识出一个在代码段中的指令的地址。CS 寄存器指向代码(指令)段的基址,并且EIP寄存器包含了该指令的地址。

CS:EIP

(自己补充的内容:

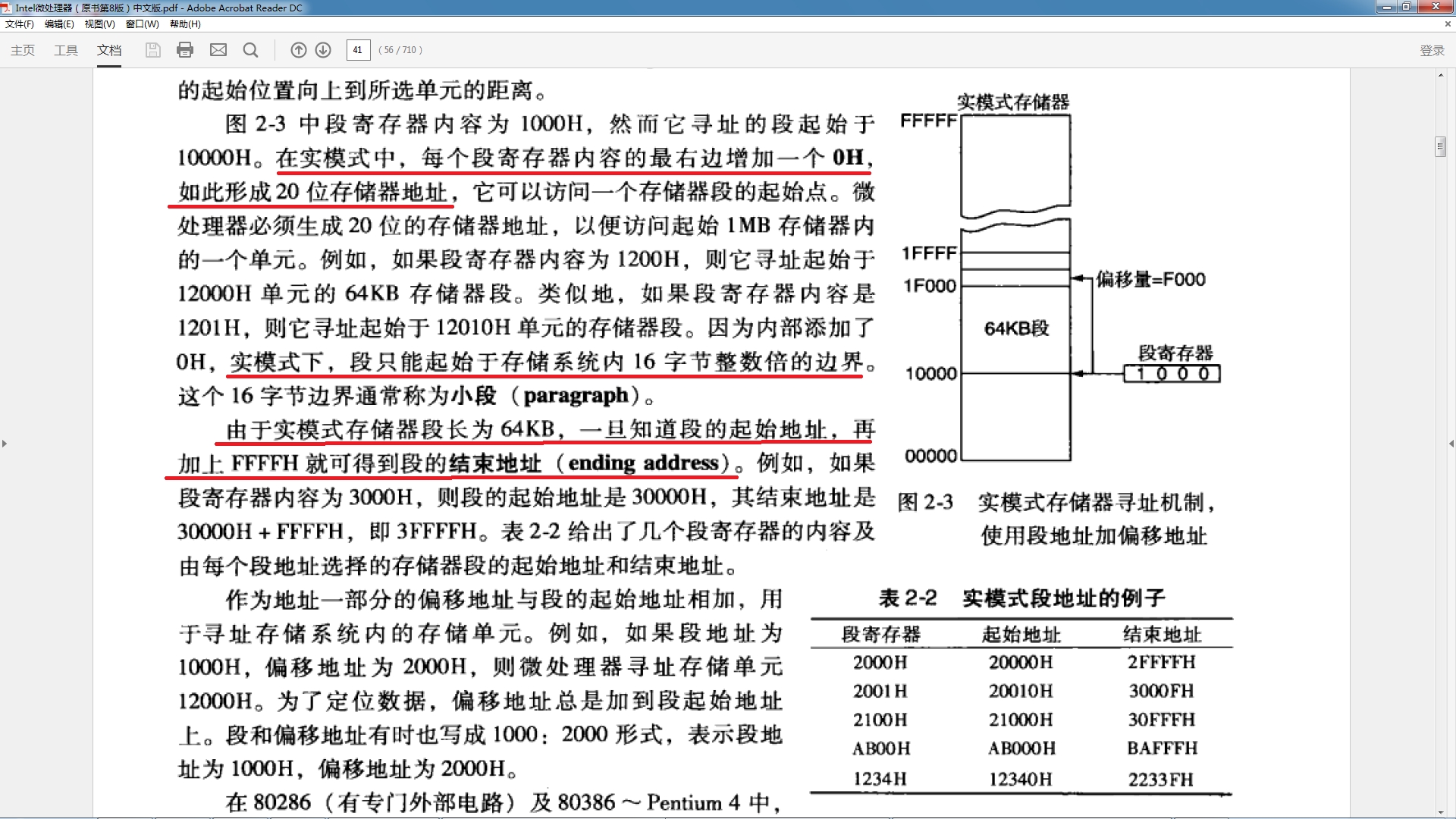

上面这种标识法为 段基址:段偏移量(segment:offset),这是16位实地址模式下的分段寻址,要把它转换为线性地址(16位寄存器支持20位地址空间),需要如下运算:

segment << 4 + offset ,即,用于寻址的最终物理地址等于段基址左移四位,再加上偏移量,例如下面的汇编代码:

shl DS, 4 ;将DS寄存器中保存的数据段基址左移4位,即 DS <<4 ,这等于乘以2的4次方=16=10hex

add DS, FF79h ;段偏移可以用8~32位的16进制立即数,或者通用寄存器,或[寄存器]形式的存储器寻址

假设DS的值为F000,则最终寻址为 F000 * 10h +FF79h = FFF79

实际的计算中,最简便的方法是直接在段基址的右侧加上一个16进制的 0h ,即得到16位段寄存器支持20位(1MBytes)地址空间的能力;即便如此,由于保存段偏移量的其它寄存器在8086/8088上也是16位的(如CS:IP,中的 IP 为 EIP 的16位形式;DS:BX,中的 BX 为 EBX 的 16位形式),这意味着“段限”为FFFF,或者64KB,以上面为例,数据段寄存器(DS)指向的实际数据段起始地址为 F0000,结束地址为 F0000+FFFF(64KBytes段限)= FFFFF,而最终寻址的内存单元为 FFF79,在该段范围内,是合法的。

要注意的是,各种处理器指令集体系结构(例如 intel 64与ia-32)包含各种运行模式(实模式,保护模式等)而实模式的内存分段管理与保护模式的内存分段管理有所不同,其中之一是,段寄存器中保存的段基址计算法不一样。

实模式与保护模式的差别主要体现在如下几个方面:

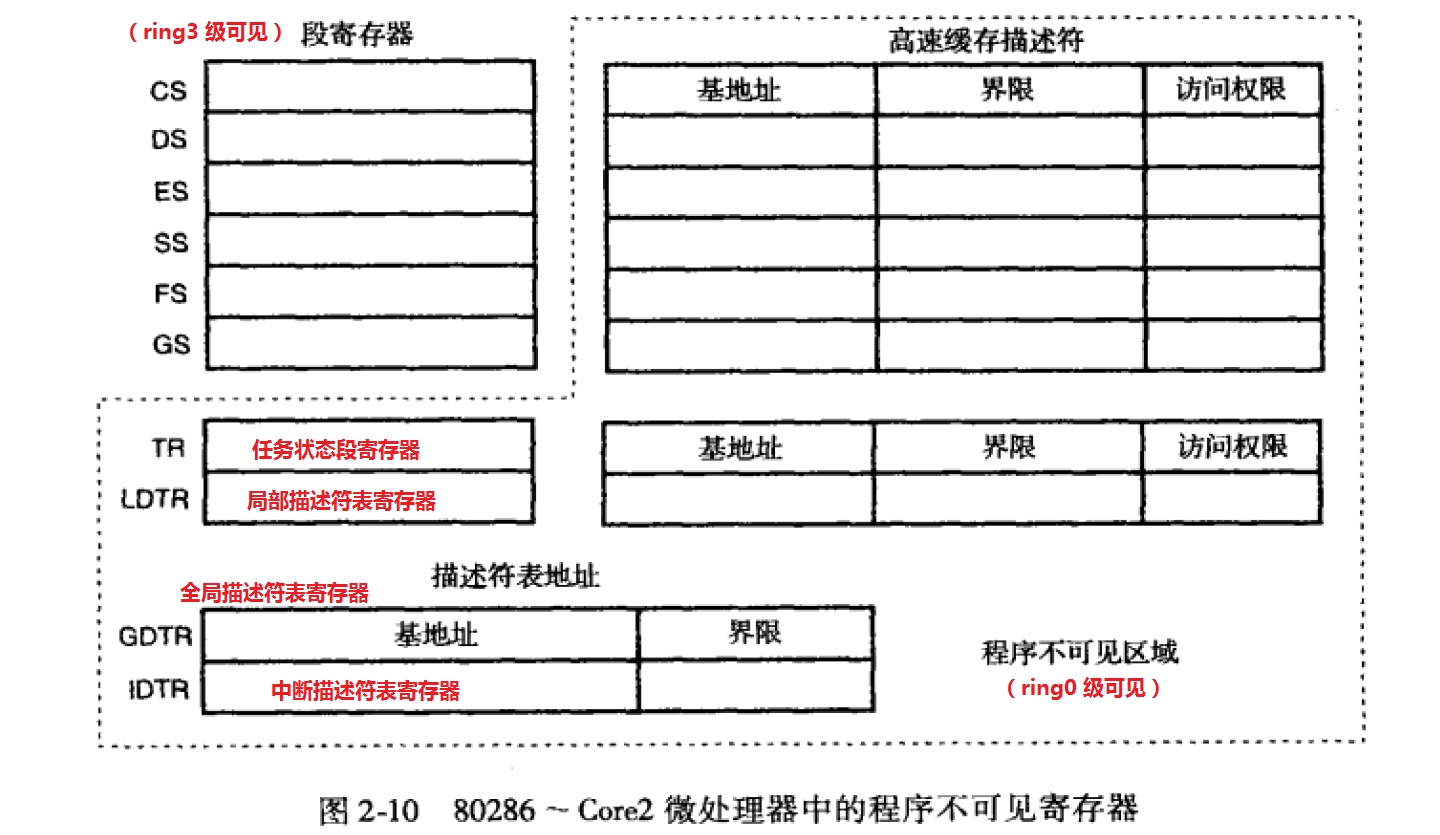

1。保护模式多了8个寄存器:5个控制寄存器(CR0~CR4),1个全局描述符表寄存器(GDTR),1个局部描述符表寄存器(LDTR),1个中断描述符表寄存器(IDTR)

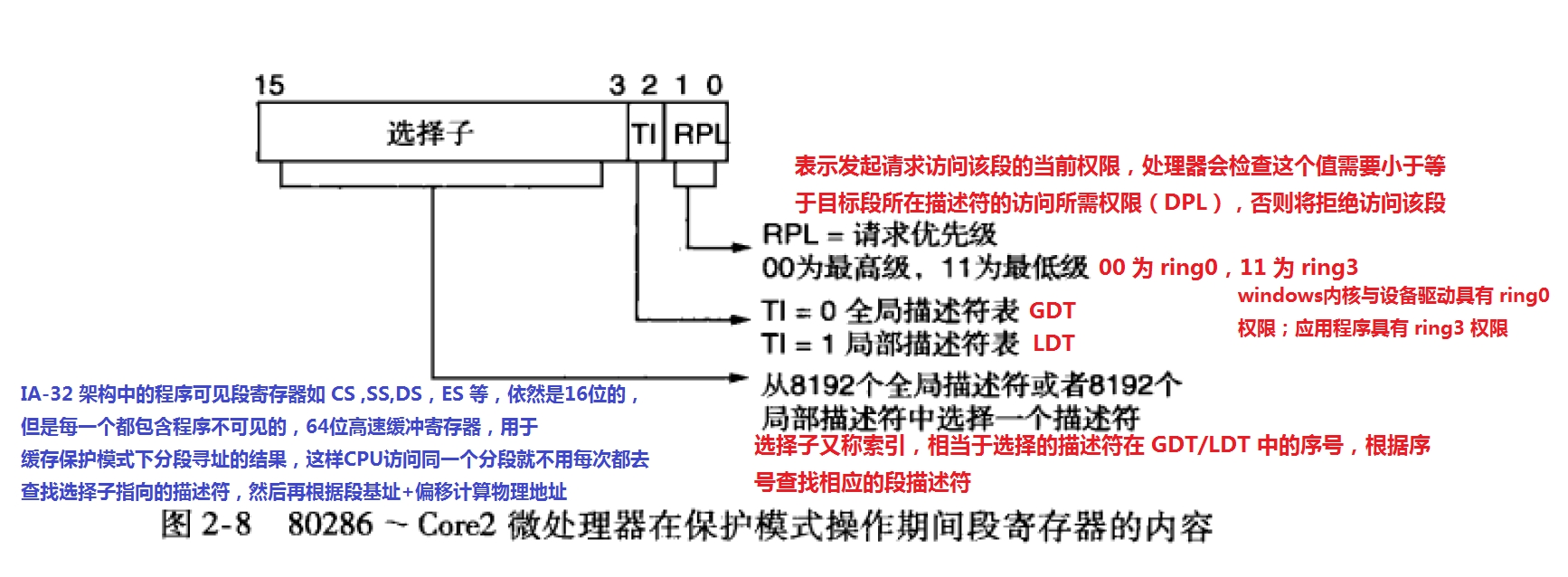

2。保护模式中,除了6个保存段选择符(子)的段寄存器:CS,DS,SS,ES,FS,GS 仍旧为16位外,其余寄存器多数为32位;GDTR,IDTR为48位;LDTR为16位;实模式下的所有寄存器均为16位

3。保护模式在寄存器和指令上引入了特权概念(ring0~ring3),由此衍生出用户

可见寄存器(ring3可见)与用户不可见寄存器(ring0可见),以及特权指令,段的特权检查等概念。所有这些都是实模式不具备的。

4。实模式中的段寄存器保存的就是某个段在物理内存中的基地址;保护模式中的段寄存器(bit 15~3)保存的是一个到GDT或LDT中,某个段描述符的索引,这个索引又称段选择符,而实际的32位段基地址保存在64位段描述符中的特定域(bit)中,后面会详解其结构。

5。IA-32(x86)处理器在加电初始化时,以及DOS操作系统,都运行在16位实模式下,这就是可以用DOS引导盘启动IA-32机器的原因。

另外,下面会讲到,8086/8088的地址总线为20位,从A0(第1根地址线)~A19(第20根地址线),如果段寄存器中的段基址为FFFF,偏移地址为FFFF,则实际寻址的内存单元为 FFFF0 + FFFF = 10FFEF = 1.1 MBytes,超过了 8086/8088 的 1MBytes 寻址上限,此时最前面的“1”,需要A20(第21根地址线)才能表示,而 8086/8088 最高到A19 地址线,因此这个1无效,最终产生的寻址单元为0FFEF=FFEF;相反,在80286及其后续处理器中,地址总线从24位起跳,因此可以通过汇编指令,在16位实模式下启用A20地址线,从而支持寻址

超过1MBytes的存储单元。

)

地址线是一组连接处理器和它的随机访问存储器(RAM)芯片的电线,每条地址线在给定字节的地址中占用一个单独的比特,例如IA-32处理器默认使用32条地址线,这意味着它使用32位地址寻址RAM中的每个字节。

下面为实模式分段寻址机制更详细的文字图解,摘录自《Intel微处理器,原书第8版》

32位保护模式分段寻址下的段寄存器结构:

因为段寄存器中的选择子能够从GDT中选择8192个描述符的任一个,而每个描述符长度为8字节,因此整个GDT的长度为 8 * 8192 = 65536 字节(近似为64KBytes);并且GDTR(全局描述符表寄存器,用于存储GDT的基址,通过x86汇编指令 lgdt/sgdt 分别可以将指向GDT基址的指针和GDT的界限从内存加载到GDTR / 将GDTR中的GDT基址指针,界限写入至内存;GDT基址指针和界限在加载到GDTR前,可由汇编程序员指定,界限不能超过16位,或2个16进制数FFFF,即10进制的65535)中的GDT界限字段为16位(0~15),决定了GDT的大小,以字节为单位,这解释了GDT最大只能为65536字节的原因(2的16幂=65536);GDTR中的高32位(47~16)存储GDT的第一个字节的起始地址。

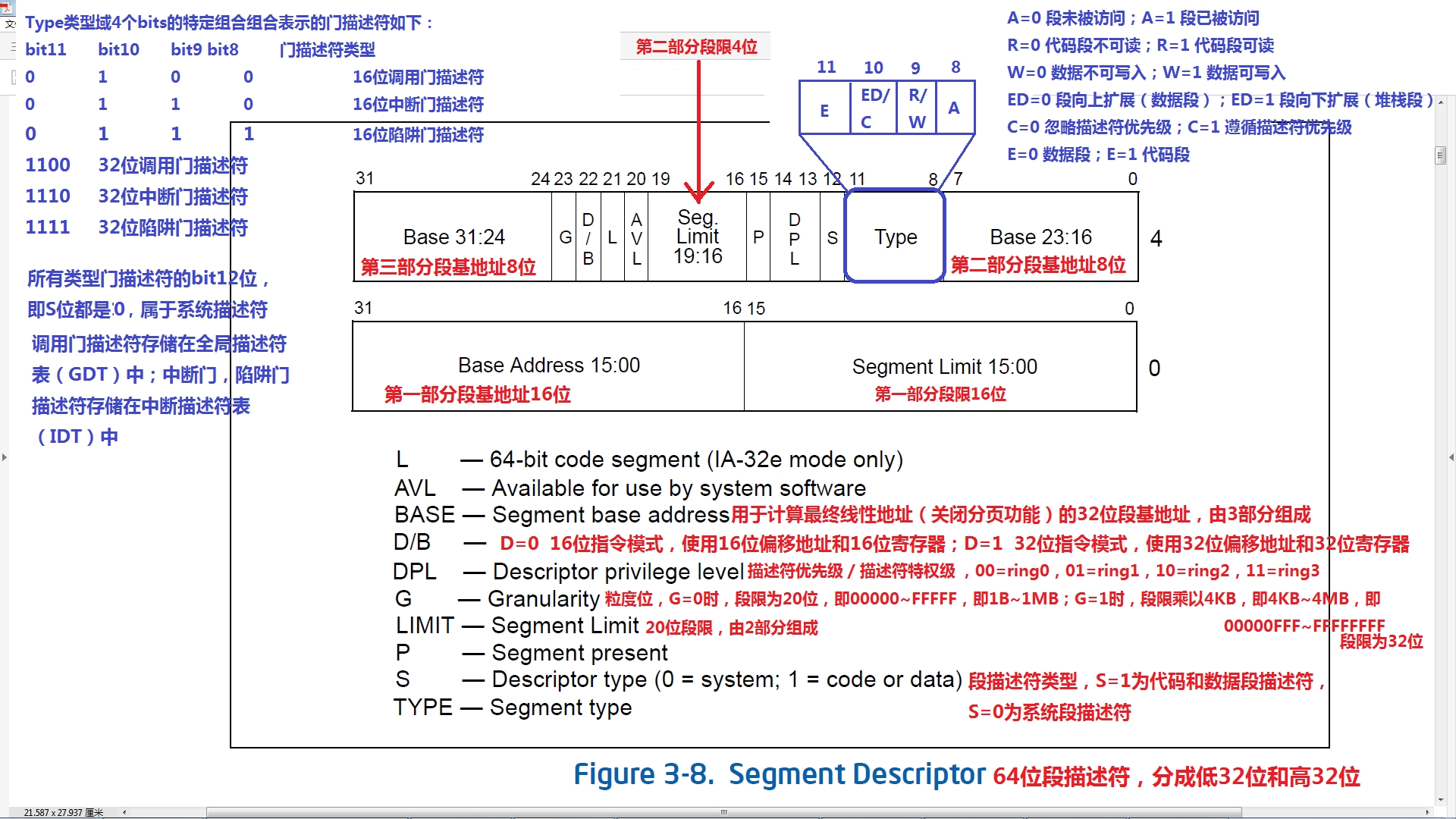

DPL(描述符优先级或描述符特权级):位于64位段描述符(内存中)的 bit 14~13位(64位段描述符通常用2个32位表示,DPL 域占用高32位中的14~13位)

RPL(请求优先级或请求特权级):位于16位段选择符(段寄存器中)的 bit 1~0位

另外,上述16位段限仅适用于80286处理器,从80386~Pentium4 的这些32位处理器,使用20位的段限,即FFFFF,或者10进制的1048575,即段限为1MBytes,

并且从80386开始,在段描述符中添加了G字段(在Intel 64体系结构中为bit 55),当G=0时,20位的段限以“字节”为单位,其值不变;当G=1时,20位的段限以“4K 字节”为单位,需要在原始段限后添加“FFF”,换算成实际的段限,例如,当G=1,段限为FFFFF时,实际段限为FFFFFFFF,即4GBytes(一个段的最大长度);再看一个例子,假设一个段描述符的基址为10000000,界限为001FF,G=1,则该段的结束地址为10000000 + 001FFFFF = 101FFFFF,也就是说,加上偏移量后得出的线性地址(在没有开启分页的情况下就是物理内存地址)只能在10000000~101FFFFF之间寻址。

下图取自Intel开发者手册文档,略经修改,全面完整地解析了段描述符的结构:

上图中,系统段描述符(S=0)用于跳转到比当前执行任务(当前特权级或者CPL)更高特权级(值更小)的段。例如,当用户应用程序调用一个实现于ring0中的系统调用时,就必须使用系统段描述符。

执行 lgdt/sgdt 指令需要 ring0 级运行权限,如果是编写运行在裸机上的程序,由于没有操作系统强加的运行权限限制( ring3 级),因此可以直接使用该指令。

指令需要一个内存地址作为操作数,低16位是GDT界限,高32位是GDT基址指针:

lgdt [GDT_POINTER] GDT_POINTER: dw 3FFH ;界限 dd 200000h ;基址

上述汇编代码中的 GDT_POINTER 数据结构中的 dw (define word)用于定义2字节(16位)的字;

dd (define double word)用于定义4字节(32位)的双字;这符合指令对其操作数格式的要求。

上面讲到的保护模式寻址中的段寄存器及其高速缓冲寄存器;全局,局部描述符表寄存器;中断描述符表寄存器;任务状态段寄存器的程序员可见与不可见结构,总结如下图:

这里跳过对CPUID段落的翻译,请见谅。

Exceptions

异常

An exception is an event that typically occurs when an instruction causes an error. For example, an attempt to divide by zero generates an exception. However, some exceptions, such as breakpoints, occur under other conditions.

Some types of exceptions may provide error codes. An error code reports additional information about the error. An example of the notation used to show an exception and error code is shown below:

#PF(fault code)

This example refers to a page-fault exception under conditions where an error code naming a type of fault is reported. Under some conditions, exceptions that produce error codes may not be able to report an accurate code.

In this case, the error code is zero, as shown below for a general-protection exception:

#GP(0)

当一个指令引发错误时通常出现的事件叫做异常。例如,尝试除以零会产生异常。然而,某些异常,例如断点,在其它条件下出现。

某些类型的异常可能会提供错误代码。 错误代码报告关于该错误的附加信息。

下面是一个展示异常和错误代码的符号例子:

#PF(fault code)

上述例子引用了一个页面错误异常。它的产生条件是以报告的故障类型命名的错误代码。在某些条件下,生成错误代码的异常未必能够回报准确的代码。在这种情况下,错误代码为0

例如下面展示的通用保护异常

#GP(0)

一个产生#GP异常的例子是,在当前的 CPL 权限不足(CPL > IOPL,CPL通常用于指代程序当前执行代码所在代码段的特权级,也就是CS寄存器中储存的当前段选择符的RPL,并且应该与对应的内存中段描述符的DPL值相同或小于后者;特权或权限的判断标准是,较小的值拥有较高的特权,较大的值拥有较低的特权)的情况下,使用 STI 指令,尝试直接修改 EFLAGS 标志寄存器中的 IF 标志位(bits 9位,即中断标志位,用于控制处理器能否使用中断请求 INTR 引脚,当 eflags.IF == 1,则允许 INTR 引脚;当 eflags.IF == 0,则禁用 INTR引脚,后者将导致处理器忽略所有的中断请求?)

STI 指令等同于设置 eflags.IF = 1;CLI 指令等同于设置 eflags.IF = 0,如前所述,这两个指令需要 CPL <= IOPL ,即当前的 CPL 权限大于 IOPL 权限,才能正常执行,否则就会引发#GP异常!

在 ring0 (CPL == 0 ,CPL <= IOPL?)的实模式下,假设程序包含下述指令序列:

sti ret

在该过程(或函数)返回到调用者前,通过 STI 指令启用处理器的 INTR 引脚,假设在STI 指令成功执行后,执行 RET 指令前,正好产生外部中断,它会被延迟,直到执行 RET 指令返回后,才响应外部中断 ;但是如果使用2个 STI 指令,强制要求优先响应外部中断:

sti sti ret

那么在 RET 指令执行前若产生外部中断信号,则处理器会优先响应该中断。

保护模式分段模型下,什么时候进行特权级(权限)检查?

当与段描述符相对应的段选择符被加载到处理器的一个段寄存器中时。例如当一个程序试图访问另一个代码段(不在当前代码段),或者通过“段间”转移指令(下述)转移程序控制时,目标代码段的段选择符必须加载到CS寄存器中,而且其RPL或对应的段描述符的DPL值应该大于等于当前代码段CPL(即当前特权级高于目标代码段的访问所需特权级),如果不是这样,处理器会发现特权级违例,并产生一个通用保护异常。CS寄存器无法显式修改,只能通过转移指令INT,CALL,JMP,RET,IRET,SYSENTER,SYSEXIT 来隐式修改;其中,INT 和 IRET 是段间转移;CALL,JMP,RET 则根据指令的操作数格式,可能是段间或段内转移。

BRIEF HISTORY OF INTEL 64 AND IA-32 ARCHITECTURE

Intel 64 与 IA -32 架构简史

The following sections provide a summary of the major technical evolutions from IA-32 to Intel 64 architecture:

starting from the Intel 8086 processor to the latest Intel Core 2 Duo, Core 2 Quad and Intel Xeon processor 5300 and 7300 series.

Object code created for processors released as early as 1978 still executes on the latest processors in the Intel 64 and IA-32 architecture families.

下面的部分给出从 IA -32 架构到 Intel 64 架构的主要技术演进的概览:从 Intel 8086处理器开始,到最新的 ntel Core 2 Duo, Core 2 Quad 与 Intel Xeon 处理器 5300 与 7300 系列。专为早在1978年发布的处理器生成的目标代码依旧可以在最新的 Intel 64 与 IA -32 架构处理器上执行。(向后兼容)

(这里的内容是自行添加的,从网上搜集的在 Intel 8086 的 16 位微处理器以前的处理器进化史)

Intel 4004 :第一个微处理器,4位,可寻址 4096 个 4 位(半字节)宽的存储单元,因此实际能寻址 (4096 * 4) / 8 = 2KBytes 的地址空间,每秒执行5万条指令(50 KIPS),执行一条指令需要 0.00002 秒(指令周期为 20 微秒);

Intel 8008:8位,可寻址16KBytes 的地址空间,指令执行速度与 4004 相同;

Intel 8080:8位,可寻址64KBytes 的地址空间,每秒执行50万条指令,指令周期为 2 微秒;

Intel 8085:最后一个8位通用微处理器,每秒执行近77万条指令,指令周期为 1.3 微秒;

16-bit Processors and Segmentation (1978)

16位处理器与内存分段 (1978)

The IA-32 architecture family was preceded by 16-bit processors, the 8086 and 8088. The 8086 has 16-bit registers and a 16-bit external data bus, with 20-bit addressing giving a 1-MByte address space. The 8088 is similar to the 8086 except it has an 8-bit external data bus.

在 IA -32 架构之前的是16位处理器,即8086与8088。8086拥有16位的寄存器集和16位的外部数据总线,采用20位寻址(地址总线为20位),可寻址 1Mbyte 地址空间(2的20次方等于 1048576 bytes=1Mbyte,即寻址范围从00000~FFFFF)。 8088与8086类似,但是它的外部数据总线为8位。

注意,当我们讨论处理器是“几位”的时候,通常是指它的寄存器位数以及数据总线的位数,只有两者位数相同,处理器才能实际处理长度相符的数(整数或者浮点数),系统总线中,数据总线的位数与处理器位数一致,常见的有8位,16位,32位,64位等等。举个例子,只有8位寄存器和8位数据总线的8088要处理一个32位的整数,需要四个总线周期来执行传送,而32位的80386只需一个总线周期;

而地址总线的位数直接决定处理器能够寻址的地址空间(内存),它与处理器位数不太一致,例如20位,24位,32位,36位,40位等等。

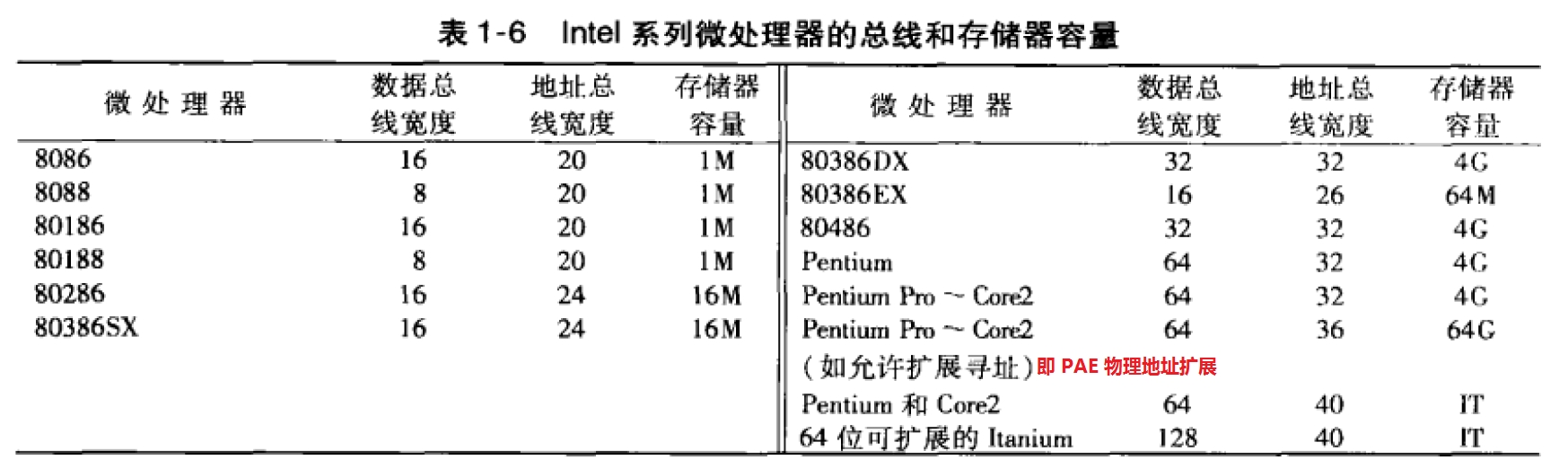

Intel 系列处理器(进化史上重要的主流产品)的数据总线,地址总线位数,能寻址的内存大小等信息总结如下:

(Intel 8086/8088 每秒执行250万条指令,即 2.5 MIPS,指令周期 400 纳秒)

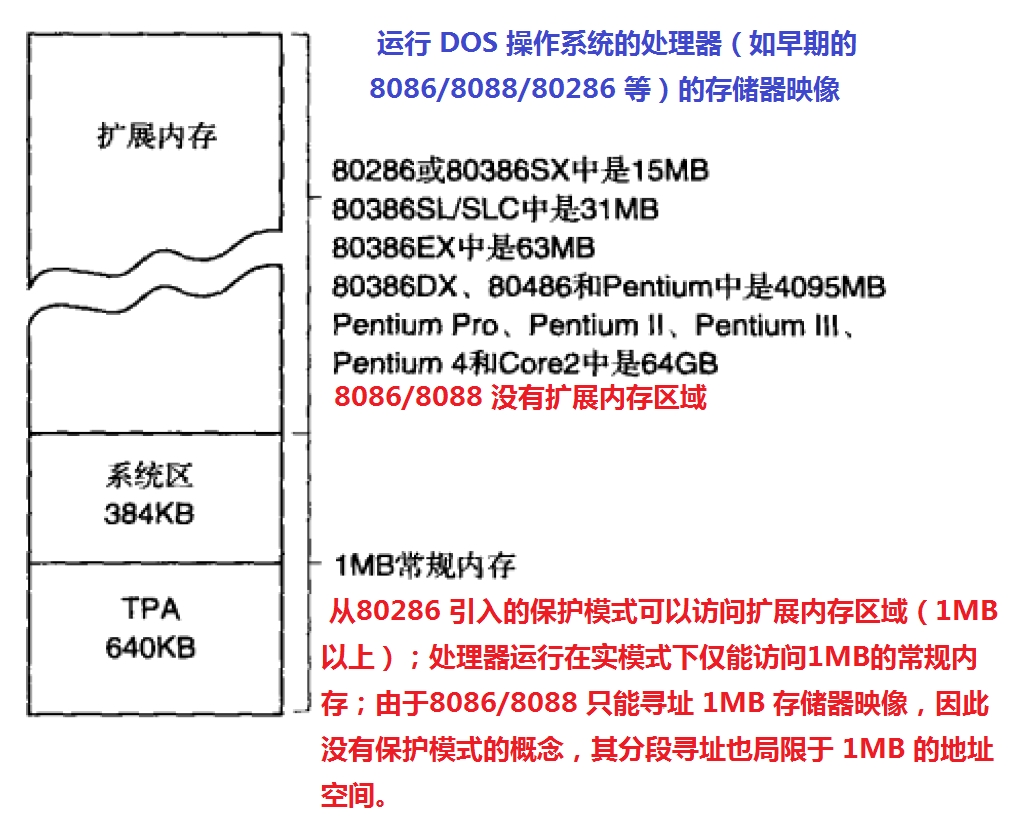

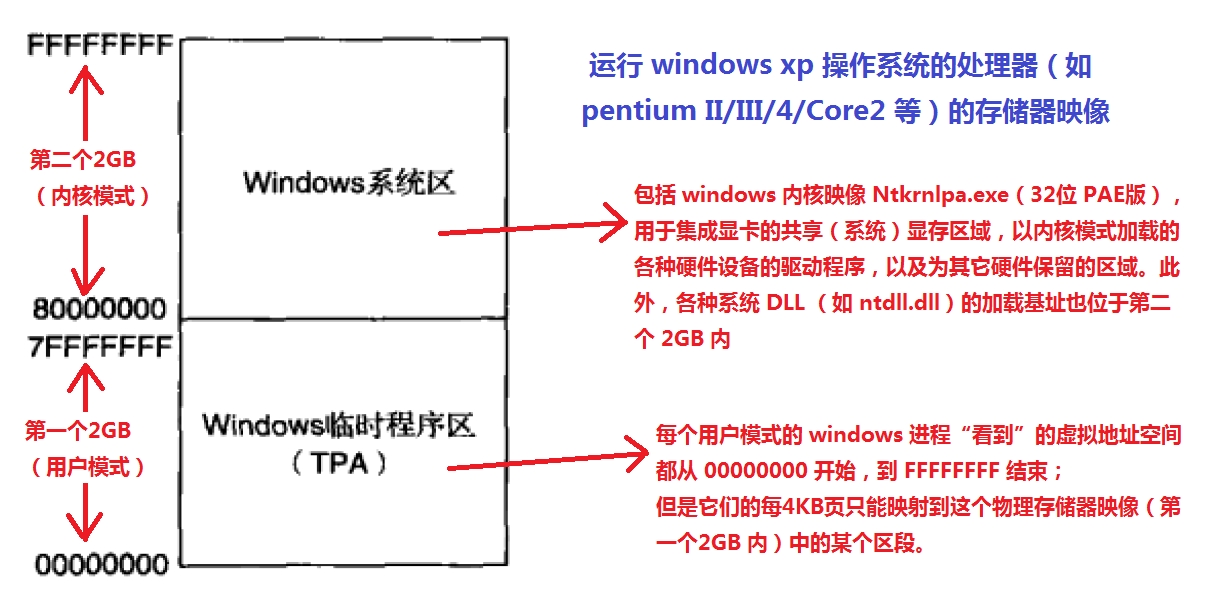

处理器能够寻址的地址空间可以看成是存储器映像,如下图:

The 8086/8088 introduced segmentation to the IA-32 architecture. With segmentation, a 16-bit segment register contains a pointer to a memory segment of up to 64 KBytes. Using four segment registers at a time, 8086/8088 processors are able to address up to 256 KBytes without switching between segments. The 20-bit addresses that can be formed using a segment register and an additional 16-bit pointer provide a total address range of 1 MByte.

8086/8088 引入了 IA -32 架构中使用的内存分段概念。通过分段,一个16位的段寄存器包含指向一个最多 64KBytes 的内存分段的指针。(2的16次方等于65536 bytes=64Kbytes)一次使用4个分段寄存器,8086/8088 有能力寻址最多256KBytes 的地址空间,而不用在分段之间切换。

8086的20位寻址原理是,使用(每)一个段寄存器与附加的16位指针,形成20位的地址总线, 提供总共1Mbytes的地址范围。

首次引入了 4~6 Bytes 的指令高速缓存硬件,为后续更大的高速缓存奠定发展基础;并且新增了乘法与除法指令

(IBM 于 1981 年推出的第一台 “PC”即采用了 8088 处理器)

The Intel 286 Processor (1982)

Intel 286 处理器 (1982)

The Intel 286 processor introduced protected mode operation into the IA-32 architecture. Protected mode uses the segment register content as selectors or pointers into descriptor tables. Descriptors provide 24-bit base addresses with a physical memory size of up to 16 MBytes, support for virtual memory management on a segment swapping

basis, and a number of protection mechanisms. These mechanisms include:

Segment limit checking

Read-only and execute-only segment options

Four privilege levels

Intel 286 处理器引入了保护模式。保护模式使用段寄存器上下文作为选择符或指针指向描述符表。

描述符提供24位基址空间,最多支持 16Mbytes 物理内存(2的24次方等于16777216Bytes=16MBytes),并且支持在分段交换基础上的虚拟内存管理机制,以及若干保护机制。这些机制包括:

1。段限制检查

2。只读和仅执行段选项

3。4个权限级别(ring0~ring3?)

( Intel 286 也称 80286,主频 8.0MHz,因此一个时钟周期为 125 纳秒,最快每秒可以执行400万条指令,即执行一条指令最少需要 250 纳秒,或者二个时钟周期)

The Intel386 Processor (1985)

Intel 386 处理器 (1985)

The Intel386 processor was the first 32-bit processor in the IA-32 architecture family. It introduced 32-bit registers for use both to hold operands and for addressing. The lower half of each 32-bit Intel386 register retains the properties of the 16-bit registers of earlier generations, permitting backward compatibility. The processor also provides a virtual-8086 mode that allows for even greater efficiency when executing programs created for 8086/8088 processors.

In addition, the Intel386 processor has support for:

A 32-bit address bus that supports up to 4-GBytes of physical memory

A segmented-memory model and a flat memory model

Paging, with a fixed 4-KByte page size providing a method for virtual memory management

Support for parallel stages

Intel 386 处理器是 IA -32 架构系列中的首个32位处理器。它引入了可以用于寻址以及作为操作数的32位寄存器。

(早期的 8086~80286是16位处理器,只能处理8位和16位数)

每个 32位 的 Intel 386 寄存器的下半部分(后2个字节)保留了前一代16位寄存器的属性,允许向后兼容。

该处理器也提供了虚拟8086的模式,从而允许在执行专为8086/8088处理器生成的程序(机器指令)时,获得更高的效率。

此外, Intel 386 处理器支持下述特性:

1。支持多达4GBytes 物理内存的32位地址总线。

2。同时支持分段内存模型与平坦内存模型。(即分段寻址与平坦寻址模式?Linux 与当前的 windows 均使用平坦寻址模式?)

3 。支持带有固定的 4KBytes 页面大小的分页机制,从而为虚拟内存管理提供了一种方法。

4 。支持并行阶段?

总结,Intel 386 处理器 (I386)引入的,并且至今仍在使用的重要特性:

32位地址空间,平坦寻址,虚拟8086模式(保护模式),这就是为什么gcc的默认编译设置,以及多数二进制rpm软件包选择了I386平台作为基本支持的原因。

The Intel486 Processor (1989)

The Intel 486 处理器 (1989)

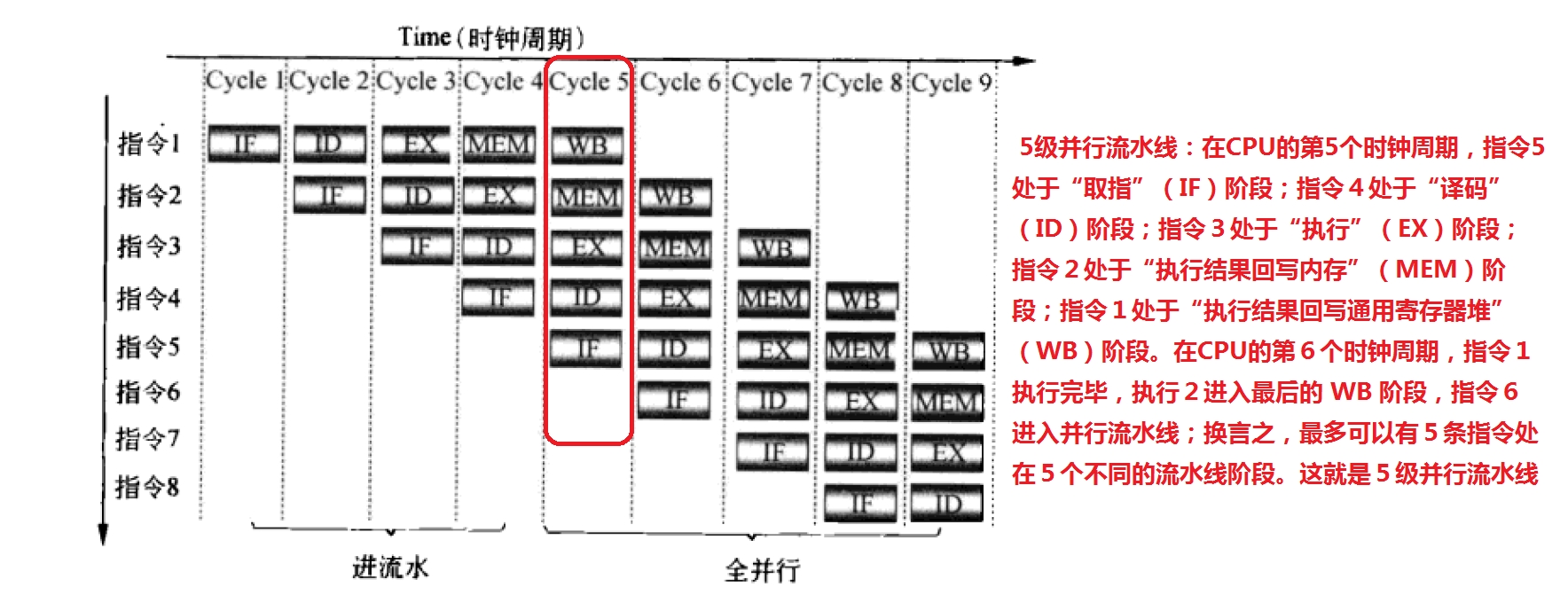

The Intel486 processor added more parallel execution capability by expanding the Intel386 processor’s instruction decode and execution units into five pipelined stages. Each stage operates in parallel with the others on up to five instructions in different stages of execution.

In addition, the processor added:

An 8-KByte on-chip first-level cache that increased the percent of instructions that could execute at the scalar rate of one per clock

An integrated x87 FPU

Power saving and system management capabilities

Intel 486 处理器通过将 Intel 386 处理器的指令译码与执行单元扩展到5条流水线阶段,增加了更强的并行执行能力。

每个阶段可以与其它在不同执行阶段的最多5条指令并行操作。

下图可以解释并行的5级流水线的工作模式:(该图取自《大话处理器》,略作修改,添加说明文字)

此外,该处理器增加了下述特性:

1。一个集成在芯片上的 8Kbytes L1高速缓存。这增加了每个以标率计算的时钟周期可以执行的指令百分比

2。芯片上集成一个 x87 浮点协处理单元(在此之前, 8087浮点协处理器作为独立的芯片与8086/8088处理器一起运作)

3。增加了节能和系统管理的能力。

(80486 主频从 50MHz 起跳,因此一个时钟周期“最长”为 20 纳秒,每秒执行5千万条指令,即 50MIPS,一个指令周期等于一个时钟周期,均为 20纳秒)

The Intel Pentium Processor (1993)

Intel Pentium(奔腾) 处理器 (1993)

The introduction of the Intel Pentium processor added a second execution pipeline to achieve superscalar performance

(two pipelines, known as u and v, together can execute two instructions per clock). The on-chip first-level cache doubled, with 8 KBytes devoted to code and another 8 KBytes devoted to data. The data cache uses the MESI protocol to support more efficient write-back cache in addition to the write-through cache previously used by the

Intel486 processor. Branch prediction with an on-chip branch table was added to increase performance in looping constructs.

In addition, the processor added:

Extensions to make the virtual-8086 mode more efficient and allow for 4-MByte as well as 4-KByte pages

Internal data paths of 128 and 256 bits add speed to internal data transfers

Burstable external data bus was increased to 64 bits

An APIC to support systems with multiple processors

A dual processor mode to support glueless two processor systems

A subsequent stepping of the Pentium family introduced Intel MMX technology (the Pentium Processor with MMX

technology). Intel MMX technology uses the single-instruction, multiple-data (SIMD) execution model to perform parallel computations on packed integer data contained in 64-bit registers.

Intel Pentium 处理器添加了第二条"执行"流水线,一共有2个执行单元,从而实现了超标量的性能(2条被称为u和v的流水线,每时钟周期可以同时执行两条指令,)

片上L1高速缓存的容量加倍:带有专门的8KBytes代码L1高速缓存与专门的8KBytes数据L1高速缓存。后者使用MESI协议,除了先前用于 Intel 486处理器的写直达缓存策略外,其支持更高效的回写缓存策略(译注:指专门的8KBytes数据L1高速缓存)。

添加了带有片上分支表(硬件)的分支预测能力,这可以提高处理循环结构(译注:相应的机器指令序列,等价于C 中的for,while等语句)的效率与性能。

此外,该处理器增加了下述特性:

1。扩展了虚拟的8086模式,使其运行起来更有效率,并且允许4MByte以及4KByte大小的分页。

2。128与256位的内部数据通道,用于加快内部数据传输。

3。突发传输式外部数据总线的带宽增加到64位

4。支持带有多处理器系统的APIC (Advanced Programmable Interrupt Controller,高级可编程中断控制器)

5。引入双处理器模式,从而无缝支持带2个处理器的系统

在Pentium处理器系列随后的发展脚步中,引入了Intel MMX技术(即,带有MMX技术的Pentium处理器)。

该技术用单条指令执行多数据流的模型(SIMD)做并行计算,计算对象是位于64位寄存器中打包的整型数据。

(Pentium 系列处理器内部的时钟频率从 60MHz 起跳,最高的版本为 233MHz,后者的一个时钟周期为 2.3 纳秒;处理器外部的64位数据总线的时钟频率为 60~66MHz,由此我们可以看到,早期的 Pentium 处理器受限于其微架构约束,数据在处理器内部的“流速”与在外部的速度不一致,这是整个计算机系统的性能瓶颈之一)

《补充资料》SIMD数据是指下面列出的数据类型:

1。最初的MMX指令处理的64位打包的整型数据;

2。SSE系列指令(SSE~SSE4.2)与AVX指令处理的128位“矢量浮点型”与“标量浮点型”数据,以及128位打包的整型数据;

3。AVX2指令(在第三代Intel Core I 系列微架构,即 Ivy Bridge 中引入)处理的256位打包的整型数据,以及256位“矢量浮点型”与“标量浮点型”数据;

下面着重介绍“打包的整型数据”格式,以SSE与AVX指令支持的128位打包的整型数据为例,其支持4种打包整型:

1。将16个“字节”打包成128位的整型数据;

2。将8个“字”打包成128位的整型数据;

3。将4个“双字”打包成128位的整型数据;

4。将2个“四字”(每个“四字”长64位)打包成128位的整型数据;

类似地,一条AVX2指令可以处理32个打包的字节,或者16个打包的字,或者8个

打包的双字,或者4个打包的四字,这就是单指令多数据流(SIMD)指令的由来。

The P6 Family of Processors (1995-1999)

P6系列的处理器(1995-1999)

The P6 family of processors was based on a superscalar microarchitecture that set new performance standards;

One of the goals in the design of the P6 family microarchitecture

was to exceed the performance of the Pentium processor significantly while using the same 0.6-micrometer,

four-layer, metal BICMOS manufacturing process. Members of this family include the following:

P6系列的处理器基于超标量微架构,从而树立了新的性能标准。

P6系列微架构的设计目标之一,是使用与Pentium处理器相同的0.6微米,四层金属BICMOS的制造工艺,但是生产性能要明显超越Pentium的处理器。

这个系列的成员包括以下处理器:

1。The Intel Pentium Pro processor is three-way superscalar. Using parallel processing techniques, the processor is able on average to decode, dispatch, and complete execution of (retire) three instructions per clock cycle. The Pentium Pro introduced the dynamic execution (micro-data flow analysis, out-of-order execution, superior branch prediction, and speculative execution) in a superscalar implementation.

The processor was further enhanced by its caches. It has the same two on-chip 8-KByte 1st-Level caches as the

Pentium processor and an additional 256-KByte Level 2 cache in the same package as the processor.

1。Intel Pentium Pro (奔腾专业版)处理器为三路超标量。使用并行处理技术,集成3个整数执行单元,使得处理器在每个时钟周期能够平均地译码,调度,并且完整的执行三条指令。

Pentium Pro 在一个超标量体系结构的实现中,引入了动态执行(包括微数据流分析,乱序执行,高级分支预测,猜测/预测执行)技术。

译注:某些指令涉及存储器访问操作,需要数十或数百个 CPU 时钟周期,顺序执行时,该指令后面的其它短周期指令(只需数个时钟周期)必须等待;如果这些短周期指令(数据传送,加法,减法等)不依赖于前面长周期指令的执行结果(不存在指令相关),那么就可以优先调度执行后面的指令,这就是乱序执行。乱序执行的前提是指令序列的全部或其中某部分不存在前后相关;编译器通常会尽可能去除指令的相关性来最大程度利用处理器的乱序执行特性,称为编译器对处理器流水线的优化。

猜测/预测执行(speculative execution,又叫“投机执行”)是指在分支预测时,跳转到某个程序分支的概率很高,那么就预先执行从该分支处开始的不相关的指令序列,即使此刻还没有实际执行跳转指令。

Pentium Pro 进一步增强了它的高速缓冲存储器。

它与Pentium处理器一样带有2个片上分立(指令与数据分离)的 8KByte L1高速缓存,并且在同一个处理器封装芯片内部添加了 256KByte 的L2 高速缓存。(指令与数据合并)

2。The Intel Pentium II processor added Intel MMX technology to the P6 family processors along with new packaging and several hardware enhancements. The processor core is packaged in the single edge contact cartridge (SECC). The Level l data and instruction caches were enlarged to 16 KBytes each, and Level 2 cache sizes of 256 KBytes, 512 KBytes, and 1 MByte are supported. A half-frequency backside bus connects the Level 2 cache to the processor. Multiple low-power states such as AutoHALT, Stop-Grant, Sleep, and Deep Sleep are supported to conserve power when idling.

2。Intel Pentium II (奔腾2)处理器以新的封装与硬件增强特性,向P6系列处理器添加了 Intel MMX 技术。该处理器的核心被封装在一个单边接触盒(SECC)中。

分立的 L1 指令与数据高速缓存都扩大到了 16 KBytes,并且 L2 高速缓存的容量有 256KByte,512KByte,以及 1 MBytes 三种版本可供选择。

一个只有处理器 1/2 运行频率的后端总线将 L2 高速缓存连接到处理器(译者注 :Intel 处理器发展史上,唯一没有将 L2 Cache 集成到处理器核心内部,且区分前端与后端总线的型号)。

诸如 AutoHALT, Stop-Grant, Sleep, 以及 Deep Sleep 等多个低功耗状态支持在处理器闲置时的节能特性。

3。The Pentium II Xeon processor combined the premium characteristics of previous generations of Intel processors. This includes: 4-way, 8-way (and up) scalability and a 2 MByte 2nd-Level cache running on a fullfrequency

backside bus.

3。Pentium II Xeon (奔腾2至强处理器)

结合了前一代 Intel处理器的特色,包含:4路或者8路(以及更多)超标量,以及一个2MB的L2高速缓存,通过与处理器运行频率相等的后端总线连接到处理器。

4。The Intel Celeron processor family focused on the value PC market segment. Its introduction offers an integrated 128 KBytes of Level 2 cache and a plastic pin grid array (P.P.G.A.) form factor to lower system design cost.

4。Intel Celeron (赛扬处理器)系列,侧重在PC市场的(低端)划分,引进的赛扬处理器提供了片上集成的128KB L2高速缓存,以及一个塑料引脚网格阵列(P.P.G.A),从而降低系统设计的成本。

5。The Intel Pentium III processor introduced the Streaming SIMD Extensions (SSE) to the IA-32 architecture.

SSE extensions expand the SIMD execution model introduced with the Intel MMX technology by providing a new set of 128-bit registers and the ability to perform SIMD operations on packed single-precision floatingpoint values

5。Intel Pentium III (奔腾3处理器)

在 IA-32体系结构中,引入了“流式”单指令多数据扩展

(Streaming SIMD Extensions ,SSE)。

SSE通过提供一组新的128位寄存器,以及对一个打包的单精浮点数执行SIMD操作的能力,延伸扩展了 Intel MMX 技术引入的SIMD执行模型。

(翻译起来很绕,SSE指令的本质就是将MMX的SIMD模型中,支持的64位打包整型数,扩展到128位,并且加入对128位打包的单精度浮点数的处理支持,可以参考前面的补充资料)

The Intel Pentium 4 Processor Family (2000-2006)

Intel Pentium 4 (奔腾4处理器)系列 (2000-2006)

The Intel Pentium 4 processor family is based on Intel NetBurst microarchitecture; see Section 2.2.2, “Intel

NetBurst Microarchitecture.”

The Intel Pentium 4 processor introduced Streaming SIMD Extensions 2 (SSE2); see Section 2.2.7, “SIMD Instructions.”

The Intel Pentium 4 processor 3.40 GHz, supporting Hyper-Threading Technology introduced Streaming

SIMD Extensions 3 (SSE3); see Section 2.2.7, “SIMD Instructions.”

Intel 64 architecture was introduced in the Intel Pentium 4 Processor Extreme Edition supporting Hyper-Threading

Technology and in the Intel Pentium 4 Processor 6xx and 5xx sequences.

Intel Virtualization Technology (Intel VT) was introduced in the Intel Pentium 4 processor 672 and 662.

Intel 奔腾4处理器系列基于 Intel NetBurst 微架构,引入了“流式”单指令多数据扩展第二代(SSE2),主频 3.40 GHz(一个处理器时钟周期短于三分之一纳秒);该系列支持超线程的产品则引入了第三代“流式”单指令多数据扩展指令集。

在 Intel 奔腾4处理器极限版中,引入了 Intel 64 位体系结构,并且支持超线程技术,产品序号为 6xx 与 5xx;在产品序号为 672 和 662 的 Intel 奔腾4处理器中,引入了 Intel 虚拟化技术(Intel VT)

The Intel Xeon Processor (2001- 2007)

Intel Xeon (至强处理器) (2001- 2007)

Intel Xeon processors (with exception for dual-core Intel Xeon processor LV, Intel Xeon processor 5100 series) are

based on the Intel NetBurst microarchitecture; see Section 2.2.2, “Intel NetBurst Microarchitecture.” As a family,

this group of IA-32 processors (more recently Intel 64 processors) is designed for use in multi-processor server

systems and high-performance workstations.

The Intel Xeon processor MP introduced support for Intel Hyper-Threading Technology; see Section 2.2.8, “Intel

Hyper-Threading Technology.”

The 64-bit Intel Xeon processor 3.60 GHz (with an 800 MHz System Bus) was used to introduce Intel 64 architecture.

The Dual-Core Intel Xeon processor includes dual core technology. The Intel Xeon processor 70xx series

includes Intel Virtualization Technology.

The Intel Xeon processor 5100 series introduces power-efficient, high performance Intel Core microarchitecture.

This processor is based on Intel 64 architecture; it includes Intel Virtualization Technology and dual-core technology.

The Intel Xeon processor 3000 series are also based on Intel Core microarchitecture. The Intel Xeon

processor 5300 series introduces four processor cores in a physical package, they are also based on Intel Core

microarchitecture.

Intel 至强处理器系列(除了双核 Intel 至强处理器 LV,以及 Intel 至强处理器 5100 系列以外) ,基于 Intel NetBurst 微架构。

该系列中的 IA-32 处理器,以及最近的 64 位处理器,专为有多个处理器的服务器系统,以及高性能工作站设计的。

64 位 Intel 至强处理器主频 3.60 GHz (800MHz 的系统总线,一个总线周期1.25纳秒,还是比处理器内部慢上4倍多)

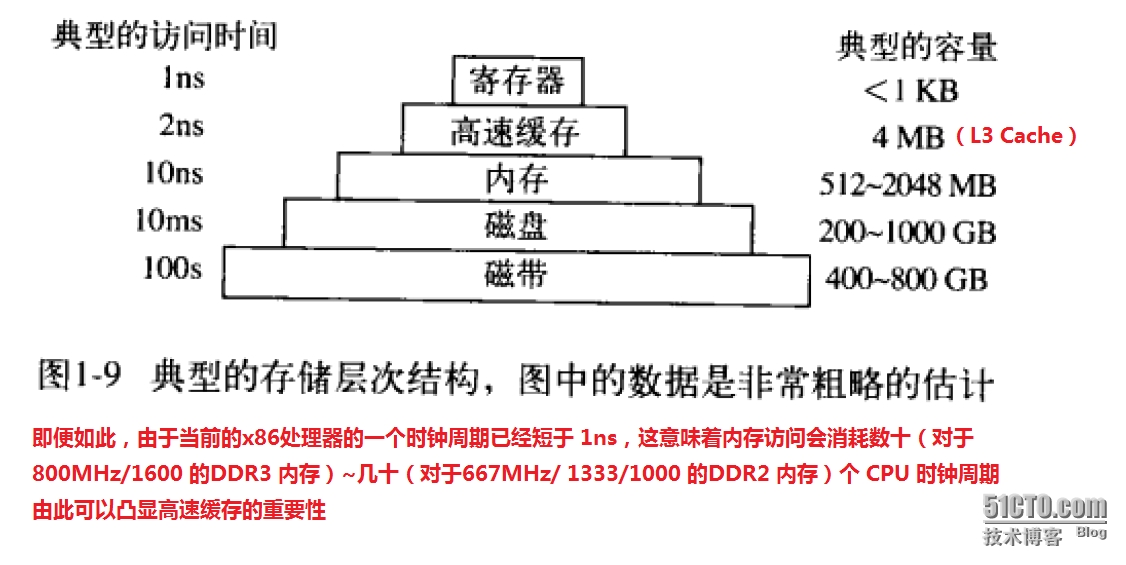

(译者补充:下图说明了CPU在访问工作频率与系统总线大致相等的内存时,为了等待数据/指令读写所延迟的时间)

使用了 Intel 64 位体系结构;双核 Intel 至强处理器引入了双核心技术; Intel 至强处理器 70xx 系列引入了 Intel 虚拟化技术。

Intel 至强处理器 5100 系列采用了低功耗,高性能的 Intel Core 微架构,并且基于 Intel 64 位体系结构,支持 Intel 虚拟化技术以及双核技术,并且在一个物理封装的芯片中集成了4个处理器核心。

The Intel Core Duo and Intel Core Solo Processors (2006-2007)

Intel Core Duo (酷睿双核) 与 Intel Core Solo (酷睿单核)处理器 (2006-2007)

The Intel Core Duo processor offers power-efficient, dual-core performance with a low-power design that extends

battery life. This family and the single-core Intel Core Solo processor offer microarchitectural enhancements over

Pentium M processor family.

Its enhanced microarchitecture includes:

Intel Smart Cache which allows for efficient data sharing between two processor cores

Improved decoding and SIMD execution

Intel Dynamic Power Coordination and Enhanced Intel Deeper Sleep to reduce power consumption

Intel Advanced Thermal Manager which features digital thermal sensor interfaces

Support for power-optimized 667 MHz bus

The dual-core Intel Xeon processor LV is based on the same microarchitecture as Intel Core Duo processor, and

supports IA-32 architecture.

Intel 酷睿双核处理器通过低功耗的设计,提供节能的双核性能,并且延长了电池的使用寿命;该系列以及单核的 Intel Core Solo 处理器采用了在 Pentium M 处理器系列的基础上,增强的微架构,包括:

Intel Smart Cache ,允许在处理器的2个核心之间高效地共享数据;

改进的指令译码与 SIMD 执行流水线;

Intel Dynamic Power Coordination 以及 Enhanced Intel Deeper Sleep ,用于降低功耗;

Intel Advanced Thermal Manager,其特点为数字热传感器接口;

支持功耗优化的 667 MHz 系统总线;

另外,上面提到的双核 Intel 至强处理器 LV ,基于与 Intel 酷睿双核处理器相同的微架构(即 Intel Core 微架构),并且支持 IA-32 体系结构。

The Intel Xeon Processor 5100, 5300 Series and Intel Core2 Processor Family (2006)

Intel Xeon (至强处理器)5100,5300系列,以及 Intel Core2 (酷睿2)处理器系列(2006)

The Intel Xeon processor 3000, 3200, 5100, 5300, and 7300 series, Intel Pentium Dual-Core, Intel Core 2 Extreme,

Intel Core 2 Quad processors, and Intel Core 2 Duo processor family support Intel 64 architecture; they are based

on the high-performance, power-efficient Intel Core microarchitecture built on 65 nm process technology. The

Intel Core microarchitecture includes the following innovative features:

Intel Wide Dynamic Execution to increase performance and execution throughput

Intel Intelligent Power Capability to reduce power consumption

Intel Advanced Smart Cache which allows for efficient data sharing between two processor cores

Intel Smart Memory Access to increase data bandwidth and hide latency of memory accesses

Intel Advanced Digital Media Boost which improves application performance using multiple generations of

Streaming SIMD extensions

The Intel Xeon processor 5300 series, Intel Core 2 Extreme processor QX6800 series, and Intel Core 2 Quad

processors support Intel quad-core technology.

Intel 至强处理器 3000,3200,5100,5300,7300系列;Intel 奔腾双核,Intel 酷睿2 极限版,Intel 酷睿2 四核,Intel 酷睿2 双核处理器系列,均支持 Intel 64位体系结构,并且基于高性能,

低功耗的 Intel Core 微架构,采用65纳米制程技术。Intel Core 微架构包含下述创新功能:

Intel Wide Dynamic Execution,用于提升性能与执行的吞吐量;

Intel Intelligent Power Capability,用于降低功耗;

Intel Advanced Smart Cache,允许在两个处理器的核心之间高效共享数据;

Intel Smart Memory Access ,用于增加内存访问的数据带宽,以及隐藏延迟

Intel Advanced Digital Media Boost,其通过使用多代的SSE(SSE,SSE2 ;,SSE3 。。。)扩展指令,改进了应用程序的性能;

Intel 至强处理器5300系列,Intel 酷睿2 极限版 QX6800 series,以及 Intel 酷睿2 四核处理器均支持 Intel 四核技术。

The Intel Xeon Processor 5200, 5400, 7400 Series and Intel Core2 Processor Family (2007)

Intel 至强处理器5200,5400,7400系列,以及Intel Core2 (酷睿2)处理器系列(2007)

The Intel Xeon processor 5200, 5400, and 7400 series, Intel Core 2 Quad processor Q9000 Series, Intel Core 2 Duo

processor E8000 series support Intel 64 architecture; they are based on the Enhanced Intel Core microarchitecture

using 45 nm process technology. The Enhanced Intel Core microarchitecture provides the following improved

features:

A radix-16 divider, faster OS primitives further increases the performance of Intel Wide Dynamic Execution.

Improves Intel Advanced Smart Cache with Up to 50% larger level-two cache and up to 50% increase in wayset

associativity.

A 128-bit shuffler engine significantly improves the performance of Intel Advanced Digital Media Boost and

SSE4.

Intel Xeon processor 5400 series and Intel Core 2 Quad processor Q9000 Series support Intel quad-core technology.

Intel Xeon processor 7400 series offers up to six processor cores and an L3 cache up to 16 MBytes.

Intel 至强处理器 5200, 5400, 7400 系列,Intel 酷睿2 四核 Q9000 系列,Intel 酷睿2 双核 E8000 系列,均支持 Intel 64位体系结构,并且基于采用45纳米制程技术的增强型Intel Core 微架构

增强型 Intel Core 微架构提供了下述改进:

以16为基数的一个除法器(?),更快的操作系统原语(?? ),极大的提高了原 ntel Core 微架构中的 Wide Dynamic Execution 技术的性能;

改善的 Intel Advanced Smart Cache ,2级高速缓存的容量提升多达50%;2级高速缓存增加多达50%的路组相联(逻辑电路);

新增一个 128位的排序引擎,显著地提升了原 Intel Core 微架构中的 Advanced Digital Media Boost 技术以及 SSE4 指令处理打包的128位数据时的性能;

Intel 至强处理器 5400 系列以及 Intel 酷睿2 四核 Q9000 系列支持 Intel 四核技术;

Intel 至强处理器 7400 系列提供了多达六个的处理器核心,以及一个高达16MBytes 的L3 高速缓存。

The Intel Corei7 Processor Family (2008)

Intel 酷睿 i7 处理器系列 (2008)

The Intel Core i7 processor 900 series support Intel 64 architecture; they are based on Intel microarchitecture

code name Nehalem using 45 nm process technology. The Intel Core i7 processor and Intel Xeon processor 5500

series include the following innovative features:

Intel Turbo Boost Technology converts thermal headroom into higher performance.

Intel HyperThreading Technology in conjunction with Quadcore to provide four cores and eight threads.

Dedicated power control unit to reduce active and idle power consumption.

Integrated memory controller on the processor supporting three channel of DDR3 memory.

8 MB inclusive Intel Smart Cache.

Intel QuickPath interconnect (QPI) providing point-to-point link to chipset.

Support for SSE4.2 and SSE4.1 instruction sets.

Second generation Intel Virtualization Technology.

Intel 酷睿 i7 900 系列支持 Intel 64位体系结构,基于开发代号为 Nehalem 的微架构,采用45纳米制程技术;Intel 酷睿 i7处理器以及 Intel 至强 5500系列处理器包含下述创新功能:

Intel 睿频加速技术,将热余量(? )转换成更高的性能;

4个物理核心结合 Intel 超线程技术,提供8线程(8个逻辑核心)的性能;

专用的电源控制模块,降低处理器在活动和闲置时的功耗;

处理器内部集成内存控制器,支持三通道的DDR3内存(第三代双倍数据速率同步动态随机访问存储器);

Intel QuickPath interconnect (QPI 总线),提供从处理器内部到主板芯片组之间的点对点链路;

支持 SSE4.2 以及 SSE4.1 指令集;

第二代 Intel 虚拟化技术。

2010 Intel Core Processor Family (2010)

2010 Intel 酷睿处理器系列(2010)

2010 Intel Core processor family spans Intel Core i7, i5 and i3 processors. They are based on Intel microarchitecture

code name Westmere using 32 nm process technology. The innovative features can include:

Deliver smart performance using Intel Hyper-Threading Technology plus Intel Turbo Boost Technology.

Enhanced Intel Smart Cache and integrated memory controller.

Intelligent power gating.

Repartitioned platform with on-die integration of 45nm integrated graphics.

Range of instruction set support up to AESNI, PCLMULQDQ, SSE4.2 and SSE4.1.

2010 Intel 酷睿处理器系列横跨 Intel 酷睿 i7,i5 以及 i3。它们均基于开发代号为 Westmere 的微架构,采用32纳米制程技术。

Westmere 微架构中创新的特色如下:

增强的超线程和睿频加速技术;

增强的 Intel Smart Cache(智能缓存)和集成内存控制器;

智能的“功率门控”;

在芯片上添加45纳米制程技术的集成显卡,重新划分了平台架构;

新增对 AESNI,PCLMULQDQ,SSE4.2 和 SSE4.1 等指令集的支持。

The Second Generation Intel Core Processor Family (2011)

第二代 Intel 酷睿处理器系列 (2011)

The Second Generation Intel Core processor family spans Intel Core i7, i5 and i3 processors based on the Sandy

Bridge microarchitecture. They are built from 32 nm process technology and have innovative features including:

Intel Turbo Boost Technology for Intel Core i5 and i7 processors

Intel Hyper-Threading Technology.

Enhanced Intel Smart Cache and integrated memory controller.

Processor graphics and built-in visual features like Intel Quick Sync Video, Intel InsiderTM etc.

Range of instruction set support up to AVX, AESNI, PCLMULQDQ, SSE4.2 and SSE4.1.

Intel Xeon processor E3-1200 product family is also based on the Sandy Bridge microarchitecture.

Intel Xeon processor E5-2400/1400 product families are based on the Sandy Bridge-EP microarchitecture.

Intel Xeon processor E5-4600/2600/1600 product families are based on the Sandy Bridge-EP microarchitecture

and provide support for multiple sockets.

第二代 Intel 酷睿处理器系列横跨 Intel 酷睿 i7,i5 以及 i3。它们均基于开发代号为 Sandy Bridge 的微架构,采用32纳米制程技术,包括下列创新特色:

(译注:其中有4项是在前几代产品中就已经引入的技术,根本谈不上创新)

用于酷睿 i7和 i5 的睿频加速技术;

超线程技术;

增强的智能缓存和集成内存控制器;

处理器内部的集成显卡以及内置的 Intel Quick Sync Video,Intel InsiderTM 等视频输出总线(?);

新增对AVX, AESNI,PCLMULQDQ,SSE4.2 和 SSE4.1 等指令集的支持;

Intel 至强处理器 E3-1200 系列同样基于Sandy Bridge 微架构;

Intel 至强处理器 E5-2400/1400 系列基于 Sandy Bridge-EP 微架构;

Intel 至强处理器 E5-4600/2600/1600 系列基于 Sandy Bridge-EP 微架构,并且支持多处理器插槽;

(接下来的产品系列,手册正文中并没有给出详细的介绍,因此这里只作简短的翻译)

The Third Generation Intel Core Processor Family (2012)

第三代 Intel 酷睿处理器系列 (2012)

基于 Ivy Bridge 微架构

The Fourth Generation Intel Core Processor Family (2013)

第四代 Intel 酷睿处理器系列 (2013)

基于 Haswell 微架构

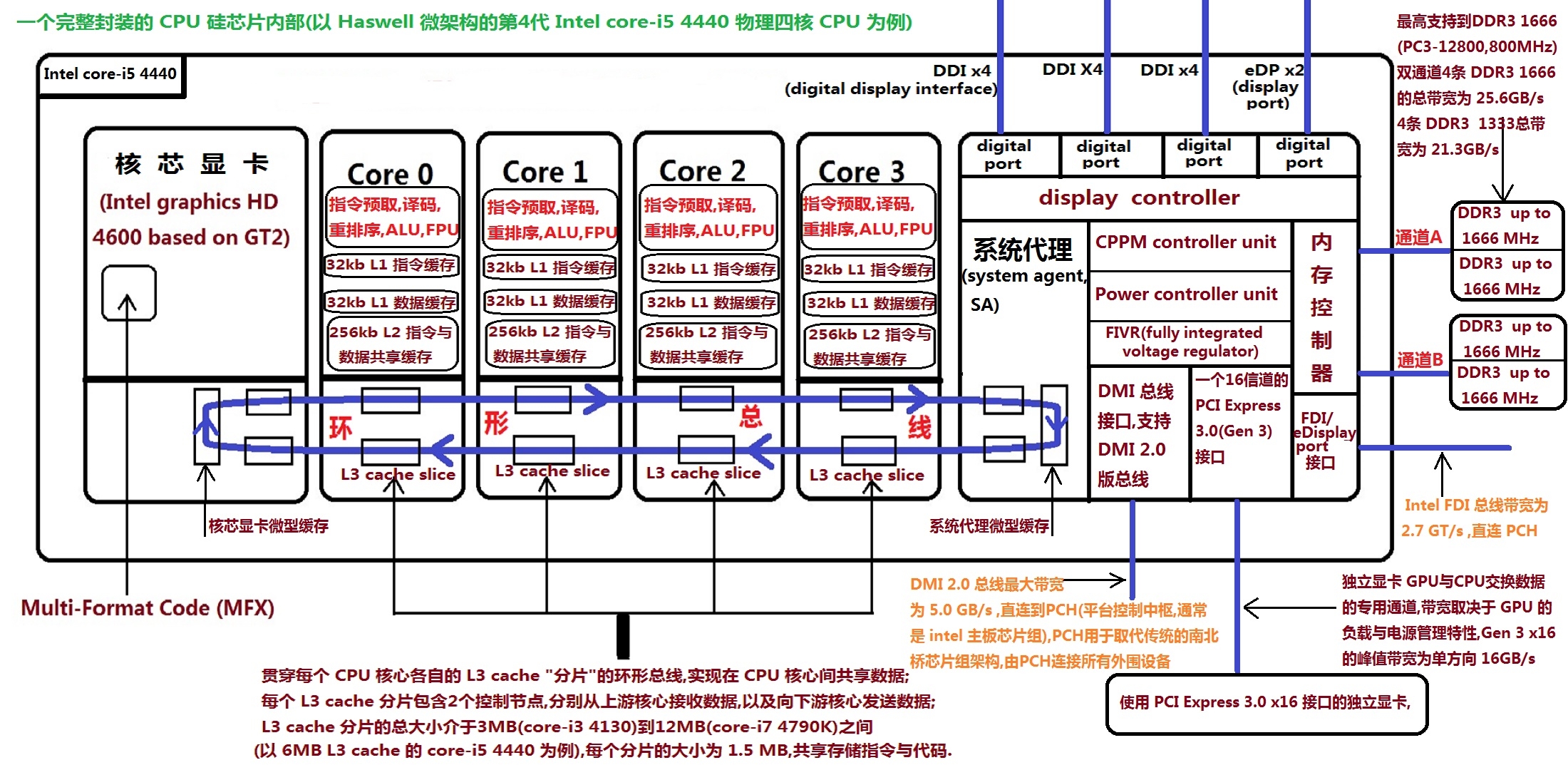

(下面这张图是我制作的,基于 Haswell 微架构的 Intel Core i5-4440 CPU 的内部详细视图,当然还没有深入到每个核心内部,但是通过这张图,大致能从整体上把握 Haswell 微架构的特点)

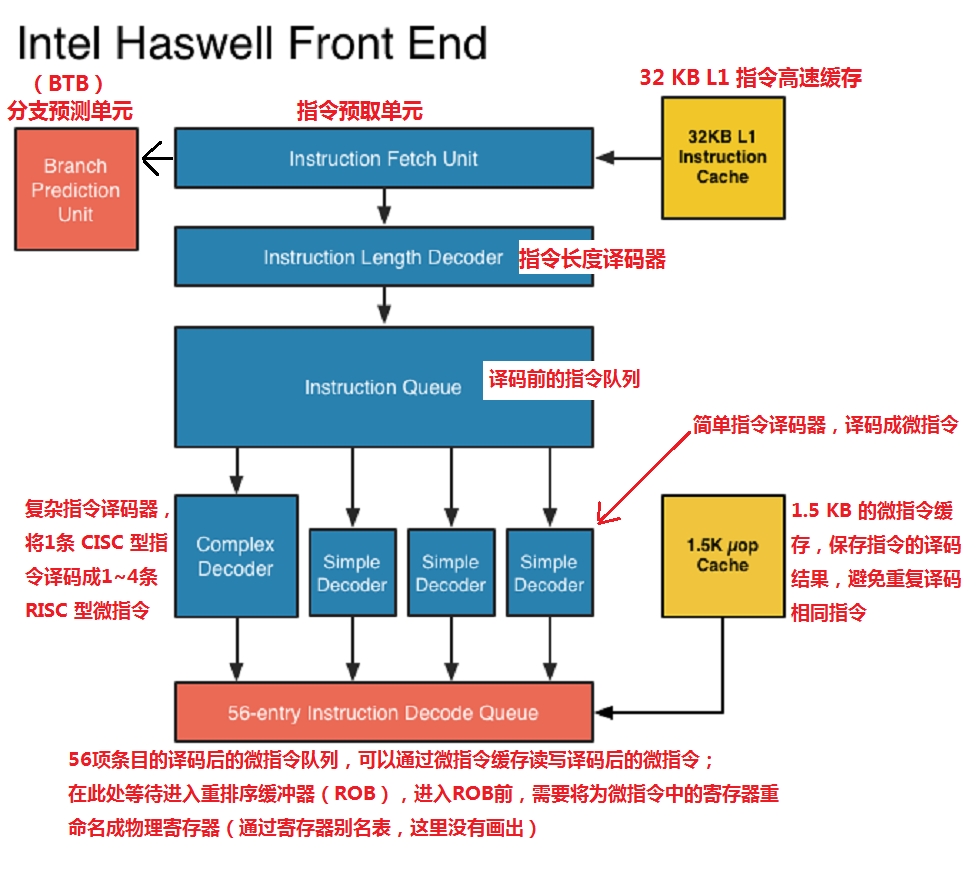

下面再深入到 Haswell 的每个 CPU 核心内部(也就是上图中的 core 0~3 内部),图片来自于 Intel 开发者论坛 2012,对其中的文字进行了翻译:

一,核心前端:(指令预取 & 分支预测 -> 译码 -> 寄存器重命名)

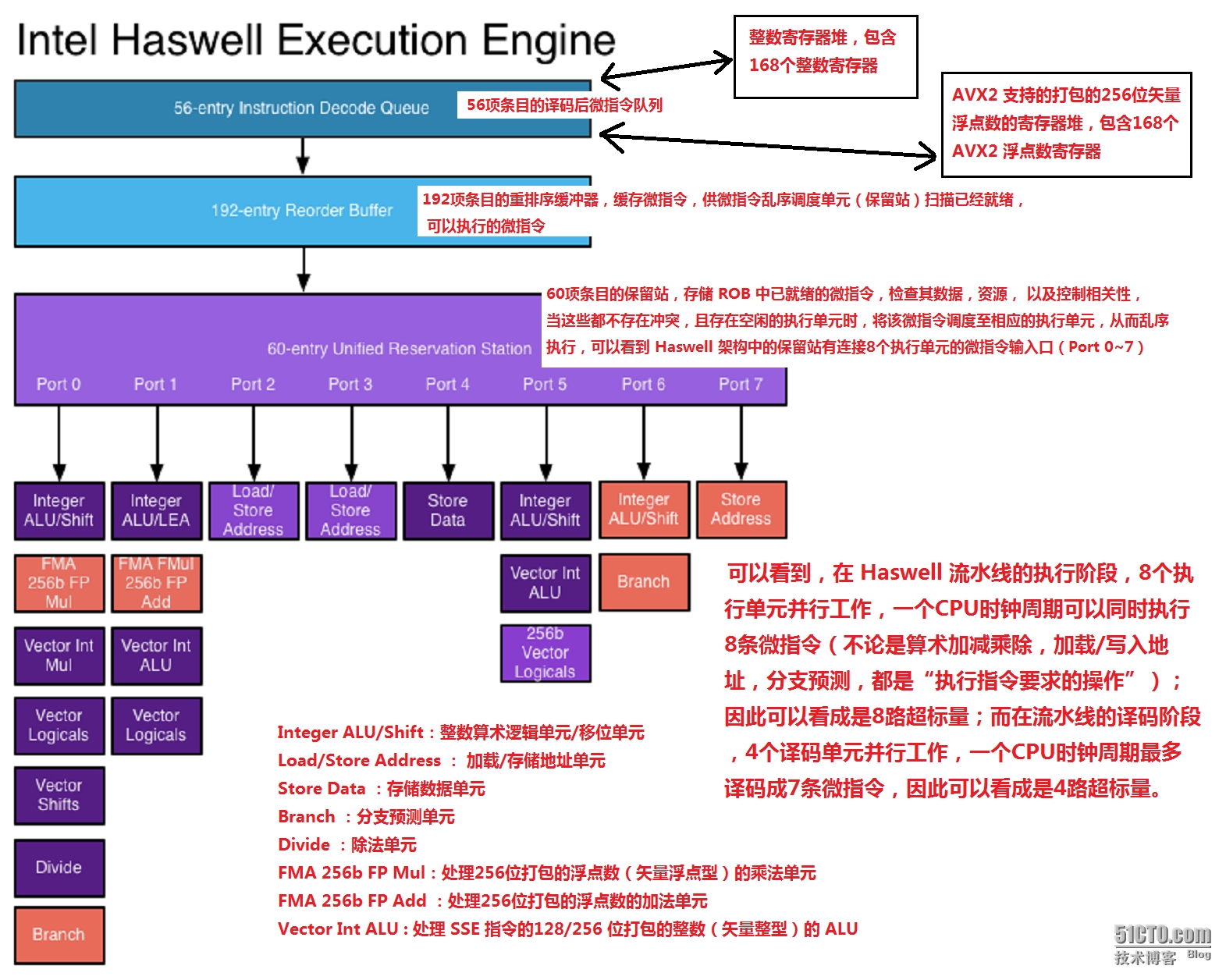

二,核心内部的执行引擎:(微指令重排序 -> 微指令乱序调度 -> 乱序执行)

注意,i5-4440 是物理4核的架构,假设没有任何一个核心处于闲置状态,那么每时钟周期的最大指令并行数为 8 * 4 = 32条微指令!这说明增加核心数量所带来的性能提升要高于增加时钟频率(等同于缩短每时钟周期花费的时间)所带来的性能提升。

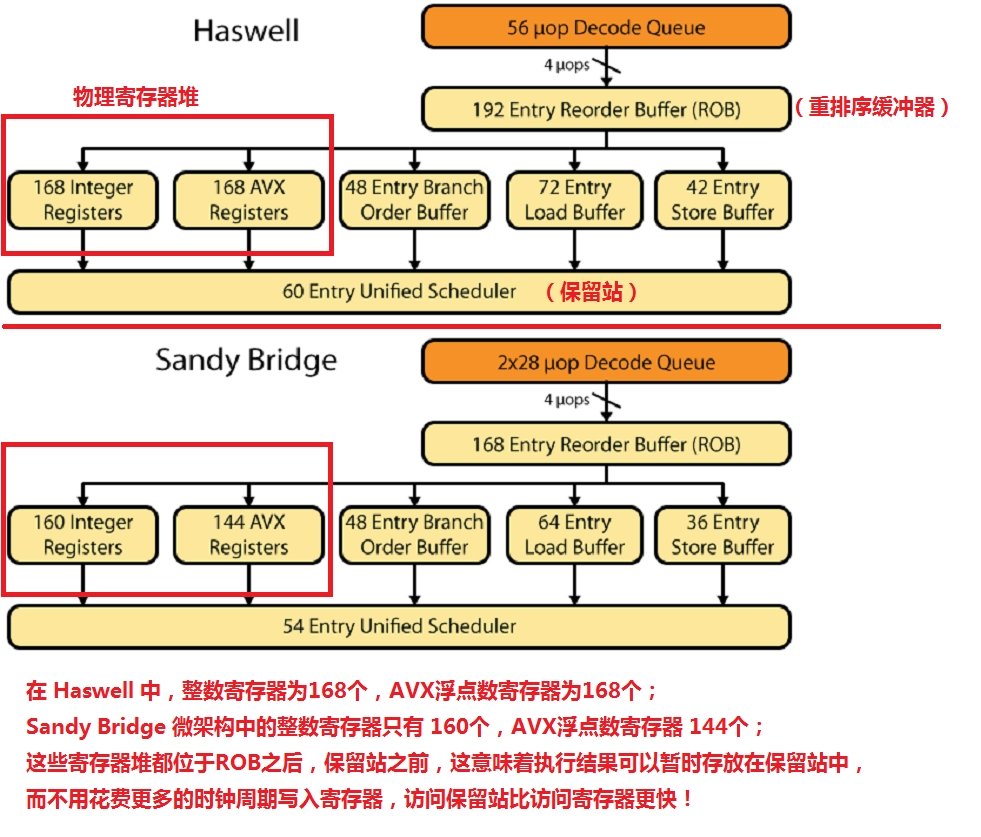

Haswell 微架构中,物理寄存器(程序员不可见)的实际位置如下所示:

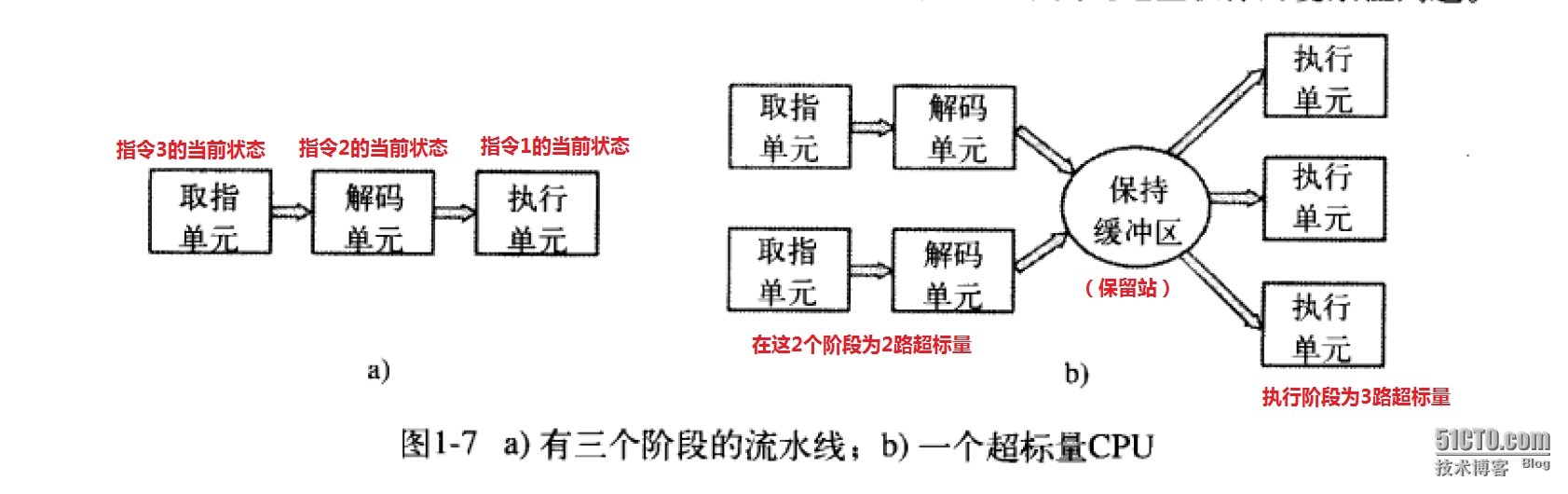

在上面一系列图片中,我们看到了超标量处理器的复杂性:并行的取值,译码,以及执行单元,下面是一个简化后的流水线和超标量示意图: