Nios学习笔记1——流水灯实验

硬件平台:黑金AX301开发板。

操作系统:Win7 64bit。

软件平台:Quartus II 64-Bit Version 12.0 Build 263和Nios II 12.0sp2 Software Build Tools for Eclipse。

参考资料:Nios那些事儿,爱上FPGA开发——特权和你一起学NIOS2

一、硬件开发

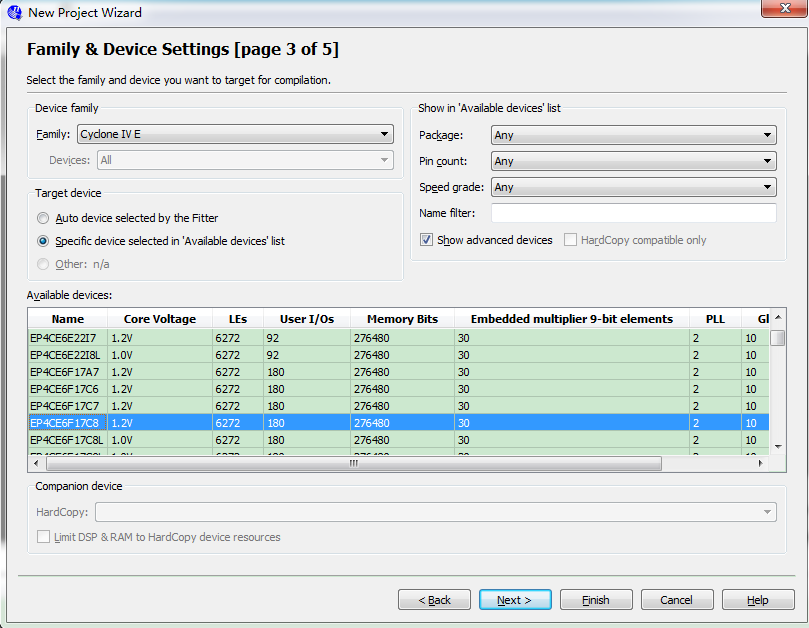

首先打开Quartus,新建一个工程,器件选择EP4CE6F17C8,如下图所示。

接着,进入Qsys 中进行软核的设计。点击 Tools->Qsys,进入Qsys。

File—>Save保存,命名为nioscpu(命名随意)。

返回Qsys主界面后点击"Clock Settings"标签栏修改时钟,双击时钟名clk_0修改为clk,时钟频率由初始的50MHz修改为100MHz,如下图所示:

修改完后回到"System Contents"标签栏。

添加Nios II核

从界面左上角Component Library查找窗口输入nios,如图:

双击Nios II Processor选择Nios II/f,其他保持默认,再点击Caches and Memory Interfaces,将Data cache改为None,如图:

然后点击右下角Finish,Nios II核就加入到Qsys中了。在“Name”列中将nios2_qsys_0改名为mcu(在nios2_qsys_0上右击选择Rename)。

添加SDRAM核

从界面左上角Component Library查找窗口输入sdram找到“SDRAM Controller”后双击。

如下图所示设置,Finish。

将sdram_0改名为sdram,完成后如下图所示:

添加System ID Peripheral核

从界面左上角Component Library查找窗口输入sys找到“System ID Peripheral”后双击。保持默认选项,Finish。将sysid_qsys_0改名为sysid,完成后如下图所示:

添加EPCS

从界面左上角Component Library查找窗口输入epcs找到“EPCS Serial Flash Controller”后双击,默认点击Finish即可。添加完成后改名为epcs。

添加JTAG UART核

从界面左上角Component Library查找窗口输入jtag找到“JTAG UART”后双击。保持默认选项,Finish。将jtag_uart_0改名为jtag,完成后如下图所示:

添加PIO核

从界面左上角Component Library查找窗口输入pio找到“PIO”后双击。在Basic Settings的Width选项中输入4(因为AX301开发板有4个LED),其他保持默认,Finish。将pio_0改名为led,然后点击led的external_connection行中的Export列(列中有灰色的Click to export),命名为led,完成后如下图所示:

连接时钟信号

将所有的clk连接起来,如下图所示:

连接数据和指令端口

规则:存储器一类的IP核需要将其Slave端口同Nios 2的data_master和instruction_master相连,其他非存储器IP核则只需连接到Nios 2的data_maste。连接完成后如下图所示:

时钟、数据和指令端口的连接可以直接在创建IP后进行。

指定Nios 2的复位和异常地址

双击mcu,配置Reset Vector为"epcs.epcs_control_port",Exception Vector为"sdram.s1",Finish,如下图所示:

连接复位信号

点击Qsys主界面菜单中的“System”下的“Create Global Reset Network”,完成后如下图所示:

分配基地址

点击Qsys主界面菜单中的“System”下的“Assign Base Addresses”,完成后如下图所示,可以看到现在有4个Warning,两个是中断没有分配,两个是输出没有引出来,我们先来分配中断号。

分配中断号

在“IRQ”标签栏下点选“Avalon_jtag_slave”和IRQ的连接点就会为“jtag”核添加一个值为0的中断号,如下图所示,同样地,给epcs分配中断1。

设置SDRAM和EPCS输出

如图,在Export标签栏下点选sdram的wire行和epcs的external行,分别重命名为sdram和epcs。

生成Qsys系统

Save,点击“Generation”标签栏中Generate按钮生成Qsys系统。至此Nios 2软核构建完毕。点击“HDL Example”标签栏,在HDL Language选择Veriolg,点击Copy留待后面使用,如下图所示:

最后关闭Qsys。