Cyclone III中LVDS的设计

一,概述

LVDS低压差分信号,最早由美国国家半导体公司

提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。

LVDS的工作原理是其中发送端是一个为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。由于接收端对于直流表现为高阻,电流

通过接收端的100欧姆的匹配电阻产生350mA的电压,同时电流经过差分线的另一条流回发送端。当发送端进行状态变化时它通过改变流经100欧姆电阻的 电流的方向产生有效的'0'和'1'态。

二,硬件设计

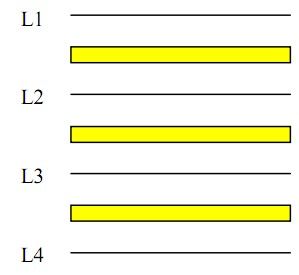

为了达到阻抗控制的要求,PCB的设计采用常见的4层板,基本叠层结构如下图:

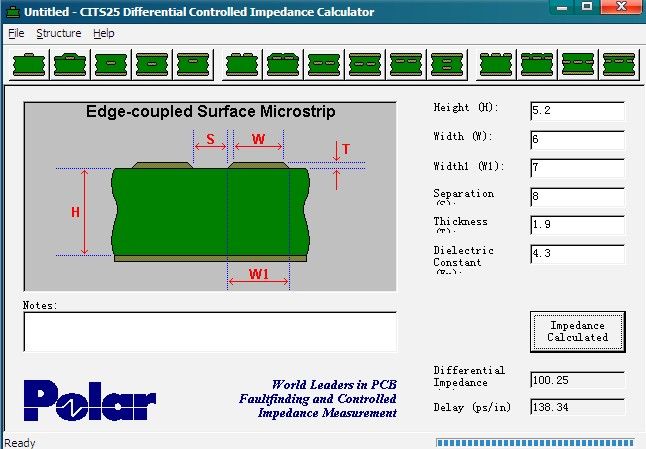

板子的总体厚度约为1.6mm,L1,L4为信号层,L2,L3分别为地线层和电源层,半固化片采用2116,根据CTS的计算,选取差分线线宽6mil,间距8mil,信号层铺铜厚度为0.5OZ(完成后约为高度48um),可以达到差分阻抗约100欧姆。

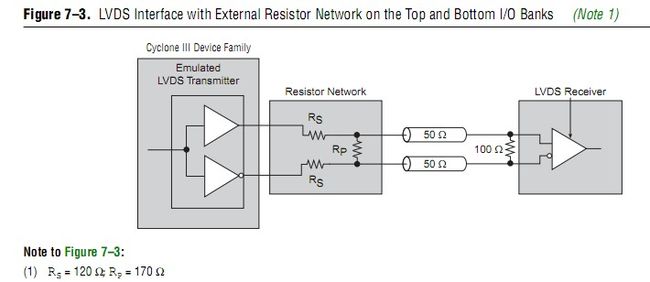

在CIII芯片中,有多组可以输出LVDS信号的IO,但有几点需要注意。在芯片的right bank,left bank上,也就是1,2,5,6 bank,设计了“dedicated output buffer”,这些IO不要添加其他器件既可以输出LVDS信号,也就是说不需要做任何电阻网络匹配的工作了。至于上下两边,3,4,7,8 bank上,没有“dedicated output buffer”,如果要做输出使用,仍然需要配上3个电阻的网络。Altera将这种方式名为“emulated lvds output...”。

需要另外端接电阻的IO,其电阻的选取和链接方式如下:

端接的电阻应该尽量靠近输出的IO口。还有一点需要的注意的是,不管是需要端接电阻还是不需要端接电阻的IO,在作为LVDS输入方式时,都是需要一个100欧姆的电阻的。

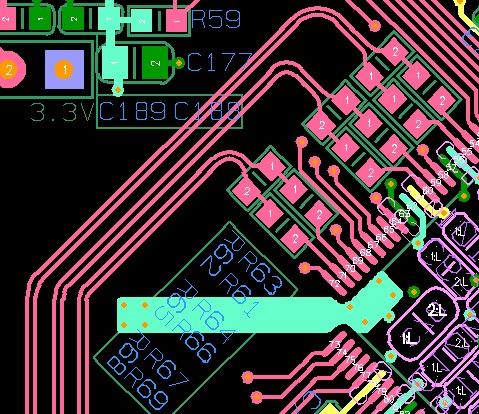

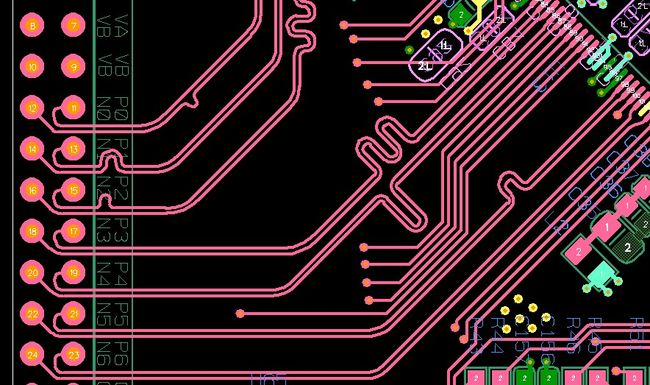

在PCB设计这些LVDS时,要把一组LVDS当做一根线来处理,它们与其他信号线的距离最好能大于20个mil。每一组LVDS内的两根信号线的长度需要做等长处理,同时采用“紧耦合”的走线方式更加有利于信号的的质量。当“紧耦合”和“等长”发生矛盾,两者不可以兼得时,应该优先考虑等长。LVDS走线尽量走直线,需要拐弯的部分,拐弯走成“圆弧”状,下面就是部分LVDS走线的截图:

三,软件设计

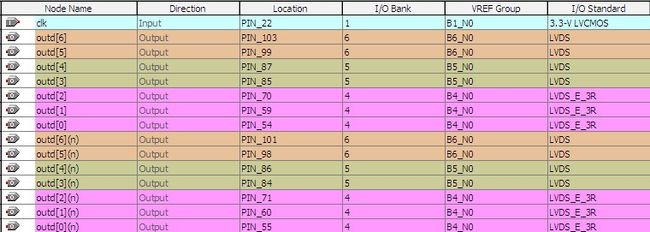

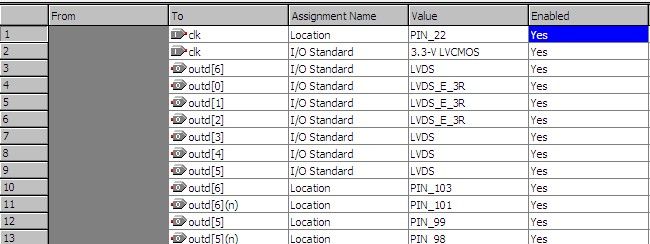

在Quartus中做信号分配时,需要注意,每一组LVDS其实就是一个信号,在Verilog中你就把它们当做一个信号处理,比如信号名称是outd[6]。。比如现需要配置一对LVDS,你想把它们分配的PIN101和PIN103,只需要对LVDS中的P信号做信号分配即可, P103在CIII中已经被定义成P了,你要做的就是把outd[6]指定到P103。首先,在IO

standard中指定电平标准为LVDS,再在outd[6]的location中选择P103就可以了,这个时候你会发现outd[6]的N端就会自动地分配了P101。

上面提到在一些IO作为LVDS使用时需要添加3个端接电阻,Altera就把这些信号称为“LVDS_E_3R”,在分配IO时需要注意区分,将LVDS信号分配成LVDS_E_3R或者相反,“适配”的时候都会报错。

分配好了以后,可以在assignment edit中查看每个IO的状态,以确认是否真的完成了LVDS的分配。

如果想测试LVDS的信号,可以在两个IO上接入一个100欧姆的电阻,使用2个探头一起探测LVDS的眼图。

四,其他

设计中还需要注意以下3点:

1, 选作LVDS的Bank的VCCIO的电压是2.5V,在硬件设计时需要注意,如果电压分配不正确,也无法完成LVDS的分配。一旦该Bank的VCCIO电压被设计成2.5V,那么该Bank的其他非LVDS信号(包括配置信号)的高电平也是2.5V了,JTAG和AS的分配、MSEL的配置也需要注意。比如3.3V的VCCIO时候标准AS模式下MSEL[3..0]为0010,而2.5V时则为0011。

2, 当LVDS和普通信号一起作为输出信号时,普通信号的IO至少距离LVDS信号5个PIN。比如P101和P103作为LVDS输出,则P96~P100,P102,P104~P108不可以同时被分配成普通输出信号,但可以被配置成LVDS输出信号。这些在硬件设计之初也需要有考虑。

3, LVDS非常讲究阻抗的匹配,LVDS的信号应该尽量少打过孔,在跨板传输时需要选择合适的接插件和信号线,如果接插件或者信号选择不正确,会大大影响传输的速率

本帖转载至:http://group.ednchina.com/GROUP_MES_14274_47_49771.HTM