[D-X] 限位数对称制2整数 浮点数乘(除)法器

EDA:quartus II 13. 1

平台:CycloneV:5CSEMA5F31C6

阅读“《自己设计制作CPU与单片机》---- 姜咏江”

粗略过渡到门级的一片笔记:[D-VII] (数)晶体管2逻辑门2寄存器s。个人笔记中的文字表达极差。读书后为整数乘除法的出现编、斗。此次所斗整数乘除法器笔记的保存地址:to_mdivider。32位限位浮点数乘法器笔记保存地址:to_fmulidivider32。

乘法和除法可以转换成(移位和)加减法,如2*3可以拆分为3+ 3(写在程序中的乘除法算式由如像编译器的软件转换)。只要有移位寄存器、加减法器以及诸如编译器的软件就可以完成乘除法。根据乘除法的过程,也可以斗出乘除法器来。

2015.06.24

1 乘法器

乘法计算的过程如下(负数的乘法多一个负号)。

Figure1. 二进制乘法过程

乘法的原理:将乘数的每一位分别与被乘数相乘得到的值作和。乘数b[3..0]的每一位与被乘数a[3..0]相乘,将得到的不同级别的值(b[0] 乘以a[3..0]的值为b[0]* a[3..0],b[1] 乘以a[3..0]的值为2 * (b[1] * a[3..0])……)作和。

1.1 4位无符号乘法器

按照两个4位二进制数乘法过程斗出4位无符号数的乘法器。

- 由位与位相乘的真值表,两位二进制相乘可以用与门来实现

- 1位加法器用[D-VIII]限位数对称制2分段加减法器中的cadder1

4位无符号乘法器电路描述图为to_mdivider工程下的to_umulti4.bdf文件中。

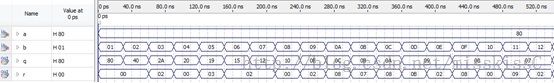

to_umulti4电路仿真图形如下。

Figure2. to_umulti4电路功能仿真

1.2 8位无符号乘法器

按照“4位无符号乘法器”那样最为直观的设计方式可以设计出n位的无符号乘法器。限于电脑屏幕(设计原理图区域的大小),最好能够根据乘法过程斗出“n位乘法器的一个最小单元”,用n个这样的单元的封装就可以组合成n位乘法器。这样,就可以不用原理图的太多区域。

如to_mdivider工程下的to_umulti8r.bdf文件中的电路描述图就是描述的8位乘法器的一个单元(乘法阵列行电路)。(根据乘法过程,to_umulti8r将来自前几次的和ls[7..0]分为ls[7]和ls[6..0];对应地,作当前和后的输出也要分为s[7..1]和s[0]。两个单元之间,ls[6..0]和上一个单元的s[7..1]相连,ls[7]和上一个单元的c2h相连)。用8个to_umulti8r的封装就可以组合成8位无符号乘法器(见to_umulti8.bdf)。

to_umulti8电路的仿真图如下。

Figure3. to_umulti8电路的功能仿真图

2015.06.25

1.3 8位通用乘法器

通用乘法器描述的是既能做无符号数的乘法运算,也能做有符号数的乘法运算。

限位数对称制理论下判断正负数的方法:最高位(bit[7])为1则为负数;最高位为0则为正数。实现有符号运算的方法:先以有符号数的绝对值做乘法得到乘积,再判断两数符号,同号则乘积为正(为乘积本身),异号则表明乘积为负(取乘积堆成码)。

8位有符号乘法器数据流程及对应的电路功能模块。

Figure 4. 有符号乘法器数据流程与对应的电路功能模块

(1) 乘数正负判断的电路描述图

将乘数的正负判断跟乘法器运算模式的信号放在一起(乘法器只有在有符号模式下才区分乘数的符号)。对乘法器的运算模式信号和乘数最高位列真值表,可得用与运算就可以得到乘数的符号。

Figure5. 通用乘法器做有符号运算时乘数的正负判断

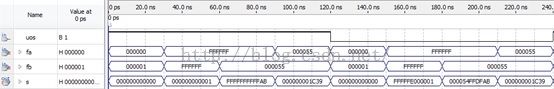

当uos为1时,通用乘法器进入有符号乘法的模式。

(2) 求负数的绝对值的电路描述图

根据限位数对称制(负数由较大的一半正数表示,用较大一半正数表示的负数的绝对值为其(较大一半正数)对称码),因此负数的绝对值由其对称码(取反码加1)来表示。(在二进制中,取反码可由异或门完成。)通过将被加数设置为0,求8位二进制数的对称码可由8个加减法单元(to_counters工程中的cas1.bdf)斗出来。由cas1.bdf封装斗出来的求8位二进制数的绝对值的电路描述图在to_mdivider工程下的to_abv8l.bdf文件中。

当sub = 1时,s[7..0]输出b[7..0]的绝对值。to_abv8l电路的功能仿真图如下。

Figure6. to_abv8电路功能仿真

用限位数对称码相加为2^n(n为二进制位数)特点可判断to_abv8l设计是否正确。对于to_abv8l电路描述图来说,只要sub= 1时,电路就会输出b[7..0]的对称码。而在结合用大一半的数表示负数的理论进行求负数的绝对值时,只会在b[7]= 1时才将sub置为1而求得负数的绝对值。如果将sub信号和b[7]最高位相连,则就直接成了求b[7..0]绝对值得电路(电路描述图保存在to_abv8.bdf中)。

to_abv8电路功能仿真如下图。

Figure7. to_adv8功能仿真

可以看出,正数的绝对值为本身,负数的绝对值为其对称码。

(3) 判断两乘数同号还是异号

由限位数对称制知,二进制数的最高位代表数的正负特点,列a[7]和b[7]的真值表。由根据真值表得出的逻辑表达式知可用一个异或门来判断乘数同异号。

Figure8. 判断乘数同异号电路描述图

sod= 1时,两乘数异号;sod = 0时,两乘数同号。

(4) 两乘数异号时求乘积对称码

得到的乘积是两乘数的绝对值相乘得到的。如果两乘数异号,真正的乘积应该为当前乘积的相反数即负数,根据限位数对称制,应取乘积的对称码(较大一半正数中的某个数)来表示相应的负数。求一个数的对称码可由to_abv8来完成,不过两个8位数相乘得到的是16位,所以需要在to_abv8的基础上得到to_opn16(在to_opn16.bdf中)。其中,to_abv8l由to_abv81.bdf中的电路封装而来,to_abv8h是将to_abv8的电路中的sub和l2c分开,将l2c引脚单独引出来,目的是接受低8位的进位。

to_opn16功能仿真图如下。

Figure9. to_opn16电路功能仿真

由对称码相加的特点可知,在理论上,to_opn16描述的电路达到预定功能。

(5) 组合8位通用乘法器

根据8位有符号乘法器的数据流程和功能模块图已将8位有符号乘法各个模块斗出来了。如果要实现8位通用乘法器to_gen_multi8,可以将这些模块堆在一个原理图中,在进行无符号运算时,乘数直接进入8位乘法器;在进行有符号数的运算时则根据相应条件让数据进入所设计的各个模块中。

Figure10.将组成通用乘法器的模块堆在原理图中

现在开始斗。

当uos= 1时,to_gen_multi8进行有符号乘法,如果a[7..0]或者b[7..0]为负数,那么要通过to_abv8l电路求其绝对值,如果不为负数则直接进入乘法器to_umulti8中。这个过程可以通过ask和bsk来控制三态门的导通与否来实现。

Figure11. 乘数若为负数则取绝对值后再送入乘法器

当uos= 1时,两数的乘积由to_opn16输出,由两乘数是否异号去对称码。

Figure12. 当进行有符号运算时,乘积由to_opn输出

当uos= 0时,两乘数直接进入to_umulti8,并且由to_umulti8直接输出结果

Figure13. uos为0时,参与运算的只有to_umulti8

2015.06.26

2 除法器

以两个4位二进制为对象做除法,观其过程(负数的除法多一个负号)。

Figure15. 二进制除法过程

在被除数前加3个0,其值不变且能够让商也为4位;做第一次除法时,选取被除数的最高4位a[6..4],若a[6..4]大于等于除数b[3..0]则商1,否则商0;然后将a[6..4]减去商与b[3..0]的乘积的差sub[3..0]左移1位加上a[3]作为下一轮乘法的被除数sub[3..0];直到a[0]也参与除法运算,得到最终的商和余数。

1.1 4位无符号除法器

同“4位无符号乘法器”,先根据除法过程斗一个4位除法器出来。

分析。

下一轮的4位被除数由上一轮的4位被除数减去上一轮商与除数的乘积加上被除数下一位得来,所以判断4位被除数是否大于除数可以考虑在减法器的基础上斗。斗出来的器件具有这样的功能:如果4位被除数大于等于4位除数则输出商1,同时用被除数与除数的差作为下一轮被除数的高3位;如果4位被除数小于4位除数则输出商0,同时用被除数的高3位作为下一轮被除数的高3位。被除数最低位参与减法后的差作为余数。

判断4位被除数是否大于除数以得到商。

根据限位数对称制,减法过程可转换为加法完成。a[3..0] – b[3..0]时,如果进位为0则表明a[3..0]小于b[3..0],如果进位为1则表明a[3..0]大于等于b[3..0]。(将a[3..0]和b[3..0]看出5位二进制数的低4位,那么第5位就成了表明数正负的位)。如此可以通过减法器进位来获得商,就可以着手斗减法器了。然后再根据进位来选择差或被除数来作为下一轮被除数的高3位了。

1位减法器。

根据减去一个数等于加上这个数的绝对值的对称码,一个减法单元就是将加法单元中的加数b的取反,当进位为1(取反加1)就完成1位的减法运算。当将n个1位减法器组合到一块时,最低位的进位为1时完成n位减法运算。

1位减法器在工程下的suber1.bdf文件中。其功能仿真图如下。

Figure16. suber1功能仿真图

从1位减法器的功能仿真也可以看出,在做a– b时,若a < b则有c2h为0,否则则为1。

根据进位(商)选择被除数或者差。

当进位为0时选择被除数本身作为下一轮被除数,当进位为1时选择差作为下一轮被除数。具有此功能的单元在gndnd1.bdf文件中。其功能仿真图如下。

Figure17. gndnd1电路功能仿真

4位无符号除法器。

按照4为二进制数除法过程利用gndnd1将4位无符号除法器to_udivider4斗出来。to_udivider4的电路描述图在to_udivider4.bdf文件中。to_udivider4功能仿真图如下。

Figure18. to_udivider4功能仿真

除法器to_udivider4可以接受除数为0的情况,只是给不出正确的结果。

1.2 8位无符号除法器

采用“4位无符号除法器”的方法可以设计出n位除法器,不过设计过程会占用较大的区域,不利于调试。最好也能够设计出n位除法器的一个单元,然后用n个这样的单元就可以组合成n位除法器。

观察“4位无符号除法器”,每一行需要接受上一行的差作为下一轮被除数的高3位,下一轮被除数的最低一位为被除数的后续低位。所以4位除法器的一个单元被除数的输入分为两部分,被除数减去商与除数乘积部分只需输出低3位。其余位照旧。以8位无符号除法器为例,其除法单元被设计在to_udivider8r.bdf文件中。用to_udivider8r的封装按照除法步骤组合成8位无符号除法器to_udivider8(在to_udivider8.bdf中),其功能仿真如下图。

Figure 19. to_udivider8功能仿真图

1.3 8位通用除法器

8位通用除法器描述的是既能够做无符号数除法又能够做有符号数除法。像8位通用除法器那样,将“求绝对值电路”、“除法器”等电路模块放在原理图中斗(斗的方法不变)。商的符号跟乘积的符号的判断方式一样,余数的符号跟被除数一致。8位通用除法器to_gen_divider8的电路描述图在to_gen_divider8.bdf文件中。to_gen_divider8功能仿真图如下。

Figure20. to_gen_divider8功能仿真

2015.06.25

3 小结

在不用某个模式时,此模式对应的模块依然在执行,这可能会比较耗电。可在电路模块不用时将其断开(如三态门)。

[2015.06.26-21:04]

2015.07.12

32位限位浮点数乘法器笔记保存地址:to_fmulidivider32。

4 32位限位浮点数乘除法过程

32位限位浮点数的表示在笔记[D-VIII] 限位数对称制2整数 浮点数加减法器中的“32位浮点数的表示和运算”里。限位浮点数在做乘除法时,涉及到M(尾数)和E(阶码)的操作。M1* 2E1 * M2 * 2E2 = (M1 * M2)*2E1 + E2; M1 * 2E1 / M2 * 2E2= (M1 / M2)* 2E1 - E2。所以,限位浮点数的乘除法对应于尾数的乘除法、阶码的加减法。

5 斗32位浮点数乘除法器

根据乘法器数据流程,尾数乘法需要以下模块。求24位尾数的绝对值电路,24位无符号乘法器,48位求对称码电路。其余模块电路不变。

5.1 32位限位浮点数乘法器

(1) 24位求尾数绝对值电路

用to_abv8l和to_abv8h来构成求24位尾数绝对值的电路fm_abv24,低8位用to_abv8l,高16位用to_abvh。整个电路描述图在fm_abv24.bdf文件中。fm_abv24的功能仿真图如下。

Figure1. to_abv24功能仿真

(2) 24位无符号乘法器

将to_umulti8r扩展成24位乘法阵列行电路fm_umulti24r,此电路描述图在fm_umulti24r文件中。由fm_umulti24r乘法阵列行电路构成的24位无符号乘法器fm_umulti24在fm_umulti24.bdf文件中。fm_umulti24的功能仿真图如下。

Figure2. fm_umulti24功能仿真

(3) 48位求对称码电路

用to_abv8l和to_abv8h组合成求48位限位二进制的对称码。其电路描述图在opn48.bdf中,其低8位由to_abv8l构成,高32位由to_abv8h构成。opn48的功能仿真图如下。

Figure3. opn48功能仿真图

(4) 组合尾数乘法模块

将(1)~ (3)中所斗的模块拖进to_genfm_multi24.bdf中,按照to_gen_multi8整数乘法器那样的斗to_genfm _multi24,使其可以进行有符号的小数乘法用运算。to_genfm _multi24功能仿真图如下。

Figure4. to_genfm _multi24功能仿真

从列举的这几个乘积来看,结果都是正确的。

(5) 加入阶码相加电路

阶码之间的运算可用8位加减法器来完成。将阶码输入作为限位浮点数的高8位,经8位加减法器完成后的运算也作为限位浮点数的高8位输出,这样就完成了32位限位浮点数的乘除法运算。将阶码运算电路scaddsub8(去掉分段功能,将最低位l2c和sub链接在一起)加入to_genfm_multi24.bdf文件中,完成其to_genfm _multi24的功能仿真图如下。

Figure5.to_ genfm _multi24功能仿真

5.2 32位限位浮点数除法器

因为有了斗通用除法器to_gen_divider8的过程后,斗出32位限位浮点数除法器的过程跟斗32位限位乘法器的过程差不多。在学习阶段,我不想再斗32位限位浮点数除法器了。以后要用时再斗。

[2015.07.12-21:35]

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第1张图片](http://img.e-com-net.com/image/info5/90c795d411b84c0695200bb23b1451d5.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第2张图片](http://img.e-com-net.com/image/info5/a2e66062889d43e9ab8bb783034b21f6.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第3张图片](http://img.e-com-net.com/image/info5/01dad3cad7cb461ebbc53d147209669e.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第4张图片](http://img.e-com-net.com/image/info5/560c25750194443e938a4f50575e8edb.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第5张图片](http://img.e-com-net.com/image/info5/66d016e6fb494ccc8ccf38b53d35cb88.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第6张图片](http://img.e-com-net.com/image/info5/1bd50becacf849dc8d02af99fdee97fa.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第7张图片](http://img.e-com-net.com/image/info5/81063724c2d64c3280cb4c0632532332.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第8张图片](http://img.e-com-net.com/image/info5/64547dce94964d89996cbfddeb762bde.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第9张图片](http://img.e-com-net.com/image/info5/07cbb12c987c4cd7ad4ff39ab5df2adf.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第10张图片](http://img.e-com-net.com/image/info5/dbe3406a9eba424abf0d5e1a2cc52127.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第11张图片](http://img.e-com-net.com/image/info5/5b09f01996004f46ba99429d69473fe5.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第12张图片](http://img.e-com-net.com/image/info5/fab167d7f079445785eea204c384eb66.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第13张图片](http://img.e-com-net.com/image/info5/2c202e73780e4afaaf819ab34b0fcef5.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第14张图片](http://img.e-com-net.com/image/info5/5417c69991eb4c198b79b55ed315fea2.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第15张图片](http://img.e-com-net.com/image/info5/b5e5ff769c0844609fe719fc956e5fc2.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第16张图片](http://img.e-com-net.com/image/info5/4386f984cbd747108a2a9b0158591d3e.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第17张图片](http://img.e-com-net.com/image/info5/5f8ac9f877a1475080ac8e79290fe2dd.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第18张图片](http://img.e-com-net.com/image/info5/f31607d52db749bcb04f5c4111abd6f1.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第19张图片](http://img.e-com-net.com/image/info5/621a08cece7242e893f0cc789fbeb964.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第20张图片](http://img.e-com-net.com/image/info5/156316fda579433b9fdb9bbd69ec6257.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第21张图片](http://img.e-com-net.com/image/info5/7f43efb02aaa42fbb0adf1995404c0fb.jpg)

![[D-X] 限位数对称制2整数 浮点数乘(除)法器_第22张图片](http://img.e-com-net.com/image/info5/0b0cf91f1068462baac259de0e9ca8a9.jpg)