- TensorFlow Serving学习笔记3: 组件调用关系

一、整体架构TensorFlowServing采用模块化设计,核心组件包括:Servables:可服务对象(如模型、查找表)Managers:管理Servable生命周期(加载/卸载)Loaders:负责Servable的初始化状态管理Sources:提供新版本Servable的LoaderAspiredVersions:Servable的期望状态集合Core:连接所有组件的核心枢纽APIs:gR

- python教学爬虫入门

早柚不用工作了

python

Python爬虫入门教程:从零基础到抓取数据一、什么是网络爬虫?网络爬虫(WebCrawler),也称为网络蜘蛛(WebSpider),是一种按照一定的规则,自动抓取万维网信息的程序或者脚本。它能够模拟人类在浏览器中的操作,自动访问网页,提取所需的数据,广泛应用于数据采集、搜索引擎优化、市场调研等领域。但在编写爬虫时,务必遵守法律法规和网站的robots.txt协议,避免过度抓取对网站造成负担,同

- Java SPI机制

探索java

#死磕java基础java

引言在现代软件开发中,构建灵活、可扩展的应用程序是开发者的核心目标之一。Java的SPI(ServiceProviderInterface,服务提供者接口)机制为实现这一目标提供了强大的支持。SPI是一种服务发现机制,允许在运行时动态加载服务的实现,从而实现接口与实现的解耦,遵循面向对象设计的开闭原则(对扩展开放,对修改封闭)。通过SPI,框架开发者可以定义标准接口,第三方开发者提供具体实现,而无

- python爬虫框架scrapy学习记录

苏州向日葵

pythonpython爬虫scrapy

一爬虫简介爬虫这种技术听说好多年了,知道它从互联网抓取数据非常厉害,但由于不是专门从事相关工作,了解也就是听听。最近有些空闲,打算实际学习一下,这里做个小小记录。二常用框架介绍通用性框架类型说明scrapy最流行的爬虫框架,功能全面,扩展性强,社区支持完善,适用于中大型爬虫项目pySpider国产爬虫框架,自带web界面,方便监控和管理轻量级框架beautifulSoup+Requests经典的轻

- Jenkins执行svn update报错

在JenkinsPipeline脚本里面,执行sh:svnupdate报错信息:locale:CannotsetLC_CTYPEtodefaultlocale:Nosuchfileordirectorylocale:CannotsetLC_MESSAGEStodefaultlocale:Nosuchfileordirectorylocale:CannotsetLC_ALLtodefaultloca

- 若依vue版前端白名单处理

鱼见千寻

vue.js前端javascript

需求如下:需要直接访问系统某个界面并且不需要登录找到permission.js文件NProgress.configure({showSpinner:false});constwhiteList=['/login','/register'];router.beforeEach((to,from,next)=>{NProgress.start()在这个whiteList添加界面的url就可以直接访问并

- vue项目在IE11上报错SCRIPT1002

背景:vue项目,在谷歌浏览器上展示正常,但是在360安全浏览器上的兼容模式打开,界面空白,浏览器控制台中报错SCRIPT1002:语法错误解决:1先定位报错信息从控制台的报错信息定位过去,会发现是一大串的js(其实也就是模块中有些语法ie不支持),我们需要向上找,找到模块的名字,例如报错的模块名字是sockjs-client2vue.config.js里配置编译代码transpileDepend

- SPI NOR FLASH是什么,与SPI NAND Flash的区别

义嘉泰IC烧录服务

前端javascript网络

SPINORFLASH是什么?SPINORFLASH是一种非易失性存储器,它通过串行接口进行数据传输,具有读写速度快、可靠性高、体积小等优点。它采用类似SRAM的存储方式,每个存储单元存储一位数据(0或1),可以直接寻址,寻址速度非常快。SPINORFLASH支持全双工、单工以及半双工传输方式,被广泛应用于嵌入式系统中,如Bootloader、操作系统内核等程序的存储。由于它的读写速度和寻址方式类

- SpingBoot+LayUI 实现酒店管理系统编写

趣享先生

Java案例分享专栏layui数据库java

✅作者简介:2022年博客新星第八。热爱国学的Java后端开发者,修心和技术同步精进。个人主页:JavaFans的博客个人信条:不迁怒,不贰过。小知识,大智慧。当前专栏:Java案例分享专栏✨特色专栏:国学周更-心性养成之路本文内容:如何入门Python——学习Python的指南针文章目录1、整体分析2、客房模块3、订单模块4、财务模块1、整体分析首先,需要明确酒店管理系统的功能需求,包括但不限于

- 【android bluetooth 协议分析 02】【bluetooth hal 层详解 6】【bt_vendor_opcode_t 介绍】

奔跑吧 android

android15蓝牙协议栈分析androidbthalaosp13hidl_1.0

bt_vendor_opcode_t介绍在AOSP的BluetoothVendor接口中,bt_vendor_opcode_t定义了一组供上层调用的操作指令。这些操作在蓝牙初始化、使用和关闭过程中由协议栈(如Bluedroid)驱动调用,按照一定的顺序执行。这些枚举项代表VendorInterfaceAPI的操作码,协议栈通过调用vendor_call()接口并传入这些opcodes来控制蓝牙芯片

- 【android bluetooth 协议分析 02】【bluetooth hal 层详解 3】【高通蓝牙hal主要流程介绍-上】

奔跑吧 android

android15蓝牙协议栈分析androidbt_hal_1.0qcomqcom_btbluetooth高通蓝牙hal

1.背景本节主要讨论高通蓝牙hal中,的一些流程。看看你是否都清楚如下问题:高通芯片电如何控制?串口是在哪里控制的?固件如何下载?初始化流程是怎么样的?如果你已经对上述讨论的问题,已经很清楚了,那你无需阅读该文章,请自行忽略。当然,也可以给笨叔挑挑错。欢迎评论,一起探讨,毕竟都是笨叔自己的理解,难免有点出入,我也想进步!!!在阅读这篇文章之前,可以先阅读一下两篇文章。【androidbluetoo

- 【数字ic后端】- 物理验证之LVS

LogicYarn

lvs

LVS:layoutversusschematic;版图和电路原理图比对确保所画版图与设计电路完全一致就是LVS工具要做的工作。检查内容:所有信号的电气连接关系是否一致器件类型尺寸是否一致LVS不是一个简中地将版图与电路原理图进行比较的过程,它需要分两步完成:抽取:根据LVS抽取规则,抽取出由版图所确定的网表文件需要注意的是,抽取的网表文件为晶体管级的SPICE网表,而电路为门级网表。因此该门级网

- C# WPF 5种方式实现PDF打印

dotNET跨平台

c#wpfpdf开发语言

在C#WPF中实现PDF打印,可以通过多种方式来完成。以下是五种常见的方法:1.使用Spire.PDFfor.NET这是一个商业库,但提供了强大的PDF处理功能,包括打印。//创建PdfDocument对象并加载PDF文档PdfDocumentpdfDocument=newPdfDocument();pdfDocument.LoadFromFile("path_to_pdf");//设置打印机名称

- Jenkins Pipeline 与 Python 脚本之间使用环境变量通信

要站在顶端

Jenkinsjenkinspythonservlet

JenkinsPipeline与Python脚本之间使用环境变量通信指南✅目标在JenkinsPipeline中设置环境变量在Python脚本中读取这些变量构造可访问的日志链接(artifactURL)用于钉钉/邮件通知中的日志路径拼接一、Jenkinsfile设置环境变量(Windows批处理方式)✅示例:在bat块中设置变量stage('SendNotification'){steps{scr

- 【网络安全】网络协议分析利器:tcpdump 使用指南

学习溢出

Securityweb安全网络协议tcpdump网络安全网络安全

网络协议分析利器:tcpdump使用指南作为网络安全分析师,你将使用网络协议分析工具来协助防御网络入侵。一些网络监控和分析相关的术语:网络协议分析器(也称为抓包器)是用于捕获并分析网络中数据流量的工具。抓包是指捕捉并检查网络中的数据包内容的行为。在本文中,我们将详细介绍命令行下的强大抓包工具:tcpdump。1.什么是tcpdump?tcpdump是一种基于命令行的网络协议分析器。它可以捕获网络流

- **脉冲神经网络:探索发散创新的潜力**一、引言随着人工智能技术的飞速发展,神经网络已成为解决复杂问题的强大工具。其中,脉冲神经网络(Spiking Neural Network,SNN)作为一种模拟

weixin_43880734

人工智能神经网络深度学习python

脉冲神经网络:探索发散创新的潜力一、引言随着人工智能技术的飞速发展,神经网络已成为解决复杂问题的强大工具。其中,脉冲神经网络(SpikingNeuralNetwork,SNN)作为一种模拟生物神经网络的工作机制,因其高效、节能的特性而受到广泛关注。本文将深入探讨脉冲神经网络的基本原理、创新应用以及发展前景。二、脉冲神经网络概述脉冲神经网络是一种模拟生物神经网络中神经元之间通信方式的网络。与传统的人

- Google蜘蛛池详解:提升网站SEO爬行效率的关键策略

蜘蛛池CHUZU

爬虫python

在搜索引擎优化(SEO)领域,Google蜘蛛池(GoogleSpiderPool)是一个核心概念,它直接关系到网站在Google搜索结果中的可见性和排名。本文将从基础原理到实践技巧,系统解析Google蜘蛛池的作用、优化方法及常见误区,帮助开发者高效提升网站爬行效率。一、什么是Google蜘蛛池?Google蜘蛛池指的是Google搜索引擎爬虫(如Googlebot)对网站资源的访问调度机制。简

- SEO蜘蛛池优化:提升网站搜索引擎索引的关键策略

蜘蛛池CHUZU

python

在当今数字化时代,网站如何高效地被搜索引擎索引是SEO(搜索引擎优化)的核心挑战之一。"蜘蛛池"作为一种技术手段,通过管理大量域名或页面来吸引搜索引擎爬虫(spider),从而加速索引过程。本文以"SEO蜘蛛池优化"为副关键词,深入探讨其原理、实现方法及最佳实践,帮助网站管理员提升索引效率,同时规避潜在风险。一、什么是蜘蛛池?蜘蛛池是指一个集中管理多个域名或子域名的系统,专门用于引导搜索引擎爬虫进

- 国产入门级32位单片机PY32F002A

郦777

单片机嵌入式硬件

PY32F002A系列微控制器采用高性能的32位ARM®Cortex®-M0+内核,宽电压工作范围的MCU。嵌入高达20Kbytesflash和3KbytesSRAM存储器,最高工作频率24MHz。包含多种不同封装类型多款产品。芯片集成多路I2C、SPI、USART等通讯外设,1路12bitADC,多个定时器。PY32F002A系列微控制器适用于多种应用场景:例如控制器、手持设备、PC外设、游戏和

- Linux SPI子系统初始化与运行流程详解

进击的程序汪

linux服务器网络

LinuxSPI子系统初始化与运行流程详解以下是LinuxSPI子系统从设备树解析到驱动匹配、数据传输的完整流程,包含详细调用链和树状结构:一、SPI子系统初始化整体流程图[系统启动阶段]└───>[内核初始化]└───start_kernel()└───rest_init()└───kernel_init()└───init_post()└───do_basic_setup()└───drive

- Java:Spi 小实战

weixin_34248118

java数据库

背景Java中区分Api和Spi,通俗的讲:Api和Spi都是相对的概念,他们的差别只在语义上,Api直接被应用开发人员使用,Spi被框架扩张人员使用,详细内容可以看:http://www.cnblogs.com/happyframework/p/3325560.html。Java类库中的实例代码1Class.forName("com.mysql.jdbc.Driver");2Connection

- Java SPI机制使用及实际案例分析

不会先飞的笨鸟

springboot学习javajvm

JavaSPI机制应用场景及案例分析前言一、什么是SPI机制?二、实现方式及使用场景1.接口全限定文件名方式使用场景一:结合场景一分析:2.spring.factories方式使用场景二结合场景二分析:总结前言在之前的JVM分析系列之类加载提到过JavaSPI机制,主要是类加载器反双亲委派的实现(第三方包不在指定jdk路径,一般类加载器无法加载,需要特殊的ContextClassLoader加载以

- VINS_MONO视觉导航算法【三】ROS基础知识介绍

凳子花❀

SLAM立体视觉SLAMVINS_Mono

文章目录其他文章说明ROSlaunch文件基本概念定义用途文件结构根标签常用标签\\\\\\\示例基本示例嵌套示例使用方法启动*.launch文件传递参数总结ROStopicTopic的基本概念Topic的工作原理常用命令示例总结ROS常用命令rosrunroslaunchrosbag主要功能roscorerosnoderostopicrosservicerosparamrqtros::spin(

- 大厂校招:海能达嵌入式面试题及参考答案

大模型大数据攻城狮

牛客网嵌入式面试硬件工程arm开发fpga开发dsp开发驱动开发

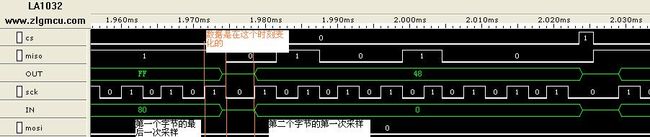

SPI协议的一些基础知识SPI(SerialPeripheralInterface)即串行外设接口,是一种高速的、全双工、同步的通信总线。SPI主要由四根信号线组成:时钟线(SCLK):由主设备产生,用于同步数据传输。时钟的频率决定了数据传输的速度。主设备输出/从设备输入线(MOSI):主设备通过该线向从设备发送数据。主设备输入/从设备输出线(MISO):从设备通过该线向主设备发送数据。片选线(C

- SPI代码详解FPGA-verilog部分(FPGA+STM32)(一)

MinJohnson

STM32FPGA/Verilogstm32fpgaspi

声明:本篇文章面向在已对SPI的四种时序有所了解的人我们采用SPI3模式以及将FPGA作从机,STM32作主机的方式讲解,在STM32控制部分采用的是半双工模式,但其实半双工与全双工区别不大,稍加修改即可本文章属于SPI的升级版,将原本的片选线CS_N再多加一根,变成spi_cs_cmd和spi_cs_data,当spi_cs_cmd拉低的时候表示传送的是命令(命令只由单片机发送),当cs_dat

- Python 爬虫实践-抓取小说

迷路啦

PythonPython爬虫小说

网络爬虫(WebSpider),又被称为网页蜘蛛,是一种按照一定的规则,自动地抓取网站信息的程序或者脚本。爬虫流程:1,先由urllib的request打开Url得到网页html文档2,浏览器打开网页源代码分析元素节点3,通过BeautifulSoup或正则表达式提取想要的数据4,存储数据到本地磁盘或数据库(抓取,分析,存储)下面以爬取笔趣网里面的小说为例:整个逻辑我这里倒着来讲述;下图是一篇小说

- 【android bluetooth 协议分析 14】【HFP详解 1】【案例一: 手机侧显示来电,但车机侧没有显示来电: 讲解AT+CLCC命令】

奔跑吧 android

android15蓝牙协议栈分析androidhfpaghfheadsetclienttelecomaosp13

1.背景今天上报了一例,手机是连接了蓝牙的。但此时来电时,车机侧不显示来电。可以在手机侧看到来电。这里简单分享一下这个问题。借着这个问题,我们讲解一下:SentAT+CLCCRcvd+CLCC:1,1,4,0,0,“173xxxxxxx7”,129,"173xxxxxx7"2.案例分析1.问题情况日志:从btsnoop文件中很清楚的看到我们车机下发了SentAT+CLCC1455852025-06

- NL2SQL实践系列(1):深入解析Prompt工程在text2sql中的应用技巧

汀、人工智能

LLM工业级落地实践promptNL2DSLNL2SQL大模型自然语言处理人工智能Text2SQL

NL2SQL实践系列(1):深入解析Prompt工程在text2sql中的应用技巧NL2SQL基础系列(1):业界顶尖排行榜、权威测评数据集及LLM大模型(SpidervsBIRD)全面对比优劣分析[Text2SQL、Text2DSL]NL2SQL基础系列(2):主流大模型与微调方法精选集,Text2SQL经典算法技术回顾七年发展脉络梳理NL2SQL进阶系列(1):DB-GPT-Hub、SQLco

- 使用requests请求时报错requests.exceptions.SSLError: HTTPSConnectionPool

PGEva

pythonhttp开发语言

这个原因是因为把fiddler开着的,这个时候去请求就会报错,解决方法是降低requests的版本即可。pip3uninstallrequestspip3install"requests==2.20"可以使用piplist查看各个模块的版本,我之前的版本是2.26,降到2.20后就可以了。并且request请求的时候需要加上参数verify=False结果出现警告,UnverifiedHTTPSr

- SqlServer查看锁表与解锁

多加香菜码力全开

SQL专区sqlserver数据库sql

某些情况下,sqlserver的表会被锁住,比如某个会话窗口有数据一直没提交,窗口又没关闭,这时表就会被锁住其他任何连接查询表数据时都不会返回这时需要手工杀掉产生死锁的会话ID,才能恢复正常查看被锁表:selectrequest_session_idspid,OBJECT_NAME(resource_associated_entity_id)tableNamefromsys.dm_tran_loc

- rust的指针作为函数返回值是直接传递,还是先销毁后创建?

wudixiaotie

返回值

这是我自己想到的问题,结果去知呼提问,还没等别人回答, 我自己就想到方法实验了。。

fn main() {

let mut a = 34;

println!("a's addr:{:p}", &a);

let p = &mut a;

println!("p's addr:{:p}", &a

- java编程思想 -- 数据的初始化

百合不是茶

java数据的初始化

1.使用构造器确保数据初始化

/*

*在ReckInitDemo类中创建Reck的对象

*/

public class ReckInitDemo {

public static void main(String[] args) {

//创建Reck对象

new Reck();

}

}

- [航天与宇宙]为什么发射和回收航天器有档期

comsci

地球的大气层中有一个时空屏蔽层,这个层次会不定时的出现,如果该时空屏蔽层出现,那么将导致外层空间进入的任何物体被摧毁,而从地面发射到太空的飞船也将被摧毁...

所以,航天发射和飞船回收都需要等待这个时空屏蔽层消失之后,再进行

&

- linux下批量替换文件内容

商人shang

linux替换

1、网络上现成的资料

格式: sed -i "s/查找字段/替换字段/g" `grep 查找字段 -rl 路径`

linux sed 批量替换多个文件中的字符串

sed -i "s/oldstring/newstring/g" `grep oldstring -rl yourdir`

例如:替换/home下所有文件中的www.admi

- 网页在线天气预报

oloz

天气预报

网页在线调用天气预报

<%@ page language="java" contentType="text/html; charset=utf-8"

pageEncoding="utf-8"%>

<!DOCTYPE html PUBLIC "-//W3C//DTD HTML 4.01 Transit

- SpringMVC和Struts2比较

杨白白

springMVC

1. 入口

spring mvc的入口是servlet,而struts2是filter(这里要指出,filter和servlet是不同的。以前认为filter是servlet的一种特殊),这样就导致了二者的机制不同,这里就牵涉到servlet和filter的区别了。

参见:http://blog.csdn.net/zs15932616453/article/details/8832343

2

- refuse copy, lazy girl!

小桔子

copy

妹妹坐船头啊啊啊啊!都打算一点点琢磨呢。文字编辑也写了基本功能了。。今天查资料,结果查到了人家写得完完整整的。我清楚的认识到:

1.那是我自己觉得写不出的高度

2.如果直接拿来用,很快就能解决问题

3.然后就是抄咩~~

4.肿么可以这样子,都不想写了今儿个,留着作参考吧!拒绝大抄特抄,慢慢一点点写!

- apache与php整合

aichenglong

php apache web

一 apache web服务器

1 apeche web服务器的安装

1)下载Apache web服务器

2)配置域名(如果需要使用要在DNS上注册)

3)测试安装访问http://localhost/验证是否安装成功

2 apache管理

1)service.msc进行图形化管理

2)命令管理,配

- Maven常用内置变量

AILIKES

maven

Built-in properties

${basedir} represents the directory containing pom.xml

${version} equivalent to ${project.version} (deprecated: ${pom.version})

Pom/Project properties

Al

- java的类和对象

百合不是茶

JAVA面向对象 类 对象

java中的类:

java是面向对象的语言,解决问题的核心就是将问题看成是一个类,使用类来解决

java使用 class 类名 来创建类 ,在Java中类名要求和构造方法,Java的文件名是一样的

创建一个A类:

class A{

}

java中的类:将某两个事物有联系的属性包装在一个类中,再通

- JS控制页面输入框为只读

bijian1013

JavaScript

在WEB应用开发当中,增、删除、改、查功能必不可少,为了减少以后维护的工作量,我们一般都只做一份页面,通过传入的参数控制其是新增、修改或者查看。而修改时需将待修改的信息从后台取到并显示出来,实际上就是查看的过程,唯一的区别是修改时,页面上所有的信息能修改,而查看页面上的信息不能修改。因此完全可以将其合并,但通过前端JS将查看页面的所有信息控制为只读,在信息量非常大时,就比较麻烦。

- AngularJS与服务器交互

bijian1013

JavaScriptAngularJS$http

对于AJAX应用(使用XMLHttpRequests)来说,向服务器发起请求的传统方式是:获取一个XMLHttpRequest对象的引用、发起请求、读取响应、检查状态码,最后处理服务端的响应。整个过程示例如下:

var xmlhttp = new XMLHttpRequest();

xmlhttp.onreadystatechange

- [Maven学习笔记八]Maven常用插件应用

bit1129

maven

常用插件及其用法位于:http://maven.apache.org/plugins/

1. Jetty server plugin

2. Dependency copy plugin

3. Surefire Test plugin

4. Uber jar plugin

1. Jetty Pl

- 【Hive六】Hive用户自定义函数(UDF)

bit1129

自定义函数

1. 什么是Hive UDF

Hive是基于Hadoop中的MapReduce,提供HQL查询的数据仓库。Hive是一个很开放的系统,很多内容都支持用户定制,包括:

文件格式:Text File,Sequence File

内存中的数据格式: Java Integer/String, Hadoop IntWritable/Text

用户提供的 map/reduce 脚本:不管什么

- 杀掉nginx进程后丢失nginx.pid,如何重新启动nginx

ronin47

nginx 重启 pid丢失

nginx进程被意外关闭,使用nginx -s reload重启时报如下错误:nginx: [error] open() “/var/run/nginx.pid” failed (2: No such file or directory)这是因为nginx进程被杀死后pid丢失了,下一次再开启nginx -s reload时无法启动解决办法:nginx -s reload 只是用来告诉运行中的ng

- UI设计中我们为什么需要设计动效

brotherlamp

UIui教程ui视频ui资料ui自学

随着国际大品牌苹果和谷歌的引领,最近越来越多的国内公司开始关注动效设计了,越来越多的团队已经意识到动效在产品用户体验中的重要性了,更多的UI设计师们也开始投身动效设计领域。

但是说到底,我们到底为什么需要动效设计?或者说我们到底需要什么样的动效?做动效设计也有段时间了,于是尝试用一些案例,从产品本身出发来说说我所思考的动效设计。

一、加强体验舒适度

嗯,就是让用户更加爽更加爽的用你的产品。

- Spring中JdbcDaoSupport的DataSource注入问题

bylijinnan

javaspring

参考以下两篇文章:

http://www.mkyong.com/spring/spring-jdbctemplate-jdbcdaosupport-examples/

http://stackoverflow.com/questions/4762229/spring-ldap-invoking-setter-methods-in-beans-configuration

Sprin

- 数据库连接池的工作原理

chicony

数据库连接池

随着信息技术的高速发展与广泛应用,数据库技术在信息技术领域中的位置越来越重要,尤其是网络应用和电子商务的迅速发展,都需要数据库技术支持动 态Web站点的运行,而传统的开发模式是:首先在主程序(如Servlet、Beans)中建立数据库连接;然后进行SQL操作,对数据库中的对象进行查 询、修改和删除等操作;最后断开数据库连接。使用这种开发模式,对

- java 关键字

CrazyMizzz

java

关键字是事先定义的,有特别意义的标识符,有时又叫保留字。对于保留字,用户只能按照系统规定的方式使用,不能自行定义。

Java中的关键字按功能主要可以分为以下几类:

(1)访问修饰符

public,private,protected

p

- Hive中的排序语法

daizj

排序hiveorder byDISTRIBUTE BYsort by

Hive中的排序语法 2014.06.22 ORDER BY

hive中的ORDER BY语句和关系数据库中的sql语法相似。他会对查询结果做全局排序,这意味着所有的数据会传送到一个Reduce任务上,这样会导致在大数量的情况下,花费大量时间。

与数据库中 ORDER BY 的区别在于在hive.mapred.mode = strict模式下,必须指定 limit 否则执行会报错。

- 单态设计模式

dcj3sjt126com

设计模式

单例模式(Singleton)用于为一个类生成一个唯一的对象。最常用的地方是数据库连接。 使用单例模式生成一个对象后,该对象可以被其它众多对象所使用。

<?phpclass Example{ // 保存类实例在此属性中 private static&

- svn locked

dcj3sjt126com

Lock

post-commit hook failed (exit code 1) with output:

svn: E155004: Working copy 'D:\xx\xxx' locked

svn: E200031: sqlite: attempt to write a readonly database

svn: E200031: sqlite: attempt to write a

- ARM寄存器学习

e200702084

数据结构C++cC#F#

无论是学习哪一种处理器,首先需要明确的就是这种处理器的寄存器以及工作模式。

ARM有37个寄存器,其中31个通用寄存器,6个状态寄存器。

1、不分组寄存器(R0-R7)

不分组也就是说说,在所有的处理器模式下指的都时同一物理寄存器。在异常中断造成处理器模式切换时,由于不同的处理器模式使用一个名字相同的物理寄存器,就是

- 常用编码资料

gengzg

编码

List<UserInfo> list=GetUserS.GetUserList(11);

String json=JSON.toJSONString(list);

HashMap<Object,Object> hs=new HashMap<Object, Object>();

for(int i=0;i<10;i++)

{

- 进程 vs. 线程

hongtoushizi

线程linux进程

我们介绍了多进程和多线程,这是实现多任务最常用的两种方式。现在,我们来讨论一下这两种方式的优缺点。

首先,要实现多任务,通常我们会设计Master-Worker模式,Master负责分配任务,Worker负责执行任务,因此,多任务环境下,通常是一个Master,多个Worker。

如果用多进程实现Master-Worker,主进程就是Master,其他进程就是Worker。

如果用多线程实现

- Linux定时Job:crontab -e 与 /etc/crontab 的区别

Josh_Persistence

linuxcrontab

一、linux中的crotab中的指定的时间只有5个部分:* * * * *

分别表示:分钟,小时,日,月,星期,具体说来:

第一段 代表分钟 0—59

第二段 代表小时 0—23

第三段 代表日期 1—31

第四段 代表月份 1—12

第五段 代表星期几,0代表星期日 0—6

如:

*/1 * * * * 每分钟执行一次。

*

- KMP算法详解

hm4123660

数据结构C++算法字符串KMP

字符串模式匹配我们相信大家都有遇过,然而我们也习惯用简单匹配法(即Brute-Force算法),其基本思路就是一个个逐一对比下去,这也是我们大家熟知的方法,然而这种算法的效率并不高,但利于理解。

假设主串s="ababcabcacbab",模式串为t="

- 枚举类型的单例模式

zhb8015

单例模式

E.编写一个包含单个元素的枚举类型[极推荐]。代码如下:

public enum MaYun {himself; //定义一个枚举的元素,就代表MaYun的一个实例private String anotherField;MaYun() {//MaYun诞生要做的事情//这个方法也可以去掉。将构造时候需要做的事情放在instance赋值的时候:/** himself = MaYun() {*

- Kafka+Storm+HDFS

ssydxa219

storm

cd /myhome/usr/stormbin/storm nimbus &bin/storm supervisor &bin/storm ui &Kafka+Storm+HDFS整合实践kafka_2.9.2-0.8.1.1.tgzapache-storm-0.9.2-incubating.tar.gzKafka安装配置我们使用3台机器搭建Kafk

- Java获取本地服务器的IP

中华好儿孙

javaWeb获取服务器ip地址

System.out.println("getRequestURL:"+request.getRequestURL());

System.out.println("getLocalAddr:"+request.getLocalAddr());

System.out.println("getLocalPort:&quo