在ISE中使用FFTv5.0 IP核时出现的错误

今天想产生一个16384点的FFT核,使用的是ISE10.1,然而总是出错,错误如下:

Generating IP...

WARNING:sim:216 - The chosen IP does not support a VHDL behavioral model, generating a VHDL structural model instead.WARNING:sim:217 - The chosen IP does not support a Verilog behavioral model, generating a Verilog structural model instead.ERROR:coreutil - Exception caught when running XST synthesis!

ERROR:coreutil - Failure to generate output products

WARNING:coreutil - Default charset GBK not supported, using ISO-8859-1 instea

ERROR:coreutil:424 - An error occurred while running Java. Please examine the console or coregen log file for a specific IP related error.

For more information please search the Xilinx Answers Database for this error: http://www.xilinx.com/supportFinished Generating.

ERROR:sim:57 - Error found during generation

WARNING: the originally identified core 'fft_16384' was not created.

If you changed the name in the customization dialog, you'll need to add that core to your project using Add Source...

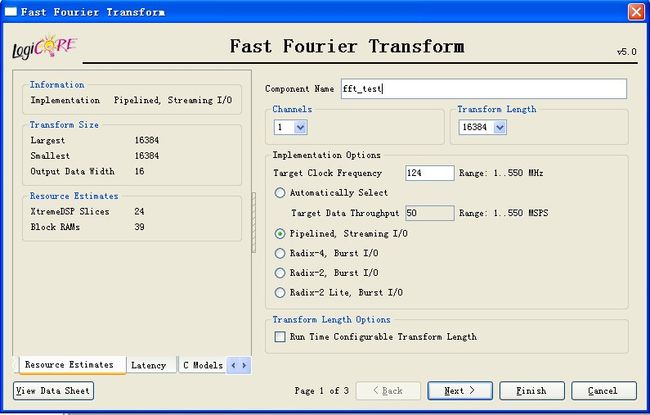

在生成IP核时,具体设置如下:

使用百度和谷歌一顿搜索,也未搜到具体的解决办法,有几个指点方向如下:

(1)CORE Generator - Error messages "Could not reserve enough space for object heap" and "Could not create the Java virtual machine"

链接:http://china.xilinx.com/support/answers/20708.htm

这个帖子主要是说修改一下core generator中file——preferences中的JAVA的参数,这里默认是1024MB,它windows不能高于512MB,但是我修改了,错误依旧……

(2)【FPGA】 Xilinx ISE IP核生成问题

链接:

http://topic.csdn.net/u/20090308/10/8e11c3d3-9348-4a3a-820e-274ba9d9a847.html

这个帖子主要是说JAVA版本低或者是内存小,但我的内存现在使用率很低呀,JAVA版本是什么意思呢?怎么升级呢?

(3)10.1 CORE Generator - White space in project directory causes "ERROR:coreutil - Failure to generate output products"

链接:http://www.xilinx.com/support/answers/30515.htm

这个帖子主要是说存储目录中不能有空格,这个我的目录里也没空格呀,不过这个的确要注意,对于ISE的安装或其它关联的软件来说,安装目录不能有空格的,工程目录也不能有空格,当然更不能有中文路径……

(4)10.1 CORE Generator - "ERROR:coreutil - Failure to generate output products"

链接:http://www.xilinx.com/support/answers/23574.htm

这个帖子的意思是说IP核命名时不能有两个边续的下划线,比如说命名成fft__ifft,这样就不行,好像是说的这个意思吧,但是这个问题在我这里是不存在的呀……

哎,实在是没办法,后来就把IP核生成时的参数改了一下,首先是把一切选用IP核生成的默认参数,呃,最后一切正常……

然后接着改,把Transform Length改成16384,其它参数默认,呃,结果也一切正常……

最后又把其它参数按照自己需要的改,生成一切正常……

但当把Input Data Width和Phase Factor Witdth由16改为自己所需要的20时,错误就出现了……

具体什么原因我也不清楚,是不是占用的资源太多了呢?我也不知道,后来问了一下做过的高人,他指点到这个问题当时他也遇到过,对于FFTv5.0的IP核他也没解决,但是使用V3.2的就没问题了,再说了两个版本的IP核在功能上也没什么区别……

如吧,到此解决办法找到了:使用FFTv3.2的IP核一切就OK啦……

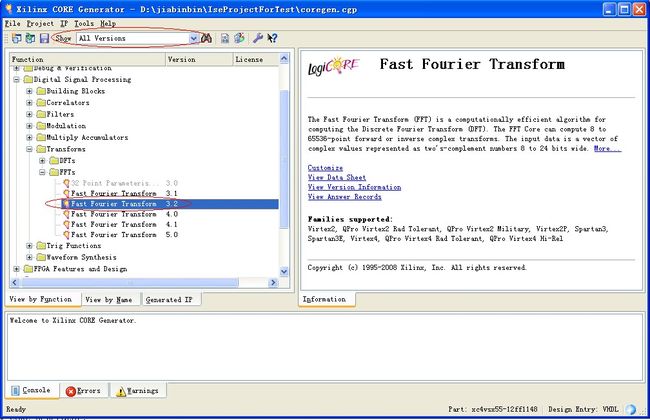

但是对于在ISE10.1环境下怎么使用FFTv3.2的IP核呢?它默认的是v5.0的IP核呀?方法如下:

打开CORE Generator,打开方法如下:

从开始菜单打开“core generator”,具体路径是“开始——所有程序——Xilinx ISE Design Suite 10.1——ISE——Accessories——CORE Generator”,还有一种打开方法是在ISE中,在sources区域任意点击一个已经生成的IP核,然后在Processes区域双击CORE Generator下面的Manage Cores即可……

如上图所示,将工具栏中的show选项选择为All Versions,这里默认为Latest Versions,意为最新版本,我们选择所有版本后即可以找到FFTv3.2的IP核,如上图。双击“Fast Fourier Transform 3.2”即可打开IP核的生成向导,按照自己的意愿修改参数,生成即可。show这里还有一个选项是 All Versions incl. Obsolete, 这个的意思是所有版本并且包含已过时的IP核……

生成结束后关闭CORE Generator即可。这时在工程中可能并不会显示生成的IP核,但其实它已经生成并且添加到了工程中,这时可以关闭工程后重新打开或者是按F5刷新即可显示……

有关FFTv5.0这个错误,只得到了这么一个下策的解决办法,我不知道是不是IP核软件的一个BUG,希望出现牛人来解决吧……