ARM与x86之2--Atom的前生今世

http://blog.sina.com.cn/s/blog_6472c4cc0100kq8b.html

世间本没有PC处理器和嵌入式处理器。这两种处理器在同一天诞生。

1976年5月,Intel开始设计8086处理器。工程师没有想到这颗处理器将给后世带来如此深远的影响。如同许多改变人类命运的产品,设计者最初并没有太大的追求,诸多的不经意与偶然促成了一个伟大的产品[24]。1978年6月8日,Intel正式推出8086处理器[25]。1981年8月12日,基于8088处理器的IBM PC诞生[26]。PC很快席卷了整个世界。

嵌入式处理器这个称呼也随之出现。从广义的角度上讲,所有处理器都是嵌入式处理器,包括用于服务器,PC和嵌入式领域的处理器。PC的日益普及,使得PC处理器从广义的嵌入式领域中脱颖而出,成为单独的一个产业,也就有了PC处理器。

在不久的将来手机也将从广义的嵌入式领域中独立,也会有单独的手机处理器,而不再是嵌入式处理器在手机中的应用。ARM处理器在手机领域的强势地位使得越来越多的人将其贴上了手机处理器的标签。更多的人认为将来的PC是揣在兜里,而不是装在包里。这些猜测触动了Intel这个巨人的心,失去未来的PC是Intel无法承受之重。

巨人的行动并非永远迟缓。2004年,地处Texas州的Intel Austin研发队伍启动了代号为Silverthorne的项目,这个项目所研发的芯片将取代A100和A110这两个低功耗处理器(A100和A110处理器的项目代号为Stealey,基于90nm工艺,是Pentium M的派生芯片[27])。这颗芯片也将是第一颗Atom处理器。Silverthorne项目的启动为两年后Intel毅然抛弃XScale构架埋下了伏笔。拥有顶尖处理器设计能力的Intel绝不允许ARM在旁酣睡。

Austin的研发队伍在项目启动时收到了来自高层的三条指令。Atom处理器必须是一个低功耗芯片,TDP(Thermal Design Power)约为ULV(Ultra Low Volatage) Dothan(即Intel Celeron M ULV)内核的十分之一(Dothan的TDP约为21瓦)。这颗处理器必须有足够的性能可以快速地浏览网页,流畅地运行高端操作系统[34]。这两条指令虽然苛刻,毕竟合理,也是可以通过努力实现的。

Austin的研发人员为此热血沸腾,也许他们将有机会创造一个完全不同的处理器,也许他们将有机会再一次改变这个世界。最容易想到的是使用RISC架构。从Pentium Pro开始,x86处理器使用了RISC流水线,在这条流水线中运行的是μops,并不是程序员使用的CISC指令。在流水线的开始阶段,x86处理器将CISC指令转换为μops,之后进入指令流水线运行。

如果能够将μops作为指令集直接提供给程序员使用,Austin的研发人员可以抛掉所有包袱,创造一颗完全不同的处理器。这个处理器可以自由地使用Intel从Pentium Pro开始的,并经过若干次改进而调优的μops流水线。Intel引以为傲的PCI/PCIe局部总线架构也可抛弃,毕竟PCIe设备的耗电量远大于ARM的AMBA设备。

主推一个新的指令集ISA(Instruction Architecture)是一件异常困难的事情。对于Intel这并非不可实现的。使用μops作为新的ISA,不过是将原先由硬件进行的指令翻译过程(Instruction Transforming)转交给编辑器。基于x86处理器的程序只需要经过重新编译,就可以运行在新的处理器平台上。一旦抛弃了CISC指令集,Austin的工程师可以自由地使用Intel所有的技术积累,更重要的是这颗处理器可以借鉴整个处理器界的成果。在多数情况下,新设计的处理器总比之前的好些。

所有这一切不过是研发人员的一厢情愿。来自高层的指令坚定而且明确,这颗低功耗处理器必须严格实现x86向前兼容。这意味着具有30多年历史的x86指令集,必须要不打一丝折扣地在这颗芯片上实现。向前兼容是Intel巨大的利润来源,也是摆在这个星球上最顶级处理器设计人员面前的一个不可逾越的山峰。在Intel并不长的历史中,违背向前兼容的例子只有以惨败而告终的Itanium。

多少年来,Intel的领袖集团都很偏执,偏执的侧重各有不同。格罗夫偏执着改变,将Intel从一个存储器厂商塑造为处理器厂商,更多的偏执着使用了三十多年的x86指令集。

Intel处理器的开发史是工程师与向前兼容不断斗争的奋斗史。许多年之前,Intel凭借向前兼容这一利器,打败了所有RICS厂商,包括DEC,SUN,Motorola和IBM,一统PC与服务器领域。这并不意味着CISC处理器战胜了RISC处理器,x86处理器已经进化成为RISC处理器,只是依然披着CISC指令的外衣。

对CISC指令的向前兼容需要许多额外的晶体管,更为重要的是Intel从1978年使用至今的CISC指令绝非完美,PowerPC和ARM用区区两三百页就能描述清楚的指令集,x86处理器需要使用1千6百多页。x86处理器的指令不仅冗长,更糟糕的是并不等长。处理这些不等长引发的对界问题是众多IC程序员的技术噩梦。

Itanium处理器决定放弃向前兼容,却成了Intel的一场商业噩梦。Intel至今没有醒来,也不敢在Atom处理器上重新进行尝试。一次错误并不意味着下一次依然错误。也许Atom处理器已经错过了再次改变世界的良机。也许Intel错过了丢弃这个糟糕指令集的机会,失去了这个可能的伟大变革,也可能失去了整个世界。

变革不仅需要勇气,更多的是能力。放弃向前兼容的变革也许会使Intel再次获得历史赋予的机会,也许会毁掉Intel。这样的决定,是勇气,是梦想,是坚贞,是决别。这样的决定,诺伊斯可以做,摩尔可以做,格鲁夫可以做,贝瑞特不敢做,欧德宁不敢想。

Intel这样的大公司,只有创始人才敢做,也有能力做出一些伟大的变革,只有他们才有毁掉这个公司的勇气。领袖有了雄威之气,剩下的人才可能有雄威之气。贝瑞特和欧德宁们恐怕做梦都没有考虑过这些可能毁掉Intel的决定,虽然这个决定也可能是上天赐给Intel的机会。睡梦中的格罗夫也许曾无数次被怒火激醒,“再锋利的剑,到了你们手里只能是一把生锈的钝刀!”。

Intel使用了三十多年的CISC指令又一次被强加在Atom处理器中。失落的设计人员需要再一次为向前兼容付出惨重代价。Intel天才的工程师需要再一次直面这些为处理CISC指令而带来的古怪逻辑。Atom处理器再一次被套上枷锁。Intel再一次丧失了和ARM站在同一起跑线上的机会。

与RISC构架使用的定长指令集不同,Intel的CISC指令的长度从16b到120b不等[35]。变长的指令为指令译码部件带来了额外的负担,而且基于CISC指令的流水线很难进一步提高速度和并发指令条数。从Pentium Pro开始,Intel抛弃了CISC指令流水线,而使用μops流水线,为此在x86处理器中需要使用一个特别的指令译码部件,首先将CISC指令转换为内部指令流水线可以识别的μops[33] [36],然后再送入μops流水线中执行。

x86处理器的绝大多数CISC指令可以方便地翻译成一条或者多条μops指令,也可能是多条CISC指令被优化成为一条μops指令。仍有为数不多的过于复杂的CISC指令需要借助Microcode ROM进行查表译码,x86处理器处理这些指令的效率极低,但是这些指令出现的频率极低,并不会影响指令译码效率[33]。

Silverthorne处理器可以使用两种方法实现严格的向前兼容,或者使用μops流水线,或者使用CISC流水线。使用μops流水线也意味着Atom处理器必须保留将CISC指令转换为μops指令的逻辑,也必须保留在绝大多数时间可以安然入睡的Microcode ROM。对于已经集成了23亿个晶体管的Nehalem EX处理器,增加这些古怪的逻辑并不会极大地增加功耗。对于TDP的设计目标仅有2.1瓦的Atom处理器,这些逻辑是不可能被接受的,因为这些古怪逻辑本身使用的功耗已经超过了一些低端ARM处理器[i]。

来自Austin的设计人员必须另辟蹊径。他们试图在Atom处理器中使用Intel最新的工艺,直接执行复杂的CISC指令,这也重新揭开了上世纪九十年代开始的RISC与CISC构架之争。在那场战争中,Intel打败了所有RISC厂商,这并不意味着CISC处理器战胜了RISC处理器。在PC服务器领域,Intel的x86处理器最终被RISC处理器同化,而在剩余的几乎所有领域中CISC构架被RISC构架屠杀。

面对CISC构架的举步维艰,Pentium Pro做出了折中选择。Atom处理器却要继续扛起CISC的大旗。所有这一切并不是因为CISC构架仍有可能优于RISC构架,而是Austin的工程师面对向前兼容的不得已。

也许使用第一流的工艺可以化腐朽为神奇,也许使用最顶尖的工程师可以将一个O(N2)算法实现得比普通工程师实现O(N×LogN)算法更为快速。也许这些“也许”永远都是“也许”。虽千万难,吾独往矣。帝国启动了赌局。

工程师首先改变的是Power设计理念。多年以来,Intel在PC和服务器上有关Power和Performance性能的设计理念是,处理器提升1%性能,Power可以提高2~3%。在Atom处理器中,这个比例是1比1,处理器每提升1%性能,相应的Power不能提高1%[37]。

Atom处理器抛弃了许多在Core 2和Nehalem处理器使用的高效设计,从零开始。与诸多传说并不一致,Atom不是削减版的Pentium M或者Core 2。Atom处理器是Intel自Pentium处理器以来最为简单的设计,也是一个全新的设计。这个设计使用了Intel最为古老的CISC流水线。

无奈的工程师面对由来已久的向前兼容,剩下的选择除了无奈,还是无奈。没有人愿意直面x86处理器这些乖张,谬妄,怪僻,荒诞的CISC指令,也没有人敢甚至去说说挑战“向前兼容”的不合理。

使用μops流水线无法越过Power的天堑,剩下的只有CISC流水线。无奈的设计人员第一个想到的是1989年发布的486处理器[ii],这颗处理器使用了单发射(single-issue),顺序执行(in-order)的CISC流水线。

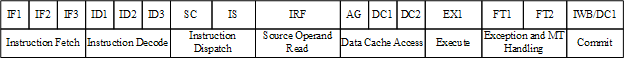

即便在当年486也不是一个顶级处理器,Atom处理器必须对此加以补充。多发射技术仍是必须的,Atom处理器支持双发射。现代高端处理器常用的乱序执行(Out-of-Order Execute)对于追求低功耗的Atom处理器是奢侈的,Austin的设计人员暂时放弃了乱序执行这个已经被广泛验证,可以显著提高流水线执行效率的功能。486处理器使用的5级流水线并不利于处理器主频的提升,Atom处理器将其提高到16级,如图1所示。

图1Atom处理器的流水线[34]

这不是Atom处理器流水线的全部。Atom处理器还含有两级预先译码部件(Predecoder)。传统的x86指令并不等长,而是16b~120b,Predecoder部件的作用是划分指令边界,然后将其导入L1指令Cache。Atom处理器L1指令Cache的大小为36KB,实际可利用大小仅为32KB,剩余的4KB存放SOI(Start of Instruction),EOI(End of Instruction),等信息[34]。

Atom处理器可以直接处理多数CISC指令,但是仍然有一些过于复杂的CISC指令被分解为若干个μops,再进入指令流水线。Atom处理器的流水线并非没有可取之处,这颗处理器可以直接执行ALU/Memory指令。这类指令首先被分解为ALU和Memory两个微操作,然后成对进入流水线。虽然Memory操作仍不能先于ALU操作执行完毕,也明显提高了这类指令的执行效率。

Atom的指令流水线不如RISC架构完美,但这是Intel的工程师在向前兼容的大前提下,为降低功耗而进行的一次大胆尝试。Atom使用按序执行流水线,这也使得HT(Hyper-Threading)技术的引入成为必然。HT技术是Intel对SMT(Simultaneous Multithreading)技术的一种称呼。在现代处理器的设计中,可以使用两种技术在节约整个设计成本的前提下大幅提高并行度,一种是提高ILP(Instruction Level Parallelism),一种是增强TLP(Thread Level Parallelism)[38]。

Superscalar技术是提高ILP最常用的方法,Superscalar技术是指在同一个时钟周期CPU可以发射多条指令。这一技术最早出现在1964年,Seymour Cray的CDC6600就使用了这一技术[39]。这一方法在绝大多数高端处理器中得到了广泛的应用。Intel的高端处理器可以并发执行3~4条指令。

TLP技术最常用的实现手段即为SMT。DEC的工程师准备在Alpha21464(EV8[iii])上率先实现SMT技术。而Alpha21464还没有完成最终的Tape-Out,就需要为Itanium让路而被迫取消[40][41]。这是在学术领域无所不能的Alpha处理器的最后绝唱。DEC的这些工程师历经辗转,最终在Pentium IV上实现了HT技术。此后MIPS MT和Power5也支持SMT技术。

HT技术的本质是在同一个CPU中支持多个线程,每一个线程都具有独立的通用寄存器,Local APIC等其他资源,所有线程共享同一条流水线,可以是一个线程的指令处于流水线的译码阶段,而另一条线程的指令处于执行阶段。当某个线程因为需要执行一些耗时较长的指令时,流水线可以切换到另外一个线程继续执行以避免流水线的阻塞[iv]。对于某些需要大量访问共享资源的应用,使用SMT技术不仅不能提高流水线效率,反而会降低。

Intel声称使用了HT技术的Atom处理器,可以提高36~47%的效率[34],也无法回避某些Benchmark的结果,使用HT的结果更加糟糕。有一点可以肯定,不支持乱序执行的Atom处理器如果还不支持HT,其执行效率不值得去评估。

体系结构上的缺陷很难用任何技术去弥补。Intel依然坚持,依然尝试。在Atom处理器的L1 Cache中一个Cell使用了8个晶体管,与使用6个晶体管的设计相比,这种设计显然将占用相对较大的die size,却可以使用更低的工作电压,最终降低功耗[28]。这些优化并不能弥补Atom为支持“向前兼容”而带来的,源自体系结构的先天缺陷。

第一代Atom处理器,Silverthorne和Diamondville早已问世。基于Atom处理器的Asus EeePC和AcerAspire One取得了不俗的战绩。第二代Atom处理器,Pineview也得到了帝国各个成员的拥戴。向前兼容持续着已有的成功。PC领域因此增加了两个新的成员,Netbook和Nettop。这两个新成员被赋予了一个新的名字,上网本。

Asus的第一个上网本EeePC预装着Linux操作系统[31]。起初这个产品并没有被Wintel帝国重视,EeePC的成功却出乎他们的意料之外,在2007年EeePC的销量达到300,000台[32],迅速地向百万台销售目标进军。Microsoft如梦初醒,迅速作出反应,在EeePC上预装WinXP,很快在EeePC上Linux与WinXP的预装比例达到了1:9。这个比例依然没有完全反映Linux在上网本中所占的比例,许多预装着Linux的上网本是销往中国的。随后比WinXP更加秀丽的Win7也出现在上网本中。

Wintel再一次统治了上网本市场,也亲手毁掉了这个市场。最初灵巧便携的EeePC已经成为历史,越来越多的人们看到的是上网本中Atom处理器的低速与Windows的臃肿。上网本的唯一优点只剩下价格。至此上网本成为廉价笔记本的简称。当Apple的Jobs拿出第一个iPad时,属于Wintel的上网本盛宴已经结束。一个新的名词平板电脑(Tablet)被万众瞩目。ARM处理器和Apple却是主角。

Wintel帝国并没有彻底失败。Intel需要的并不是上网本,不需要这样的产品去瓜分Laptop市场。帝国的终极目标依然是可以手持的PC。上网本是技术尚不成熟的临时产品。Intel很清楚的意识到初期的Atom并不能离开Windows,向前兼容依然重要。只是向前兼容这个紧箍咒套上容易脱离难。

Moorestown平台终于浮出水面。这是Intel为手持PC开发的第一款产品,与ARM的单芯片解决方案并不相同。Moorestown平台由两个芯片组成,分别是代号为Lincroft的处理器和代号为Langwell的芯片组。在Lincroft中包含一个Atom处理器、GPU和存储器控制器,用Intel的45nm工艺实现,在Langwell芯片组中包含手持PC中常用的外部设备,如摄像机接口、USB接口、1080p HDMI接口和NAND控制器等[29]。

为了更快的推出Langwell芯片组,Intel并没有使用自己的生产工艺,而是依靠TSMC的65nm工艺。这引发了人们无限的猜想,在诸多半导体厂商中,Intel始终坚持“in-house-design”的思路,一个芯片从设计到生产都在Intel内部完成,而且Intel有太多的工厂可以生产65nm的芯片。Intel究竟需要从TSMC获得什么?

Intel的Roadmap揭示Moorestown平台仅是一个权宜之计,在并不久远的将来,Medfield平台会将Lincroft和Langwell合二为一,这也将是Intel有史以来第一个单芯片处理器[29][30]。这颗芯片依然采用Intel的“in-house-design”的设计理念吗?

这一切并不重要,从体系结构的角度上看,Moorestown和Medfield平台使用的依然是Atom内核,并以某种方式连接手持PC使用的外部设备。从性能/功耗比的角度上,基于ARM AMBA总线的外部设备目前是最优的,胜过追求性能的PCIe设备。

Moorestown和Medfield平台与ARM处理器平台需要一决胜负的依然是处理器内核。与在SPECint_base_rate2006benchmark程序获得117高分的Nehalem处理器(在此之前没有任何一款处理器获得100以上的分数)不同[42],性能并不是Atom处理器的优势。并不出乎体系结构专家的意外,在许多Benchmark程序下,Atom处理器落后于Cortex A9处理器[43],如下表所示。而Atom处理器使用的功耗与ARM处理器目前并没有可比之处。

|

|

CoreMark/MHz |

Dhrystone |

Max MHz |

Estimate CoreMark at MaxMHz |

| Cortex A8 |

2.4 |

2.0 |

1.0GHz (S5PC110) |

2415 |

| Cortex A9 |

2.9 |

2.5 |

1.0GHz (Tegra 2) 2.0GHz |

2881 5762 |

| MIPS 74K |

2.5 |

2.0 |

1.6GHz |

4000 |

| N280 (1 thread) |

1.8 |

2.4 |

1.67GHz(N280) 2.GHz(Z550) |

3060 3673 |

| N280 (2 threads) |

2.8 |

N.A. |

1.67GHz(N280) 2.GHz(Z550) |

4664 5600 |

Youtube上有一个流传已久的视频[44],一个1.6GHz的Atom处理器(很可能是N270)与一个双核500MHz的Cortex A9平台在相同的分辨率,相同的主存储器大小,相同的操作系统环境下,浏览网页的速度几乎不分上下。采用RISC架构的Cortex A9依然有非常大的潜力可以进一步提升性能,而在体系结构上强调向前兼容的Atom处理器早已被捆住手脚。

失去性能优势的ARM处理器,还有功耗。而失去了性能优势的Atom处理器,只剩下向前兼容。越来越多的人们开始发问,在手持式领域,向前兼容是不是如Intel所料那样重要?虽然Intel一再宣称x86处理器拥有最大的软件Ecosystem,又有多少x86兼容的程序可以不加修改地移植到手持式设备中,又有多少硬件IP可以与PCIe总线直接互连?

如果在手持式设备中,“向前兼容”也不再重要,Atom处理器剩下的只有Intel耗费重金打造的芯片生产工艺。多年以来IT技术被归于高科技领域,这并不是指架个微机编写软件。半导体芯片的制作使用了人类有史以来最复杂的工艺。

首先是硅的提炼,硅原料被投入一个巨大的硅熔炉中,然后再植入一个精度极高的硅种,被融化的硅原料将围绕这个硅种生长,最后形成一个纯度至少为99.9999%的单晶硅锭(圆柱体)。这个硅锭的直径一般为8英寸或者12英寸。之后这个硅锭被切割为一个个Wafer(硅晶片),Wafer再被切割为一个个正方形的Die。每一个Atom处理器将使用一个Die。

这些Die将被多次影印(Photolithography),蚀刻(Etching),最后形成一个多层3D结构。至此Foundry完全结束。经过Foundry处理后的Die,将经过封装,测试等流程,最终成为一个个半导体芯片。

所谓纳米工艺是发生在Etching阶段,Etching也是半导体工艺技术的重中之重。经过影印后,硅晶片将被涂上一层光敏抗蚀膜,之后使用极短的紫外线曝光光敏抗蚀膜,并用化学溶剂清除已曝光的光敏抗蚀膜连同其下的一层硅。曝光的硅最后将被原子轰击,以生成N井或者P井,最终实现门级电路。

45nm,32nm技术指MOS晶体管栅极的宽度。这个宽度越低,在相同大小的Die中就可以集成更多的晶体管。贝瑞特时代的Intel抓住了半导体工艺的发展启动机遇,在诸多半导体厂商中脱颖而出。但是这种领先很难持久。半导体成产工艺是材料科学,化学工业,光学技术和精工机械的集大成者,本质上是一门实验科学,需要大量的资金投入。

Intel取得了先机,也在以一隅敌全国。Intel率先在Westmere处理器上实现了32nm工艺,22nm将在2011年中期实现[45][46]。这种领先是一年,还是两年,并不重要仅是白驹过隙。ARM Cortex A9已经可以使用Global Foundry提供的28nm工艺。当22nm技术来临时,Intel在生产工艺上的领先优势将不复存在。

Intel率先推出45nm时,也是与其他半导体厂商差距最大的时刻,领先其他半导体厂商一代。而技术的革新与进步总是开头最难,中期发展阶段最快,至末期的举步维艰[v]。种种迹象表明硅晶片的制造工艺已日趋极限。

如果Atom处理器连工艺的领先都无法依靠,在技术上[vi]将没有优势可言。也许一个产品成败并不完全取决于技术也许二十年前Intel战胜所有RISC厂商的故事可能再次发生,也许偏执的力量可以战胜顶尖的技术。

只是Intel已无格鲁夫。

[i] x86向前兼容至少需要使用1.65M个晶体管,比ARM7内核本身还复杂。

[ii] 如果程序员基于Atom处理器,进行程序优化,发现gcc编译器使用486的arch速度最快时,不要大惊小怪。

[iii]Alpha系列的处理器内部代号都是EV,EV是Extended VAX的缩写。VAX机曾是一个时代的经典。我书写的第一行程序就用VAX机下的行编译器的LET TEMP = A; LET B = A; LET A = TEMP。

[iv] 对于计算机体系结构较为熟悉的读者,可以将HT技术说得更简单一些,就是分属不同线程的指令之间没有相关性,只要有空余的执行单元,即可通过预约站,进入执行单元。

[v] 感谢“不懂工艺就不要乱说”在弯曲评论上的批评与指正。我本想修改部分内容,反复考虑后仍觉没有太大必要。留在这里也许更好,这能够提醒我,认真做事未必能做好。所知不多时,不该妄下结论。

弯曲评论的连接见http://www.tektalk.org/2010/11/27/atom的前生今世/。这些批评对我很有帮助。在此提醒读者,这部分与工艺相关的内容,尚有较大的争论。

[vi] 我一直在猜测也许Intel的以色列团队正在基于Sandy Bridge处理器做一个真正意义上的低功耗Atom。我所意识到的一切,在Intel一定有人更早的意识到。个人以为目前的Atom内核已经死去,替代品也许仍然叫Atom,但是这并不重要。