ARM寄存器与汇编指令详解

介绍ARM寄存器之前,先来介绍一下ARM处理的模式:

用户模式(User):ARM处理器正常的程序执行状态

快速中断模式(FIQ):用于高速数据传输或通道处理

外部中断模式(IRQ):用于通用的中断处理

管理模式(Svc):操作系统使用的保护模式

数据访问中止模式(Abort):数据或指令预取终止时进入该模式,用于虚拟存储及存储保护

系统模式(System):运行具有特权的操作系统任务

未定义指令中止模式(Undifined):当未定义指令运行时进入该模式,可用于支持硬件协处理器的软件仿真

然后再来介绍下ARM寄存器组

ARM共有37个32bit的寄存器,其中31个为同样寄存器,6个为状态寄存器,这些寄存器不能被同时访问,但是在任何时候,通用寄存器R0-R14,程序计数器PC,一个或者两个状态寄存器是可以访问的

通用寄存器分为3类

1.未分组寄存器R0-R7

在上面所指的运行模式下,未分组寄存器都指向同一个物理寄存器,它们未被系统用作特殊用途,因此在中断或者异常处理进行模式转换时,由于不同的处理模式受用相同的物理寄存器,所以会造成寄存器中数据的破坏

2.分组寄存器R8-R14

对分组寄存器来说,每一次访问的物理寄存器都与当前的运行模式有关,R8-R12每个寄存器对应两种不同的物理寄存器,当使用FIQ(快速中断模式)时,访问寄存器R8_fiq–R12_fiq,当访问除FIQ模式以外的其它模式时,访问R8_usr–R12_usr. R13,R14每个寄存器对应6个不同的物理寄存器,其中一个是用户模式与系统模式共用,另外5个物理寄存器对应其它5中不同的运行模式R13_XXX 与R14_XXX(XXX = usr,fiq,irq,svc,abt,und)

R13在ARM指令集中常用作堆栈指针SP

R14称为链接寄存器(LR),当执行子程序调用BL指令时,R14可以得到R15(程序计数器PC)的备份,在每一种运行模式下,都可用R14保存子程序的返回地址,当用BL或BLX指令调用子程序时,将PC的当前值复制给R14,执行完子程序后,又将R14的值复制给PC,即完成子程序的调用返回

3.程序计数器PC(R15)

ARM状态下bit[1:0]为0,bit[31:2]用于保存PC

Thumb状态下bit[0]为0,bit[31:1]用于保存PC

由于ARM体系结构采用多级流水线技术,对应ARM指令集而言,PC总是指向当前指令的下两条指令的地址,及PC的值为当前指令的地址增加8个字节(两条指令*32bit)

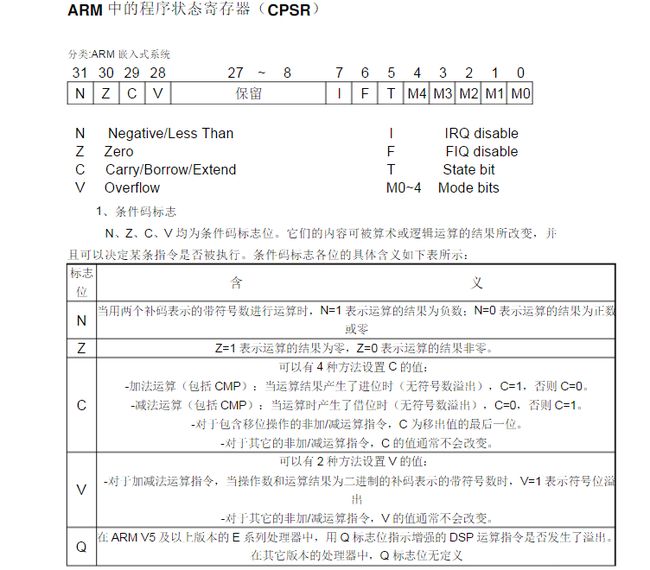

4.R16也称为CPSR(Current Program Status Register当前程序状态寄存器),CPSR可在任何模式下被访问,它包括条件控制位、中断禁止位、当前处理器模式标志位,每一种模式下都有一个专用的物理状态寄存器,称为SPSR(Saved Program Status Register,备份的程序状态寄存器),当异常发生时,SPSR用于保存CPSR的当前值,从异常退出时则可由SPSR恢复CPSR,由于用户模式和系统模式不属于异常模式,它们没有SPSR

ARM指令的寻址方式

1.立即寻址

ADD R0, R0, #0x1 ;R0<-R0+1

ADD R0, R0, #0x3f ;R0<-R0+0x3f

2.寄存器寻址

ADD R0, R1, R2 ;R0<- R1+R2

3.寄存器间接寻址

LDR R0, [R1] ;R0<- [R1]

STR R0, [R1] ; [R1]<- R0

4.多寄存器寻址

LDMIA R0, {R1,R2,R3,R4} ;R1<-[R0] ,R2<-[R0+4] ,R3<-[R0+8], R4<-[R0+12]

最后在来介绍ARM汇编指令

格式:

{} {S} {Rd}, {Rn}, {operand2}

: 指令操作编码,如LDR,STR

{} :指令执行的条件编码,如EQ,NE等

{S} :决定指令的执行是否影响CPRS的值

{Rd} :目标寄存器编码

{Rn} :包括第一个源操作数的寄存器编码

{operand2} 第二个操作数

条件码是在ARM 指令执行之前进行判断的,只有符合条件,ARM指令才能执行

跳转指令

跳转指令用于实现程序流程的跳转,在ARM程序中有两种方法实现程序的流程的跳转

1.使用专门的跳转指令

2.直接向程序计数器PC写入跳转的地址值

ARM汇编中共有四种跳转指令

1.B跳转指令 B指令编码中的跳转地址值是相依当前PC的一个偏移量,经过汇编器计算得到跳转的绝对地址

2.BL 带返回的跳转指令,BL指令在执行完跳转的同时将转移指令的下一条指令的地址复制到当前处理器模式下的链接地址LR中,一般用于子程序的调用和返回

3.BLX带返回和状态切换的跳转指令

4.BX带状态切换的跳转指令

数据处理指令

数据传送指令

MOV 传送 MOV R1, R0 ;R1 = R0

MVN 求反传送 MVN R1, R0 ;R1 = ~R0

CMP 比较 CMP R1, #100 ;R1-100—>CPSR

CMN 负数比较 CMN R1, R0 ;R1+R0—->CPSR

TST 测试 TST R1, #0xffe ;R1&0xffe–>CPSR

TEQ 测试相等 TEQ R1, R0 ;R1^R2—–>CPSR

ADD 相加 ADD R0, R1, R2 ;R0 = R1+R2

ADC 带进位相加 ADC R0, R1, R2 ;R0 = R1+R2+CPSR->C

SUB 相减 SUB R0, R1, R2 ;R0 = R1 - R2

RSB 反向相减 RSB R0, R1, R2 ;R0 = R2 - R1

MUL 乘法 MUL R0,R1, R2 ;R0 = R1 * R2;

AND 与 AND R0, R0, #3 ;R0 = R0 & 3

ORR 或 ORR R0, R0, #3 ;R0 = R0 | 3

BIC 位清除 BIC R0, R0,#0xf0 ;R0 = R0 | 0xf0

LDR 加载 LDR R0, {R1,R2} ;将存储器地址为R1+R2的字数据读入寄存器R0

LDR R0, {R1,R2}! ;将存储器地址为R1+R2的字数据读入寄存器R0并将新地址R1+R2写入R1

STR R0, [R1], #8 ;将R0中的字数据写入R1+8为地址的存储器中

MSR 通用–>CPSR MSR CPSR, R0 ;传输R0的内容到CPSR寄存器

MRS CPSR–>通用 MRS R0, CPSR ;传送CPSR的内容到R0寄存器