28335硬件教程-时钟系统

28335的最大工作频率是250M,其时钟有两种产生途径,第一是直接使用外部时钟(通过XCLKIN接入),第二种方法是在X1和X2引脚外接外部晶振或共振器。系统时钟框图如下:

上述过程产生CLKIN,直接供给CPU,CPU同时向外供给SYSCLKOUT给各个外设。SYSCLKOUT=SYSCLKIN.SYSCLK经过HISPCP LOSPCP的分频后可以送给各个外设,注意,HSPCLK和LSPCLK是独立设定的,也不一定存在。下面是一段初始化程序。

void InitPll(Uint16 val, Uint16 divsel)

{

// Make sure the PLL is not running in limp mode

//若为1,检测时钟错误,未发现时钟

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)

{

// Missing external clock has been detected

// Replace this line with a call to an appropriate

// SystemShutdown(); function.

asm(" ESTOP0");

}

// DIVSEL MUST be 0 before PLLCR can be changed from

// 0x0000. It is set to 0 by an external reset XRSn

// This puts us in 1/4

//将分频设置为4,即CLKIN=1/4OSCCLK

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0) //判断,此位应为0,才能继续设置

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

EDIS;

}

// Change the PLLCR

//结合上述设置 CLKIN=(OSCCLK * 10)/4

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

// Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1; //关闭时钟错误检测

SysCtrlRegs.PLLCR.bit.DIV = val; //设置PLL的乘因子

EDIS;

// Optional: Wait for PLL to lock.

// During this time the CPU will switch to OSCCLK/2 until

// the PLL is stable. Once the PLL is stable the CPU will

// switch to the new PLL value.

//

// This time-to-lock is monitored by a PLL lock counter.

//

// Code is not required to sit and wait for the PLL to lock.

// However, if the code does anything that is timing critical,

// and requires the correct clock be locked, then it is best to

// wait until this switching has completed.

// Wait for the PLL lock bit to be set.

// The watchdog should be disabled before this loop, or fed within

// the loop via ServiceDog().

// Uncomment to disable the watchdog

DisableDog();

//等待PLL稳定

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)

{

// Uncomment to service the watchdog

// ServiceDog();

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0; //使能时钟错误检测

EDIS;

}

// If switching to 1/2

//传入参数为2,结合上述设置 CLKIN=(OSCCLK * 10)/2

if((divsel == 1)||(divsel == 2)) //1为/4,2为/2

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

EDIS;

}

// If switching to 1/1

// * First go to 1/2 and let the power settle

// The time required will depend on the system, this is only an example

// * Then switch to 1/1

if(divsel == 3) //只有直通方式或外部晶振方式才可设置此参数3

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

DSP28x_usDelay(1500);

SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

EDIS;

}

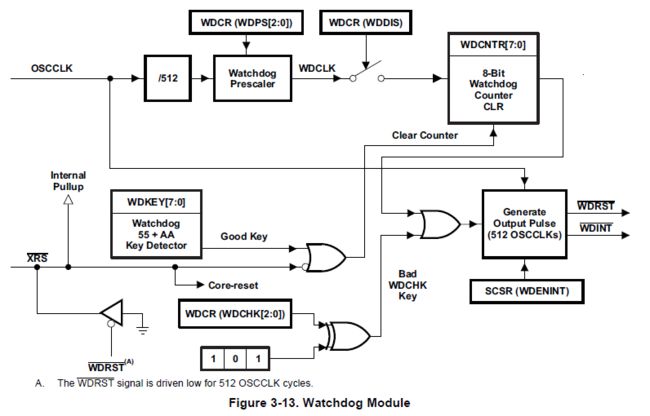

}看门狗电路模块如下

关门狗电路设置一般如下:

void DisableDog(void)

{

EALLOW;

SysCtrlRegs.WDCR= 0x0068;

EDIS;

}

下面探讨一下如何配置外围系统的时钟

外设的时钟的总体框架为:

总体配置LOSPSP和HISPSP的代码如下

SysCtrlRegs.HISPCP.all = 0x0000; // High speed clock = SYSCLKOUT/1 SysCtrlRegs.LOSPCP.all = 0x0004; // Low speed clock= SYSCLKOUT/8

对于xintf:

配置代码如下:

XintfRegs.XINTCNF2.bit.XTIMCLK = 0; //XTIMCLK = SYSCLKOUT/1 XintfRegs.XINTCNF2.bit.CLKMODE = 0; //XCLKOUT is equal to XTIMCLK XintfRegs.XINTCNF2.bit.CLKOFF = 0; //XCLKOUT is enabled. (default)

配置ADC的代码如下:

//The ADC module is clocked by the high-speed clock (HSPCLK) SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; // ADC同理,对其他外设时钟的配置如下:

SysCtrlRegs.PCLKCR0.bit.I2CAENCLK = 0; // I2C SysCtrlRegs.PCLKCR0.bit.SCIAENCLK = 1; // SCI-A SysCtrlRegs.PCLKCR0.bit.SCIBENCLK = 0; // SCI-B SysCtrlRegs.PCLKCR0.bit.SCICENCLK = 0; // SCI-C SysCtrlRegs.PCLKCR0.bit.SPIAENCLK = 1; // SPI-A SysCtrlRegs.PCLKCR0.bit.MCBSPAENCLK = 1; // McBSP-A SysCtrlRegs.PCLKCR0.bit.MCBSPBENCLK = 1; // McBSP-B SysCtrlRegs.PCLKCR0.bit.ECANAENCLK = 0; // eCAN-A SysCtrlRegs.PCLKCR0.bit.ECANBENCLK = 0; // eCAN-B SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the ePWM SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; // ePWM1 SysCtrlRegs.PCLKCR1.bit.EPWM2ENCLK = 1; // ePWM2 SysCtrlRegs.PCLKCR1.bit.EPWM3ENCLK = 0; // ePWM3 SysCtrlRegs.PCLKCR1.bit.EPWM4ENCLK = 0; // ePWM4 SysCtrlRegs.PCLKCR1.bit.EPWM5ENCLK = 1; // ePWM5 SysCtrlRegs.PCLKCR1.bit.EPWM6ENCLK = 1; // ePWM6 SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the ePWM SysCtrlRegs.PCLKCR1.bit.ECAP3ENCLK = 0; // eCAP3 SysCtrlRegs.PCLKCR1.bit.ECAP4ENCLK = 0; // eCAP4 SysCtrlRegs.PCLKCR1.bit.ECAP5ENCLK = 0; // eCAP5 SysCtrlRegs.PCLKCR1.bit.ECAP6ENCLK = 0; // eCAP6 SysCtrlRegs.PCLKCR1.bit.ECAP1ENCLK = 0; // eCAP1 SysCtrlRegs.PCLKCR1.bit.ECAP2ENCLK = 0; // eCAP2 SysCtrlRegs.PCLKCR1.bit.EQEP1ENCLK = 0; // eQEP1 SysCtrlRegs.PCLKCR1.bit.EQEP2ENCLK = 0; // eQEP2 SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0 SysCtrlRegs.PCLKCR3.bit.CPUTIMER1ENCLK = 1; // CPU Timer 1 SysCtrlRegs.PCLKCR3.bit.CPUTIMER2ENCLK = 1; // CPU Timer 2 SysCtrlRegs.PCLKCR3.bit.DMAENCLK = 1; // DMA Clock SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; // XTIMCLK SysCtrlRegs.PCLKCR3.bit.GPIOINENCLK = 1; // GPIO input clock完整设置代码如下:

void InitPeripheralClocks(void)

{

EALLOW;

// HISPCP/LOSPCP prescale register settings, normally it will be set to default values ???

SysCtrlRegs.HISPCP.all = 0x0000; //分频值为此值乘2,0为1,分频值为2. ADC 60M, High speed clock = SYSCLKOUT/1

SysCtrlRegs.LOSPCP.all = 0x0004; //分频值为此值乘2,0为1.SCI,SPI,McBsp 15M100 Low speed clock= SYSCLKOUT/8

// XCLKOUT to SYSCLKOUT ratio. By default XCLKOUT = 1/4 SYSCLKOUT

// XTIMCLK = SYSCLKOUT/2

XintfRegs.XINTCNF2.bit.XTIMCLK = 0; //XTIMCLK = SYSCLKOUT/1

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 0; //XCLKOUT is equal to XTIMCLK

// Enable XCLKOUT

XintfRegs.XINTCNF2.bit.CLKOFF = 0; //XCLKOUT is enabled. (default)

// Peripheral clock enables set for the selected peripherals.

// If you are not using a peripheral leave the clock off

// to save on power.

//

// Note: not all peripherals are available on all 2833x derivates.

// Refer to the datasheet for your particular device.

//

// This function is not written to be an example of efficient code.

//The ADC module is clocked by the high-speed clock (HSPCLK)

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; // ADC

// *IMPORTANT*

// The ADC_cal function, which copies the ADC calibration values from TI reserved

// OTP into the ADCREFSEL and ADCOFFTRIM registers, occurs automatically in the

// Boot ROM. If the boot ROM code is bypassed during the debug process, the

// following function MUST be called for the ADC to function according

// to specification. The clocks to the ADC MUST be enabled before calling this

// function.

// See the device data manual and/or the ADC Reference

// Manual for more information.

ADC_cal();

SysCtrlRegs.PCLKCR0.bit.I2CAENCLK = 0; // I2C

SysCtrlRegs.PCLKCR0.bit.SCIAENCLK = 1; // SCI-A

SysCtrlRegs.PCLKCR0.bit.SCIBENCLK = 0; // SCI-B

SysCtrlRegs.PCLKCR0.bit.SCICENCLK = 0; // SCI-C

SysCtrlRegs.PCLKCR0.bit.SPIAENCLK = 1; // SPI-A

SysCtrlRegs.PCLKCR0.bit.MCBSPAENCLK = 1; // McBSP-A

SysCtrlRegs.PCLKCR0.bit.MCBSPBENCLK = 1; // McBSP-B

SysCtrlRegs.PCLKCR0.bit.ECANAENCLK = 0; // eCAN-A

SysCtrlRegs.PCLKCR0.bit.ECANBENCLK = 0; // eCAN-B

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the ePWM

SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; // ePWM1

SysCtrlRegs.PCLKCR1.bit.EPWM2ENCLK = 1; // ePWM2

SysCtrlRegs.PCLKCR1.bit.EPWM3ENCLK = 0; // ePWM3

SysCtrlRegs.PCLKCR1.bit.EPWM4ENCLK = 0; // ePWM4

SysCtrlRegs.PCLKCR1.bit.EPWM5ENCLK = 1; // ePWM5

SysCtrlRegs.PCLKCR1.bit.EPWM6ENCLK = 1; // ePWM6

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the ePWM

SysCtrlRegs.PCLKCR1.bit.ECAP3ENCLK = 0; // eCAP3

SysCtrlRegs.PCLKCR1.bit.ECAP4ENCLK = 0; // eCAP4

SysCtrlRegs.PCLKCR1.bit.ECAP5ENCLK = 0; // eCAP5

SysCtrlRegs.PCLKCR1.bit.ECAP6ENCLK = 0; // eCAP6

SysCtrlRegs.PCLKCR1.bit.ECAP1ENCLK = 0; // eCAP1

SysCtrlRegs.PCLKCR1.bit.ECAP2ENCLK = 0; // eCAP2

SysCtrlRegs.PCLKCR1.bit.EQEP1ENCLK = 0; // eQEP1

SysCtrlRegs.PCLKCR1.bit.EQEP2ENCLK = 0; // eQEP2

SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0

SysCtrlRegs.PCLKCR3.bit.CPUTIMER1ENCLK = 1; // CPU Timer 1

SysCtrlRegs.PCLKCR3.bit.CPUTIMER2ENCLK = 1; // CPU Timer 2

SysCtrlRegs.PCLKCR3.bit.DMAENCLK = 1; // DMA Clock

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; // XTIMCLK

SysCtrlRegs.PCLKCR3.bit.GPIOINENCLK = 1; // GPIO input clock

EDIS;

}