链接地址学习笔记

链接地址

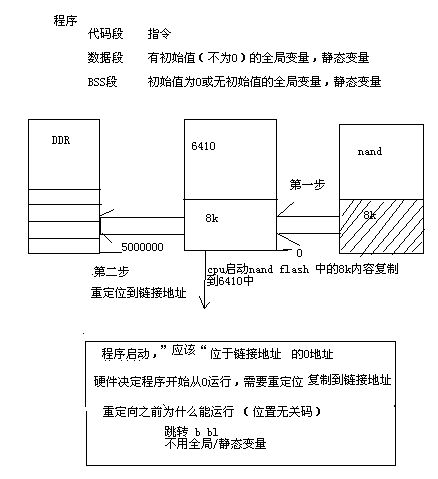

启动过程

示例代码如下:

start.S 文件

.globl _start

_start:

/*硬件相关设置*/

ldr r0,=0x70000000

orr r0,r0,#0x13

mcr p15,0,r0,c15,c2,4

/*关看门狗*/

bl test /*位置无关*/

ldr pc, =test /*位置相关*/

ldr r0,=0x7E00400

mov r1,#0

str r1,[r0]

/*设置栈*/

ldr sp,=8*1024

bl main

halt:

b halt

test:

mov pc,lr

Led.c文件

void delay(){

volatile int i=0x1000;

while (i--);

}

volatile int i=0;

volatile int j=0x12345678;

volatile int k=0;

volatile int g;

int main(){

volatile unsigned long *gpkcon=(volatile unsigned long *)0x7F008800;

volatile unsigned long *gpkdat=(volatile unsigned long *)0x7F008808;

*gpkcon=0x1111;

while(1){

*gpkdat=i;

i++;

if(i==16)

i=0;

delay();

}

return 0;

}

Leds.lds文件

SECTIONS

{

. = 0x50000000;

.text : {

start.o

* (.text)

}

.data : {

* (.data)

}

bss_start = .;

.bss : {

* (.bss)

}

bss_end = .;

}

Makefile 文件

led.bin: start.o led.o

arm-linux-ld -T leds.lds -o led.elf start.o led.o

arm-linux-objcopy -O binary led.elf led.bin

arm-linux-objdump -D led.elf > led.dis

start.o : start.S

arm-linux-gcc -o start.o start.S -c

led.o:led.c

arm-linux-gcc -o led.o led.c -c

clean:

rm *.o led.elf led.bin led.dis

Led.dis文件

led.elf: file format elf32-littlearm

首地址为0x50000000;

Disassembly of section .text:

50000000 <_start>:

50000000: e3a00207 mov r0, #1879048192 ; 0x70000000

50000004: e3800013 orr r0, r0, #19

50000008: ee0f0f92 mcr 15, 0, r0, cr15, cr2, {4}

5000000c: e59f0014 ldr r0, [pc, #20] ; 50000028 <test+0x4>

50000010: e3a01000 mov r1, #0

50000014: e5801000 str r1, [r0]

50000018: e3a0da02 mov sp, #8192 ; 0x2000

5000001c: eb00001e bl 5000009c <main>

50000020 <halt>:

50000020: eafffffe b 50000020 <halt>

50000024 <test>:

50000024: e1a0f00e mov pc, lr

50000028: 07e00400 strbeq r0, [r0, r0, lsl #8]!

5000002c: 00002541 andeq r2, r0, r1, asr #10

50000030: 61656100 cmnvs r5, r0, lsl #2

50000034: 01006962 tsteq r0, r2, ror #18

50000038: 0000001b andeq r0, r0, fp, lsl r0

5000003c: 4d524105 ldfmie f4, [r2, #-20] ; 0xffffffec

50000040: 36373131 undefined instruction 0x36373131

50000044: 2d465a4a vstrcs s11, [r6, #-296] ; 0xfffffed8

50000048: 09060053 stmdbeq r6, {r0, r1, r4, r6}

5000004c: 01090108 tsteq r9, r8, lsl #2

50000050: 0000020a andeq r0, r0, sl, lsl #4

50000054 <delay>:

50000054: e52db004 push {fp} ; (str fp, [sp, #-4]!)

50000058: e28db000 add fp, sp, #0

5000005c: e24dd00c sub sp, sp, #12

50000060: e3a03a01 mov r3, #4096 ; 0x1000

50000064: e50b3008 str r3, [fp, #-8]

50000068: e1a00000 nop ; (mov r0, r0)

5000006c: e51b3008 ldr r3, [fp, #-8]

50000070: e3530000 cmp r3, #0

50000074: 03a02000 moveq r2, #0

50000078: 13a02001 movne r2, #1

5000007c: e6ef2072 uxtb r2, r2

50000080: e2433001 sub r3, r3, #1

50000084: e50b3008 str r3, [fp, #-8]

50000088: e3520000 cmp r2, #0

5000008c: 1afffff6 bne 5000006c <delay+0x18>

50000090: e28bd000 add sp, fp, #0

50000094: e8bd0800 pop {fp}

50000098: e12fff1e bx lr

5000009c <main>:

5000009c: e92d4800 push {fp, lr}

500000a0: e28db004 add fp, sp, #4

500000a4: e24dd008 sub sp, sp, #8

500000a8: e59f3060 ldr r3, [pc, #96] ; 50000110 <main+0x74>

500000ac: e50b3008 str r3, [fp, #-8]

500000b0: e59f305c ldr r3, [pc, #92] ; 50000114 <main+0x78>

500000b4: e50b300c str r3, [fp, #-12]

500000b8: e51b3008 ldr r3, [fp, #-8]

500000bc: e59f2054 ldr r2, [pc, #84] ; 50000118 <main+0x7c>

500000c0: e5832000 str r2, [r3]

500000c4: e59f3050 ldr r3, [pc, #80] ; 5000011c <main+0x80>

500000c8: e5933000 ldr r3, [r3]

500000cc: e1a02003 mov r2, r3

500000d0: e51b300c ldr r3, [fp, #-12]

500000d4: e5832000 str r2, [r3]

500000d8: e59f303c ldr r3, [pc, #60] ; 5000011c <main+0x80>

500000dc: e5933000 ldr r3, [r3]

500000e0: e2832001 add r2, r3, #1

500000e4: e59f3030 ldr r3, [pc, #48] ; 5000011c <main+0x80>

500000e8: e5832000 str r2, [r3]

500000ec: e59f3028 ldr r3, [pc, #40] ; 5000011c <main+0x80>

500000f0: e5933000 ldr r3, [r3]

500000f4: e3530010 cmp r3, #16

500000f8: 1a000002 bne 50000108 <main+0x6c>

500000fc: e59f3018 ldr r3, [pc, #24] ; 5000011c <main+0x80>

50000100: e3a02000 mov r2, #0

50000104: e5832000 str r2, [r3]

50000108: ebffffd1 bl 50000054 <delay>

5000010c: eaffffec b 500000c4 <main+0x28>

50000110: 7f008800 svcvc 0x00008800

50000114: 7f008808 svcvc 0x00008808

50000118: 00001111 andeq r1, r0, r1, lsl r1

5000011c: 50000124 andpl r0, r0, r4, lsr #2

Disassembly of section .data:

50000120 <j>:

50000120: 12345678 eorsne r5, r4, #125829120 ; 0x7800000

Disassembly of section .bss:

50000124 <i>:

50000124: 00000000 andeq r0, r0, r0

50000128 <k>:

50000128: 00000000 andeq r0, r0, r0

5000012c <g>:

5000012c: 00000000 andeq r0, r0, r0

Disassembly of section .comment:

00000000 <.comment>:

0: 3a434347 bcc 10d0d24 <_start-0x4ef2f2dc>

4: 74632820 strbtvc r2, [r3], #-2080 ; 0x820

8: 312d676e teqcc sp, lr, ror #14

c: 312e382e teqcc lr, lr, lsr #16

10: 2941462d stmdbcs r1, {r0, r2, r3, r5, r9, sl, lr}^

14: 352e3420 strcc r3, [lr, #-1056]! ; 0x420

18: Address 0x00000018 is out of bounds.

首地址为0

Disassembly of section .ARM.attributes:

00000000 <.ARM.attributes>:

0: 00003341 andeq r3, r0, r1, asr #6

4: 61656100 cmnvs r5, r0, lsl #2

8: 01006962 tsteq r0, r2, ror #18

c: 00000029 andeq r0, r0, r9, lsr #32

10: 4d524105 ldfmie f4, [r2, #-20] ; 0xffffffec

14: 36373131 undefined instruction 0x36373131

18: 2d465a4a vstrcs s11, [r6, #-296] ; 0xfffffed8

1c: 09060053 stmdbeq r6, {r0, r1, r4, r6}

20: 01090108 tsteq r9, r8, lsl #2

24: 0412020a ldreq r0, [r2], #-522 ; 0x20a

28: 01150114 tsteq r5, r4, lsl r1

2c: 01180317 tsteq r8, r7, lsl r3

30: 031b021a tsteq fp, #-1610612735 ; 0xa0000001

led.elf: file format elf32-littlearm

Disassembly of section .text:

00000000 <_start>:

0: e3a00207 mov r0, #1879048192 ; 0x70000000

4: e3800013 orr r0, r0, #19

8: ee0f0f92 mcr 15, 0, r0, cr15, cr2, {4}

/*

Bl test 的机器码 eb00,0006

1110, 1011,0000 0000 0000 0000 0000 0110

--------------------------------------------------------------

1确定b/bl

剩余为偏移量

Branch instruction contains a signed 2's complement 24 bit offset. This is shifted left two bits, sign extended to 32

bits, and added to the PC.

偏移量offset 6<<2 =6*2*2=24

Pc=pc+24

=(当前指令+8)+24

=(c+8)+24=(12+8)+24=44=0x2c

*/

c: eb000006 Bl test ldr pc, =test

10: e59ff018 ldr pc, [pc, #24] ; 30 <test+0x4>

14: e59f0018 ldr r0, [pc, #24] ; 34 <test+0x8>

18: e3a01000 mov r1, #0

1c: e5801000 str r1, [r0]

20: e3a0da02 mov sp, #8192 ; 0x2000

24: eb00001f bl a8 <main>

00000020 <halt>:

20: eafffffe b 20 <halt>

/*跳转到此位置*/

0000002c <test>:

2c: e1a0f00e mov pc, lr

30: 0000002c andeq r0, r0, ip, lsr #32

34: 07e00400 strbeq r0, [r0, r0, lsl #8]!

38: 00002541 andeq r2, r0, r1, asr #10

3c: 61656100 cmnvs r5, r0, lsl #2

40: 01006962 tsteq r0, r2, ror #18

44: 0000001b andeq r0, r0, fp, lsl r0

48: 4d524105 ldfmie f4, [r2, #-20] ; 0xffffffec

4c: 36373131 undefined instruction 0x36373131

50: 2d465a4a vstrcs s11, [r6, #-296] ; 0xfffffed8

54: 09060053 stmdbeq r6, {r0, r1, r4, r6}

58: 01090108 tsteq r9, r8, lsl #2

5c: 0000020a andeq r0, r0, sl, lsl #4

00000054 <delay>:

54: e52db004 push {fp} ; (str fp, [sp, #-4]!)

58: e28db000 add fp, sp, #0

5c: e24dd00c sub sp, sp, #12

60: e3a03a01 mov r3, #4096 ; 0x1000

64: e50b3008 str r3, [fp, #-8]

68: e1a00000 nop ; (mov r0, r0)

6c: e51b3008 ldr r3, [fp, #-8]

70: e3530000 cmp r3, #0

74: 03a02000 moveq r2, #0

78: 13a02001 movne r2, #1

7c: e6ef2072 uxtb r2, r2

80: e2433001 sub r3, r3, #1

84: e50b3008 str r3, [fp, #-8]

88: e3520000 cmp r2, #0

8c: 1afffff6 bne 6c <delay+0x18>

90: e28bd000 add sp, fp, #0

94: e8bd0800 pop {fp}

98: e12fff1e bx lr

0000009c <main>:

9c: e92d4800 push {fp, lr}

a0: e28db004 add fp, sp, #4

a4: e24dd008 sub sp, sp, #8

a8: e59f3060 ldr r3, [pc, #96] ; 110 <main+0x74>

ac: e50b3008 str r3, [fp, #-8]

b0: e59f305c ldr r3, [pc, #92] ; 114 <main+0x78>

b4: e50b300c str r3, [fp, #-12]

b8: e51b3008 ldr r3, [fp, #-8]

bc: e59f2054 ldr r2, [pc, #84] ; 118 <main+0x7c>

c0: e5832000 str r2, [r3]

c4: e59f3050 ldr r3, [pc, #80] ; 11c <main+0x80>

c8: e5933000 ldr r3, [r3]

cc: e1a02003 mov r2, r3

d0: e51b300c ldr r3, [fp, #-12]

d4: e5832000 str r2, [r3]

d8: e59f303c ldr r3, [pc, #60] ; 11c <main+0x80>

dc: e5933000 ldr r3, [r3]

e0: e2832001 add r2, r3, #1

e4: e59f3030 ldr r3, [pc, #48] ; 11c <main+0x80>

e8: e5832000 str r2, [r3]

ec: e59f3028 ldr r3, [pc, #40] ; 11c <main+0x80>

f0: e5933000 ldr r3, [r3]

f4: e3530010 cmp r3, #16

f8: 1a000002 bne 108 <main+0x6c>

fc: e59f3018 ldr r3, [pc, #24] ; 11c <main+0x80>

100: e3a02000 mov r2, #0

104: e5832000 str r2, [r3]

108: ebffffd1 bl 54 <delay>

10c: eaffffec b c4 <main+0x28>

110: 7f008800 svcvc 0x00008800

114: 7f008808 svcvc 0x00008808

118: 00001111 andeq r1, r0, r1, lsl r1

11c: 00000124 andeq r0, r0, r4, lsr #2

Disassembly of section .data:

00000120 <j>:

120: 12345678 eorsne r5, r4, #125829120 ; 0x7800000

Disassembly of section .bss:

00000124 <i>:

124: 00000000 andeq r0, r0, r0

00000128 <k>:

128: 00000000 andeq r0, r0, r0

0000012c <g>:

12c: 00000000 andeq r0, r0, r0

Disassembly of section .comment:

00000000 <.comment>:

0: 3a434347 bcc 10d0d24 <bss_end+0x10d0bf4>

4: 74632820 strbtvc r2, [r3], #-2080 ; 0x820

8: 312d676e teqcc sp, lr, ror #14

c: 312e382e teqcc lr, lr, lsr #16

10: 2941462d stmdbcs r1, {r0, r2, r3, r5, r9, sl, lr}^

14: 352e3420 strcc r3, [lr, #-1056]! ; 0x420

18: Address 0x00000018 is out of bounds.

Disassembly of section .ARM.attributes:

00000000 <.ARM.attributes>:

0: 00003341 andeq r3, r0, r1, asr #6

4: 61656100 cmnvs r5, r0, lsl #2

8: 01006962 tsteq r0, r2, ror #18

c: 00000029 andeq r0, r0, r9, lsr #32

10: 4d524105 ldfmie f4, [r2, #-20] ; 0xffffffec

14: 36373131 undefined instruction 0x36373131

18: 2d465a4a vstrcs s11, [r6, #-296] ; 0xfffffed8

1c: 09060053 stmdbeq r6, {r0, r1, r4, r6}

20: 01090108 tsteq r9, r8, lsl #2

24: 0412020a ldreq r0, [r2], #-522 ; 0x20a

28: 01150114 tsteq r5, r4, lsl r1

2c: 01180317 tsteq r8, r7, lsl r3

30: 031b021a tsteq fp, #-1610612735 ; 0xa0000001