Verilog基础知识1(FPGA 设计的四种常用思想与技巧之一 -- 乒乓操作)

FPGA 设计的四种常用思想与技巧之一

王诚 Lattice Semiconductor

本文讨论的四种常用 FPGA/CPLD设计思想与技巧: 乒乓操作、 串并转换、 流水线操作、 数据接口同步化, 都是 FPGA/CPLD 逻辑设计的内在规律的体现, 合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。FPGA/CPLD的设计思想与技巧是一个非常大的话题, 由于篇幅所限, 本文仅介绍一些常用的设计思想与技巧, 包括乒乓球操作、 串并转换、 流水线操作和数据接口的同步方法。 希望本文能引起工程师们的注意, 如果能有意识地利用这些原则指导日后的设计工作, 将取得事半功倍的效果!

一、乒乓操作

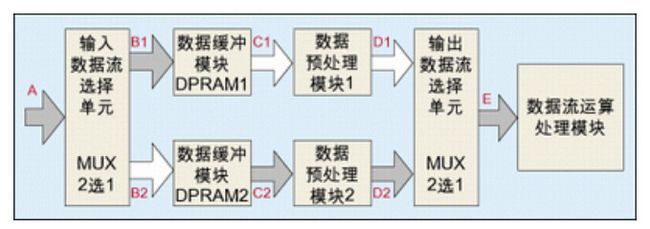

“ 乒乓操作” 是一个常常应用于数据流控制的处理技巧, 典型的乒乓操作方法如图 1 所示。

乒乓操作的处理流程为:输入数据流通过“ 输入数据选择单元” 将数据流等时分配到两个数据缓冲区, 数据缓冲模块可以为任何存储模块, 比较常用的存储单元为双口RAM(DPRAM)、单口RAM(SPRAM)、FIFO等。

在第 1个缓冲周期,将输入的数据流缓存到“ 数据缓冲模块1” ;

在第2 个缓冲周期, 通过“ 输入数据选择单元” 的切换, 将输入的数据流缓存到“ 数据缓冲模块2” , 同时将“ 数据缓冲模块1” 缓存的第1 个周期数据通过“ 输入数据选择单元” 的选择, 送到“ 数据流运算处理模块” 进行运算处理;

在第3 个缓冲周期通过“ 输入数据选择单元” 的再次切换,将输入的数据流缓存到“ 数据缓冲模块1” ,同时将“ 数据缓冲模块2”缓存的第2 个周期的数据通过“ 输入数据选择单元” 切换,送到“ 数据流运算处理模块” 进行运算处理。 如此循环。

乒乓操作的最大特点是通过“ 输入数据选择单元” 和“ 输出数据选择单元” 按节拍、相互配合的切换, 将经过缓冲的数据流没有停顿地送到“ 数据流运算处理模块” 进行运算与处理。

把乒乓操作模块当做一个整体, 站在这个模块的两端看数据, 输入数据流和输出数据流都是连续不断的, 没有任何停顿, 因此非常适合对数据流进行流水线式处理。 所以乒乓操作常常应用于流水线式算法, 完成数据的无缝缓冲与处理。

乒乓操作的第二个优点是可以节约缓冲区空间。 比如在WCDMA 基带应用中,1 个帧是由15个时隙组成的, 有时需要将1 整帧的数据延时一个时隙后处理, 比较直接的办法是将这帧数据缓存起来, 然后延时1 个时隙进行处理。 这时缓冲区的长度是1 整帧数据长, 假设数据速率是3.84Mbps,1 帧长10ms, 则此时需要缓冲区长度是38400 位。

如果采用乒乓操作, 只需定义两个能缓冲1 个时隙数据的 RAM(单口 RAM 即可)。 当向一块RAM 写数据的时候, 从另一块 RAM 读数据, 然后送到处理单元处理, 此时每块 RAM 的容量仅需2560 位即可,2块 RAM 加起来也只有 5120 位的容量。

另外, 巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。 如图2所示, 数据缓冲模块采用了双口 RAM, 并在 DPRAM 后引入了一级数据预处理模块, 这个数据预处理可以根据需要的各种数据运算, 比如在WCDMA 设计中, 对输入数据流的解扩、 解扰、去旋转等。 假设端口 A 的输入数据流的速率为 100Mbps, 乒乓操作的缓冲周期是 10ms。 以下分析各个节点端口的数据速率。

A 端口处输入数据流速率为 100Mbps, 在第1 个缓冲周期10ms 内, 通过“ 输入数据选择单元” , 从B1 到达DPRAM1。B1 的数据速率也是100Mbps,DPRAM1 要在10ms 内写入1Mb 数据。同理, 在第2 个 10ms, 数据流被切换到DPRAM2, 端口 B2 的数据速率也是 100Mbps, DPRAM2在第 2 个 10ms 被写入 1Mb 数据。 在第 3 个 10ms, 数据流又切换到 DPRAM1, DPRAM1 被写入1Mb数据。仔细分析就会发现到第 3 个缓冲周期时,留给 DPRAM1 读取数据并送到“ 数据预处理模块 1”的时间一共是 20ms。 有的工程师困惑于 DPRAM1 的读数时间为什么是 20ms, 这个时间是这样得来的: 首先, 在在第 2 个缓冲周期向DPRAM2 写数据的 10ms 内, DPRAM1 可以进行读操作;

另外, 在第 1 个缓冲周期的第 5ms起(绝对时间为5ms 时刻),DPRAM1 就可以一边向500K 以后的地址写数据, 一边从地址0 读数, 到达10ms 时,DPRAM1 刚好写完了1Mb 数据, 并且读了500K 数据, 这个缓冲时间内DPRAM1 读了5ms; 在第3 个缓冲周期的第5ms 起(绝对时间为35ms 时刻), 同理可以一边向500K 以后的地址写数据一边从地址0 读数, 又读取了5 个ms, 所以截止DPRAM1 第一个周期存入的数据被完全覆盖以前,DPRAM1 最多可以读取20ms时间, 而所需读取的数据为1Mb, 所以端口C1 的数据速率为:1Mb/20ms=50Mbps。 因此, “ 数据预处理模块1” 的最低数据吞吐能力也仅仅要求为50Mbps。 同理, “ 数据预处理模块2”的最低数据吞吐能力也仅仅要求为50Mbps。 换言之, 通过乒乓操作, “ 数据预处理模块”的时序压力减轻了, 所要求的数据处理速率仅仅为输入数据速率的1/2。

通过乒乓操作实现低速模块处理高速数据的实质是:通过DPRAM 这种缓存单元实现了数据流的串并转换, 并行用“ 数据预处理模块1” 和“ 数据预处理模块2” 处理分流的数据, 是面积与速度互换原则的体现!

二、单RAM实现乒乓操作(原创)

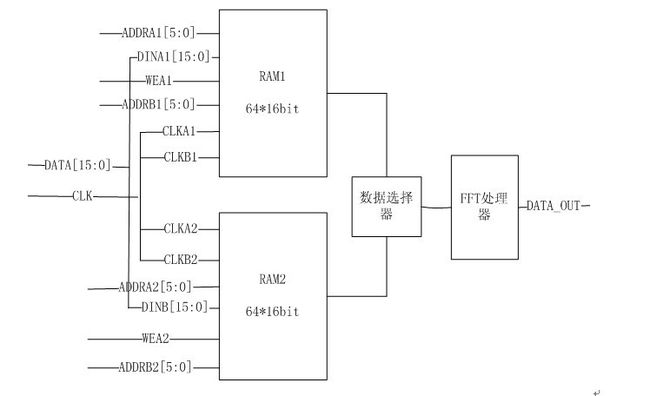

先简单说一下乒乓RAM操作的应用场合,当对数据进行处理时,如果数据来的速率比较快,而处理数据的速率相对较慢,并且在进行数据处理的时候是需要先对进来的数据做一缓冲,等数据量达到一定的程度时再集中对数据进行处理,比如FFT运算就是一个典型的例子。现拿一个64点的FFT运算来举例外说明:假设输入的原始数据的速率是5M,而ADI信号处理器的工作时钟为100M,而每处理一次64点的FFT运算需要30个系统时钟(系统时钟频率是数据速率的20倍),假如现在输入数据数已经达到64个,则信号处理器需要进行FFT运算,当FFT运算结束时,下一个数据有可能已经过了,如果不采取缓存措施,则有可能会导致数据丢失,所以,为了防止上述情况发生,可采用双RAM操作,即:用两块64个存储单元的RAM,当数据来时先对数据进行一下缓存,比如,当前64个数据来时,先把数据缓存在第一块RAM里,当第一块RAM存储满时,这时便以系统时钟速率将第一块RAM的数据给FFT信号处理器,让其完成FFT去处,并将以后的数据缓存到第二块RAM里,由于系统时钟的速率是数据速率的20倍,当第二块RAM里的数据存储满后,FFT处理器有64*20=1280个系统时钟的工作时间,对于处理仅需94(30(FFT运算处理时间)+64(从RAM块里读出64个数据给FFT运算处理器所需的时间))个系统时钟的FFT运算来说已经足够。

图1 传统的双RAM操作框图

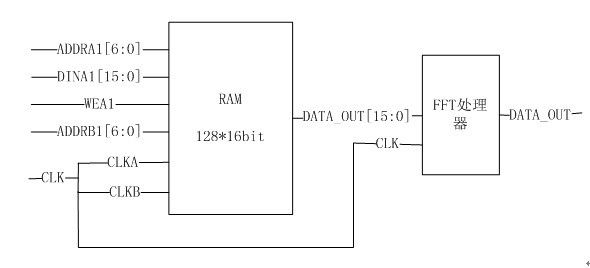

但是,采用传统的双RAM块进行操作时也会存在一定的缺陷,比如,采用两块RAM会占用比较大的面积,这对集成电路的小型化发展带来不利,所以,考虑以上原因,现利用一块RAM完成双RAM乒乓操作的功能。将原来的两个RAM块合成一块,大小变为128*16bit,前64个数据存入地址为0-63的单元里,后64个数据存入64-127的单元中。结构如下图所示。

图2 一片RAM实现双RAM乒乓操作结构图

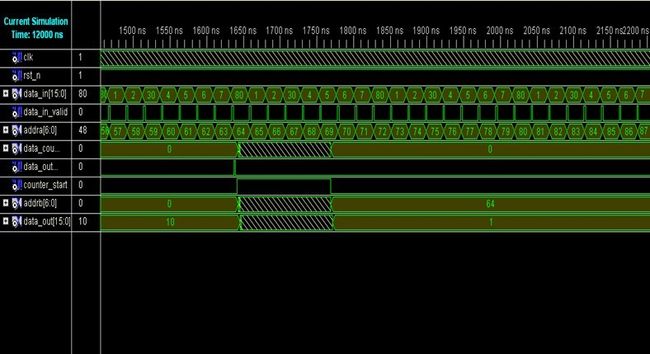

下图是利用ISE软件仿真的逻辑功能图

图3 功能仿真图

如上图所示,写地址线的操作只受输入数据的影响,而读地址线则受输入数据个数的影响,当第64个数据到来时,读地址线便从0变到63,并且将64个数据全部送入FFT处理器时,FFT处理器便在系统时钟下进行工作,当写地址线变到0时,便对64-127单元里的数据进行操作,如此循环,便实现一片RAM的双RAM乒乓操作功能。

我的理解:最近项目用到FIFO对数据的处理,主要是因为输入的数据为慢时钟,数据处理为快时钟,通过检测FIFO内wr_cnt的数值决定是否读取FIFO内部的数据,在此应用中,FIFO就起到了快慢时钟交换数据的接口,当然,这也是RAM和FIFO最多的应用场景,可以用在快慢时钟的差异,也可以用在位宽的差异,起到了缓冲的作用,让处理速度更快的等待数据准备好后再运算,其实想想FPGA的应用无非就是数据处理,所有的控制就是为了让数据更舒服地在正确的时刻达到正确的地方,这个时刻就是时序,这个地方就是HDMI、UART等外部端口。