Verilog 运算符

Verilog 运算

1. Arithmetic Operators(算术运算): + - * / %

Attention: 5%2=1; 5%-2=1; -5%2=-1; -5%-2=-1; (只与前面的数符号有关)

2. Bitwise Operators(位运算符): ~(invert), &(AND), | (OR) , ^ (Exclusive OR),,~^ ^~ (Exclusive NOR)

3. Logical Operators(逻辑运算符):回答应该是(T/F)占1bit

!, &&, ||

For example: !m :Is m false?

m && n :Are both m and n true?

m || n Is either m or n true?

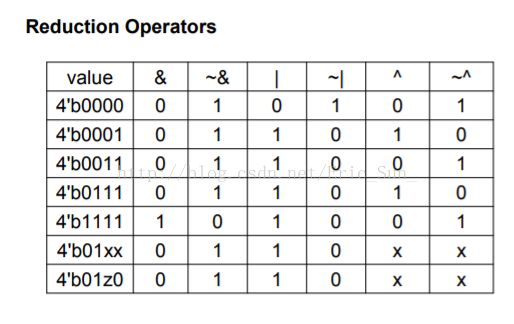

4. Reduction Operators(缩减运算符):回答应该是(T/F)占1bit

&(AND),~&(NAND),|(OR),~|(NOR),^(EOR),~^ 和^~(ENOR)

5. Relational Operators(关系运算符):回答应该是(T/F)占1bit

<,>,<=,>=,==,!=,===,!==

Attention:==,!= 与===,!==

如果里面有x那么== 与!=的结果是unknown

=== 与!==则是相等

For example:

reg [3:0] a, b;

a = 4'b1100; b = 4'b101x;

a == 4'b1z10 // false 0

!= 4'b100x //true 1

b == 4'b101x // unknown x

b != 4'b101x // unknown x

b === 4'b101x // true 1

b !== 4'b101x // false 0

6. Logical ShiftOperators(逻辑位移运算符)

<< :shift m left n-times (将m左移n次),>> :shiftm right n-times(将m 左移n次)

7. ArithmeticShift Operators(算数位移运算符)

<<< :Shift m left n-times, the vacant bits are filled with 0.(将m左移n次,空出来的点补0,>>> :Shift m right n-times, the vacant bits are filled with the leftmostbit(将m 左移n次,空出来的点补这组数中最左边的值)

For example:

对于>> ,<<

// X=4’b1100;

Y = X >> 1; // Y is 4’b0110 Y = X << 2; // Y is 4’b0000

对于>>>,<<<

a = -8; // a = 11…11000 (用32Bit 表示的)

b = a >>> 3; // b = 11…11111 , b = -1 decimal

c = a <<< 2; // b = 11…1100000, b = -32 decimal

8. Conditional Operator (条件运算)

? : sel?m:n If sel is true, select m; else select n

9. Concatenation Operator(串联运算)

{,}

// A= 1’b1, B = 2’b00 , C = 2’b10, D = 3’b110

Y = { B, C}; // Y is 4b’0010

Y = { A, B, C, D}; // Y is 8b’10010110

Y = { B[0], D[2], 2’b11}; // Y is4b’0111

10. Replication Operator(复制操作符)

{{}} {n{m}} Replicate m n-times (复制n次)

A = 1’b1; B = 2’b00; C = 2’b10; D= 3’b110;

Y = { 4{A} }; // Results in Y =4’b1111 Y = { 4{A}, 2{B} }; // Results in Y = 8’b11110000

Y = { 4{A}, 2{B}, C }; // Resultsin Y = 10’b1111000010

input、output、和inout。在verilog中,所有的端口隐含地声明为wire类型,因此如果希望端口具有wire数据类型,将其声明为三种类型之一即可:如果输出类型的端口需要保存数值,则必须将其显式的声明为reg数据类型。 不能将input和inout类型的端口声明为reg数据类型,这是因为reg类型的变量是用于保存数值的,而输入端口只反映与其相连的外部信号的变化,并不能保存这些信号的值。