基于vivado的序列检测实验

目录

目的与要求:

过程及分析(包括电路原理图):

Moore机代码

testbench代码

Mleay机代码

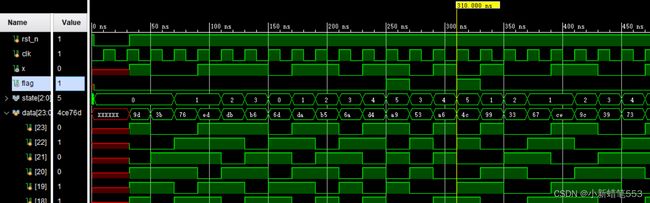

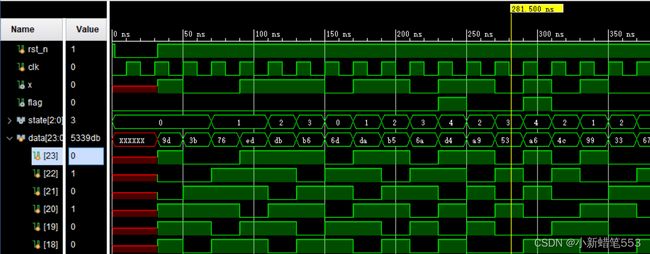

behavioral波形图

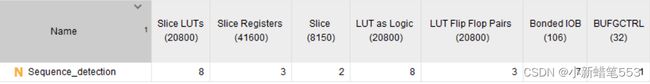

资源利用率:

Moore机和Mealy区别:

目的与要求:

基本要求:

- 利用状态机等知识,设计一个可以识别“01101”的序列检测电路;

- 使用vivado软件中verilog HDL输入方式实现所设计的序列检测器;

- 自行编写测试文件testbench.v 文件进行仿真,验证检测器功能;

高级要求(可选):

用Moore和Mealy机两种状态机实现序列检测,并分析比较其波形、资源利用率、性能的差异。

过程及分析(包括电路原理图):

1、状态机设计思想

状态机的本质是对具有逻辑顺序或时序规律事件的一种描述方法。这个论断的最重要的两个词就是“逻辑顺序”和“时序逻辑”,这两点就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机描述。

2、状态机分类

(1)mealy型和moore型

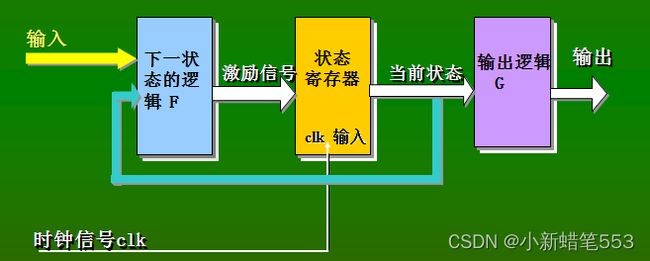

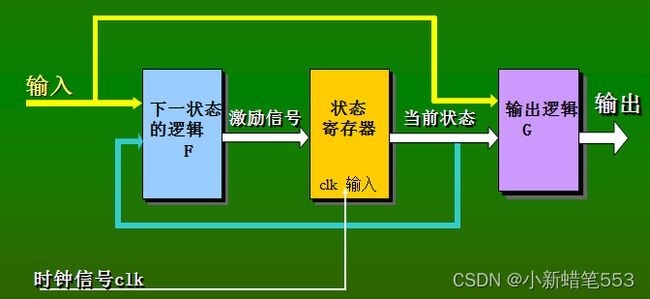

状态机有两大类:Mealy型和Moore型。Moore型状态机的输出只与当前状态有关,而Mealy型状态机的输出不仅取决于当前状态,还受到输入的直接控制,并且可能与状态无关,其状态机结构如下图:

图1 Mealy型状态机结构图

图2 Moore型状态机结构图

(2)按照状态编码来分类

1、Gray(格雷码)码状态机

2、one-hot码(独热码)状态机

3、二进制码状态机

有限状态机编码时常采用的是格雷码和独热码。格雷码,即相邻之间只变1bit,编码密度高。独热码,即任何状态只有1bit为1,其余皆为0,编码密度低。

比如说,表示四个状态,那么状态机寄存器采用格雷码编码只需要2bit,即00(S0),01(S1),11(S2),10(S3),采用独热码则需要4bit:0001(S0), 0010(S1), 0100(S2),1000(S3)。所以很明显采用格雷码可以省2bit寄存器。

(3)在Verilog中描述有限状态机,可以有三种形式,可分为一段式、二段式和三段式。这三种描述主要根据其输入、输出和状态来分类。

一段式状态机:

一段式状态机只选择一个状态标志位,这个状态标志位会在输入的决定下选择跳转到下一个状态还是维持原有状态,在每一个状态下检测状态标志位及输入来决定其状态的跳转及输出。其输出和状态的切换在一个always循环块中执行。

二段式状态机:

二段式状态机将状态分为当前状态和此状态,其系统会自动将次状态更新到当前状态,其输入更新在次状态上,其决定系统的状态切换和输出。其输出和状态的切换在两个个always循环块中执行,第一个always块决定系统状态标志的自动跳转,第二个always块决定系统根据不同状态下的输入进行状态的跳转及输出。

三段式状态机:

三段式状态机将状态分为当前状态和此状态,其系统会自动将次状态更新到当前状态,系统的输入更新在次状态上,其决定系统的状态切换,系统会根据其当前状态决定输出的值。其输出和状态更新和状态切换在三个always块中,第一个always块决定系统状态标志的自动跳转,第二个always块决定系统根据不同状态下的输入进行状态的切换,第三个always块根据系统的当前状态决定输出的值。

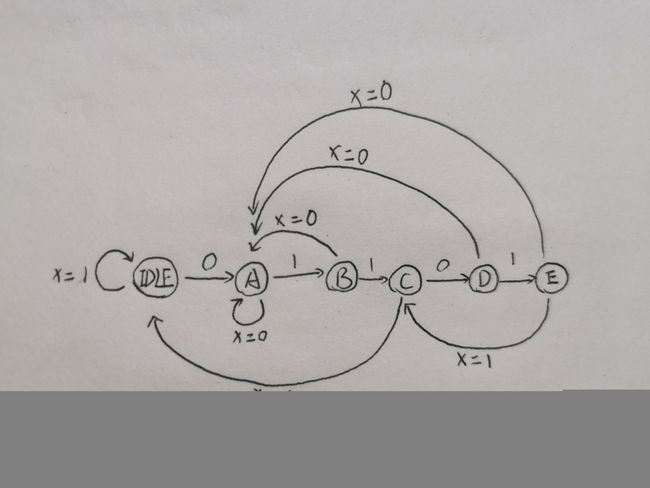

图3 检测序列为01101的状态跳转图(Moore)

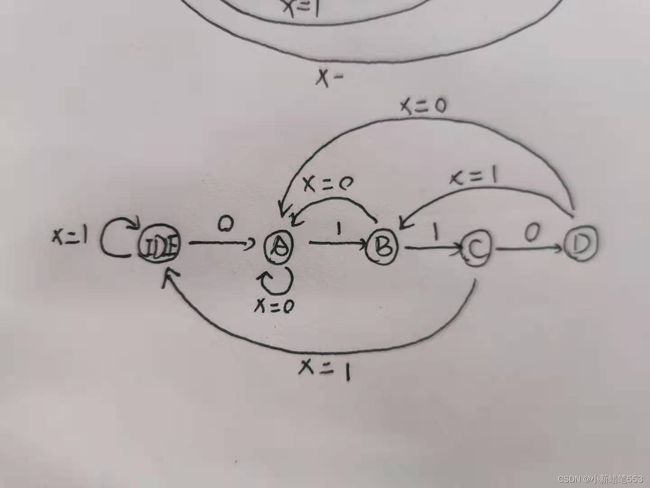

图4 检测序列为01101的状态跳转图(Mealy)

Moore机代码

module Sequence_detection(input x,clk,rst_n,

output flag,

output reg [2:0] state

);

parameter IDLE = 'd0,

A = 'd1, B = 'd2,

C = 'd3, D = 'd4,

E = 'd5;

assign flag =(state==E)?1:0;

always@(negedge rst_n or posedge clk)

begin

if (!rst_n)

begin

state <= IDLE;

end

else

casex(state)

IDLE:if(x==0) //第一个码位对,记状态A

begin

state<=A;

end

else state<=IDLE;

A:if(x==1) //第二个码位对,记状态B

state<=B;

else

state<=A;

B:if(x==1) //第三个码位对,记状态C

state<=C;

else

state<=A;

C:if(x==0) //第四个码位对,记状态D

state<=D;

else

state<=IDLE;

D:if(x==1) //第五个码位对,记状态E

state<=E;

else

state<=A;

E:if(x==1)

state<=C;

else

state<=A;

default:state<=IDLE; //默认初始状态

endcase

end

endmodule testbench代码

module sequance_detection_tb();

reg rst_n,clk;

wire x,flag;

wire [2:0] state;

reg [23:0] data;

assign x=data[23];

Sequence_detection u(.x(x),.clk(clk),.rst_n(rst_n),.flag(flag),.state(state));

initial begin

rst_n = 1;

clk = 0;

#2 rst_n=0;

#30 rst_n=1;

data = 'b1001_1101_1011_0101_0011_0011;

#500 $stop;

end

always #10 clk=~clk;

always @ (posedge clk)

data={data[22:0],data[23]};

endmoduleMleay机代码

module Sequence_detection1(x,flag,rst_n,clk,state);

input x,rst_n,clk;

output flag;

output [2:0]state;

wire flag;

reg [2:0]state = 0;

parameter IDLE = 'd0,

A = 'd1, B = 'd2,

C = 'd3, D = 'd4;

assign flag=(state==D && x==1)?1:0;

always@(negedge rst_n or posedge clk)

begin

if (!rst_n)

begin

state <= IDLE;

end

else

casex(state)

IDLE:if(x==0) //第一个码位对,记状态A

begin

state<=A;

end

else state<=IDLE;

A:if(x==1) //第二个码位对,记状态B

state<=B;

else

state<=A;

B:if(x==1) //第三个码位对,记状态C

state<=C;

else

state<=A;

C:if(x==0) //第四个码位对,记状态D

state<=D;

else

state<=IDLE;

D:if(x==1) //第五个码位对,记状态E

state<=B;

else

state<=A;

default:state<=IDLE; //默认初始状态

endcase

end

endmodule testbench代码

module Sequence_detection1_tb();

reg rst_n,clk;

wire x,flag;

wire [2:0] state;

reg [23:0] data;

assign x=data[23];

Sequence_detection1 u(.x(x),.clk(clk),.rst_n(rst_n),.flag(flag),.state(state));

initial begin

rst_n = 1;

clk = 0;

#2 rst_n=0;

#30 rst_n=1;

data = 'b1001_1101_1011_0101_0011_0011;

#500 $stop;

end

always #10 clk=~clk;

always @ (posedge clk)

data={data[22:0],data[23]};

endmodulebehavioral波形图

Moore机

Mealy机

资源利用率:

Moore机

Mealy机

Moore机和Mealy区别:

在实现相同功能时,Moore型状态机需要比Mealy型状态机多一个状态,且Moore型状态机的输出比Mealy型延后一个时钟周期。这样的话Moore机要比Mealy机的反应要慢。Mealy机能更早的得到输出。但是由于Moore机多了一个状态确认,相比Mealy没那么容易出错,可靠性更强。Mealy机输入改变后,输出立刻就会改变,故在不小心的情况下会使电路出大问题。

若本篇文章对您有帮助可以点赞或打赏支持一下作者