如何加速C++开发FPGA ?方法在此拿走不谢

更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们

HLS编译器

咱们英特尔FPGA的粉儿,肯定都知道英特尔发布的高级合成工具——HLS编译器。它可以利用无时序C++生成针对英特尔FPGA优化的生产级高质量RTL代码......简单来说,它能帮助我们的FPGA开发更加有效益。那我们怎样才能对这款新工具快速上手呢?

想快速掌握工具的使用方法?下面这个视频,可千万不要错过哟~

视频链接

无论是什么工具,想要快速使用它,必然要先了解它。现在就让小编来带大家了解学习这款英特尔高级综合HLS编译器吧~

为什么我们要使用HLS编译器?

首先我们要知道,传统硬件设计流程使用的是Verilog/VHDL编码的RTL,这在编码开发项目上的难度可是非常大的,而且复杂、低效。所以,如果客户希望继续使用传统的RTL流程来创建FPGA加速器,那将会变得非常困难。但是,咱们的HLS编译器,它就是为此而生的好工具。

视频链接

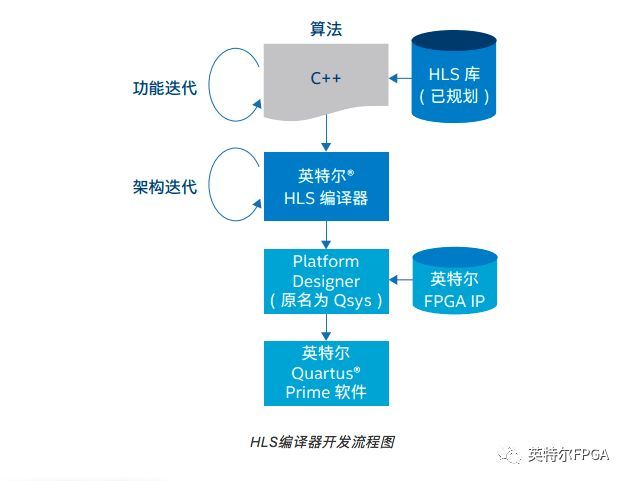

为什么这么说呢?这主要源于它的一个重要功能——能够帮助将C/C++代码转换为RTL,这也是它为大家带来的最大便利。这款英特尔HLS编译器工具,主要适用于掌握了在FPGA上运行的后端流程人员群,它可以帮助用户在C++中创建完整的系统,然后选择在硬件堆栈流程管理程序层中实施的功能。

除此之外,它还可以执行重要的任务,例如通用编译器优化;针对FPGA的特定优化(例如数据路径编排)以及针对特定技术的优化(例如能够在英特尔FPGA上标定硬浮点模块);HLS编译器还能够生成经过优化的生产级高质量RTL代码,再通过Qsys集成到系统设计中,然后通过Quartus编译生成FPGA比特流;也支持用户在CPU上执行C++程序,支持他们以远远高于RTL模拟器事件的速度验证大量代码命令。

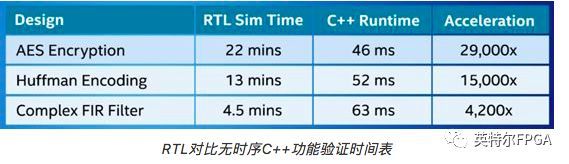

从上图表中,我们可以发现:RTL模拟的功能性调试和验证迭代周期是较长,限制了每天的迭代次数,也意味着延长了FPGA的开发时间;而在C++中开发的模型,其验证速度比RTL快了几个数量级,且所需的代码行减少了80%,明显加快验证速度,提高抽象等级。

如下图, C++相比于RTL在模拟时间方面的数量级缩减。英特尔HLS编译器可加速功能性验证和调试周期,帮助设计师在很短时间内找到并修复错误。

HLS编译器的使用方法——

如果你有认真观看上面的视频,那么你会发现,想要使用这款产品,你就不得不做一些基本的准备:

软件的安装与配置

面向linux系统的有3种基本软件的安装,你都掌握了吗?如果木有掌握,请记得再回头看一下视频哦。小编写着写着也忘了,好像记得有Quartus标准版,还有两个是啥来着?哪位长得好看的如果知道,请劳烦告知大家一下,小编先行谢过!

当然,软件安装好了不一定就是能用滴,你还需要进行相关的配置——包括运行工具shell应该具备的相关库文件、软件的环境变量以及程序路径的设置等(详见视频)。如果你觉得自己的安装和配置都木有问题了,可以试试执行i++命令查看是否OK。如果没有OK的话,那就只有再认真查看视频中的指导说明咯。

示例解析指南

工具结构和使用流程其实在HLS的安装路径中就有相关的示例和教程目录,其中包括CPP文件、Makefile和自述文件等。

我们在上文对HLS编译的了解和分析中有提到其诞生的重要原因——可以把C++转换成RTL。那是不是整个C文件都能被转换为RTL呢?如果不是,那难道是具备某一特定标志的部分才能被转换?答案尽在视频中。(PS:其实C文件中的主函数只相当一个外层,用于仿真测试运行。)

至于Makefile,它有助于运行编译器、处理多样化的输入文件,以及提供更多的优化选项和参数。其中有3个目标对象可供其运行。第二个对象是x86,仅用于检查i++编译器是否能理解所有的语法/结构,它对后续的调试有着极大的帮助。第三个对象是器件,生成了RTL/IP。运行第三个对象后,将会创建一个.prj目录,这个目录又包含了4个基本子目录……更多详情,请观看视频或留言获取。

纸上得来终觉浅,绝知此事要躬行

这款英特尔高级综合(HLS)工具的了解及其使用方法就为大家介绍到这里啦,相信上面的内容足够大家了解和掌握这款工具的使用了。但理论终究是理论,学会了还要去实践哟。祝大家能快速掌握这款HLS工具的使用~

本文转载自XILINX公众号,如涉及侵权,请私信小编删除。

============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。

这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。