自定义IP--转载我之前的blog的内容

1,Xilinx官方为大家提供了很多IP核,用ZYNQ系统设计IP核,最常用的就是使用AXI总线将PS同PL部分的IP核连接起来。

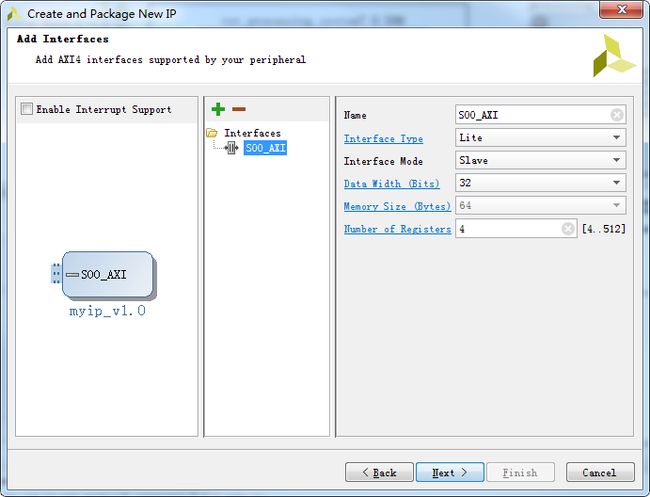

接口是Slave,数据宽度是32位,IP内部的寄存器数量为4个。这样就可以生成一个AXI读写协议的Verilog代码,主要内容就是对4的寄存器进行读写。然后在里面对ip端口的数据进行通信。哪些寄存器配置为只读,只写,可读写模式。

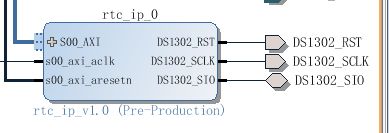

把一些PL端与外部连接的引脚加入,形成AXI接口的IP挂载ZYNQ的AXI总线上。

然后生成对应的硬件比特流,然后就发现RTC的IP映射到ZYNQ的内存空间上,也会生成对应的一些读写API的驱动函数。

#define RTC_IP_mReadReg(BaseAddress, RegOffset) \

Xil_In32((BaseAddress) + (RegOffset))

#define RTC_IP_mWriteReg(BaseAddress, RegOffset, Data) \

Xil_Out32((BaseAddress) + (RegOffset), (u32)(Data)) 实际上就是对gpio操作。

总结:既要理解底层的pl的逻辑时序,又要会使用API函数,比如历程代码:

RTC_IP_mWriteReg (RTC_BASEADDR, 12, 0x00160A0A);

//Write RTC Register3, Setting time, hour=12, month=00, date=00

RTC_IP_mWriteReg (RTC_BASEADDR, 8, 0x000C0000);

//Write RTC Register3, enable time setting

RTC_IP_mWriteReg (RTC_BASEADDR, 12, 0x80160A0A);

for (Delay = 0; Delay < 10000000; Delay++);

//Write RTC Register1, enable time setting

RTC_IP_mWriteReg (RTC_BASEADDR, 12, 0x00160A0A);//为了使能读有效,并没有生效,什么原因?只有去看FPGA代码部分

Verilog的:

if( Time_set_en==1'b1 ) begin i <= i + 1'b1; end

else begin i <= 4'd8; end

所以最后这个写寄存器函数就是为了把Time_set_en信号拉低。