Xilinx Vivado的使用详细介绍(2):综合、实现、管脚分配、时钟设置、烧写

原文链接。 https://blog.csdn.net/jzj1993/article/details/45533769

修改器件型号

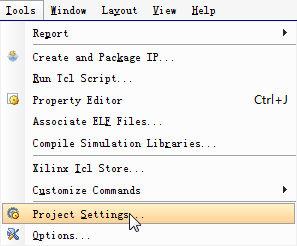

新建工程时选择过器件型号,如果新建好工程后需要修改型号,可以选择菜单Tools - Project Settings。

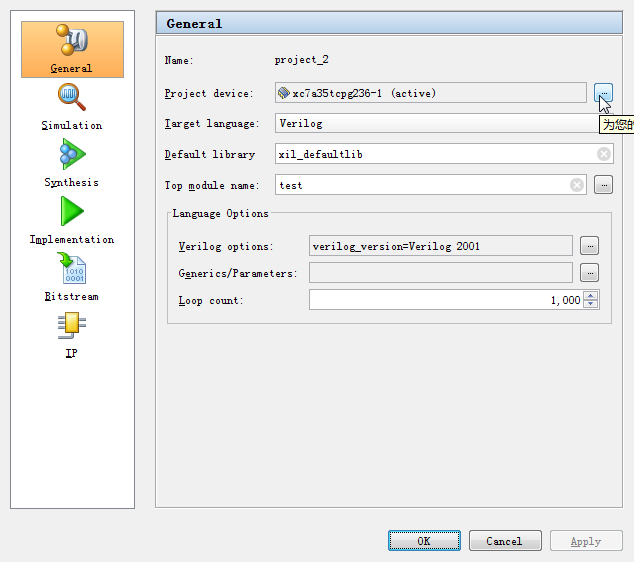

弹出窗口中,点击Project Device右侧的按钮,即可选择器件型号。

综合(Synthesis)

综合类似于编程中的编译。

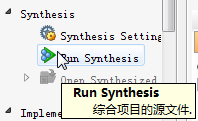

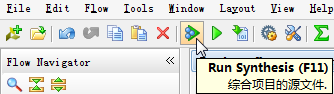

在Flow Navigator或Flow菜单中,选择Synthesis - Run Synthesis;或点击工具栏中的三角形按钮如图,即可开始对设计文件进行综合。

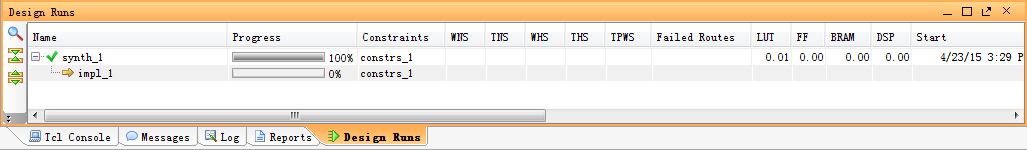

综合以及后面的实现等操作,耗时较长,可以在底部的Design Runs窗口查看进度。

如果没有找到这个窗口,在菜单中选择

Window - Design Runs即可打开。

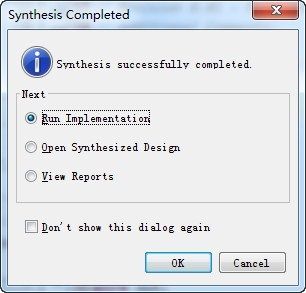

综合完成后,会弹出如下窗口。如果选择第一项并点击OK,就会启动下一步的实现。为了方便学习,这里我们直接点击Cancel。

实现(Implementation)

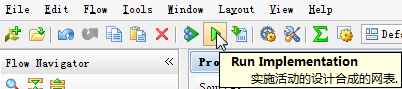

综合完成后,需要进行实现,操作如图。

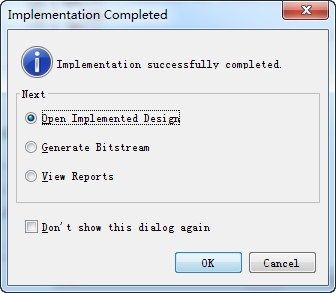

实现完成后,同样会出现一个窗口如下。选择第一项可以打开下一步的IO口设置界面,选择第一项可以启动后面要说的生成比特流操作。同样,这里还是点击Cancel关闭。

IO口配置(I/O Planning)/编辑约束文件(Edit Constraints Sets)

做好的模块,在烧写进板子之前,需要设置输入输出信号与板子上IO口的对应关系。

IO口设置有两种方法,第一种是直接创建并编辑约束文件,第二种是在图形界面进行设置。

编辑约束文件

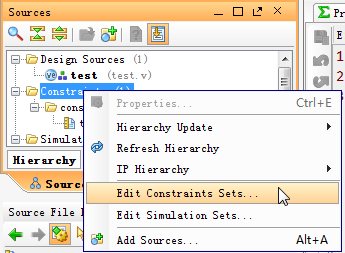

如果对约束文件的格式有了解,IO口的配置,可以直接通过手动编辑约束文件实现。右击文件夹或空白处,选择Edit Constraints Sets。

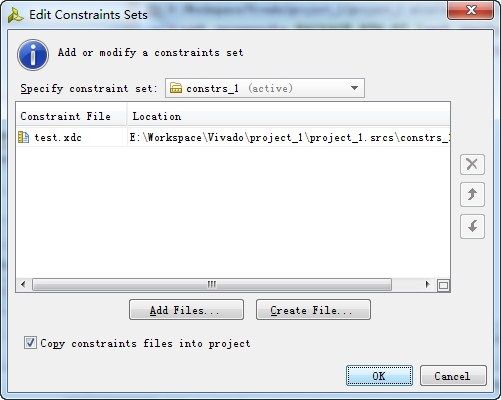

在弹出窗口中添加约束文件,点击OK。

打开文件按格式进行编辑即可。

图形界面配置管脚

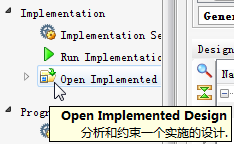

在实现完成后,Open Implemented Design选项从灰色变成可点击状态。

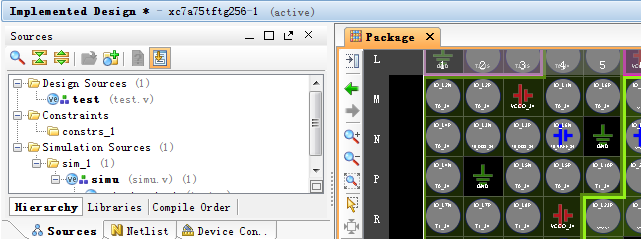

点击Open Implemented Design,即可打开Implemented Design窗口。

在I/O Ports窗口展开管脚,对于每个输入输出信号,在Site栏选择对应的管脚,注意确保Fixed栏处于勾选状态,I/O Std常选择LVCMOS33。

设置好后,Implemented Design窗口标题栏会显示一个*号,表示设置发生了更改。

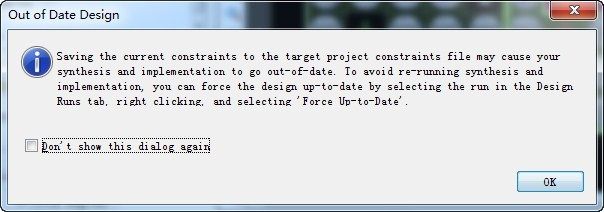

按Ctrl+S快捷键保存设置,会弹出窗口如图,提示保存constraints文件会导致综合与实现过期。也就是说,修改了管脚分配设置后,需要重新进行综合、实现操作。这里点击OK。

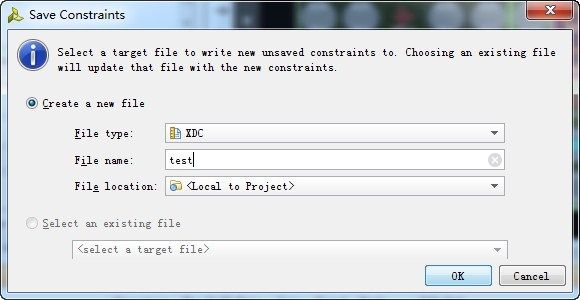

弹出窗口,选择Create a new file并输入文件名,点击OK。

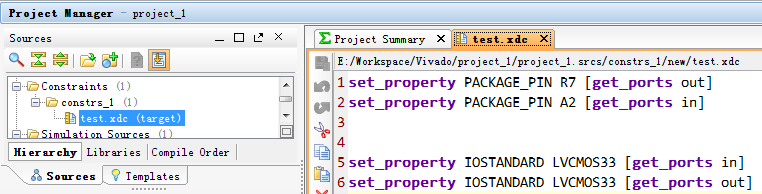

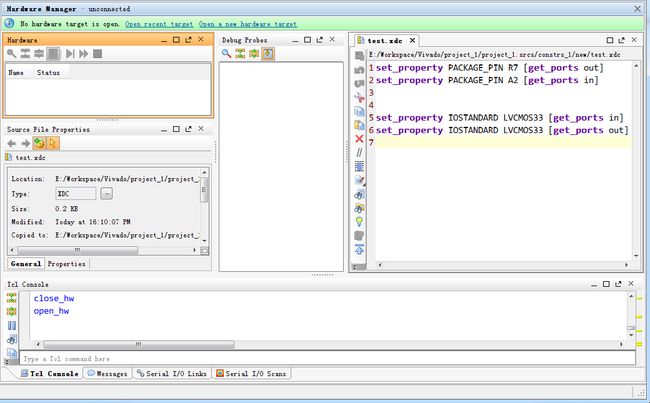

此时test.xdc约束文件已经自动被创建并编辑,可以打开查看。

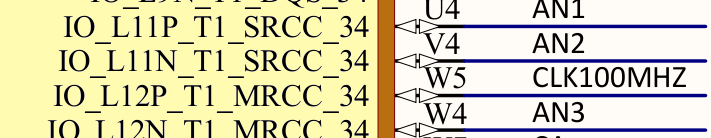

时钟信号

很多电路需要有时钟信号进行驱动,通常在开发板上都有一个外部时钟信号输入。例如在Basys3开发板中,从电路图可以看出,W5管脚外接了一个100MHz的时钟。因此可以设置100MHz时钟输入信号clk对应管脚W5。

如果需要的时钟频率不是100MHz,可以自行编写分频器取得需要的频率,或者配置IP核中的时钟Clocking Wizard来实现。IP核的具体使用方法将在后面再进行介绍。

重新进行综合与实现

IO口设置进行了修改,需要重新综合与实现。

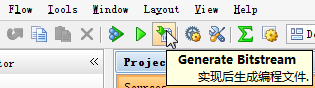

生成比特流

生成比特流文件,这个文件会被直接烧写进板子。类似于编程中的二进制可执行文件。

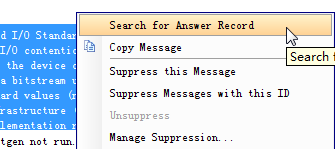

错误处理

由于程序编写问题、管脚分配问题,生成比特流文件容易发生错误。

在Message窗口可以看到发生错误的原因。

右击选择Search for Answer Record可以在论坛搜索这个问题,寻找解决方法。

烧写程序

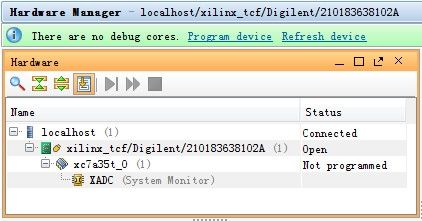

选择Program and Debug - Open Hardware Manager。

Hardware Manager窗口即被打开。

用USB连接开发板。如果之前连接过开发板,直接点击上方绿色栏的Open recent target即可打开;如果是第一次连接开发板,则点击Open a new hardware target。

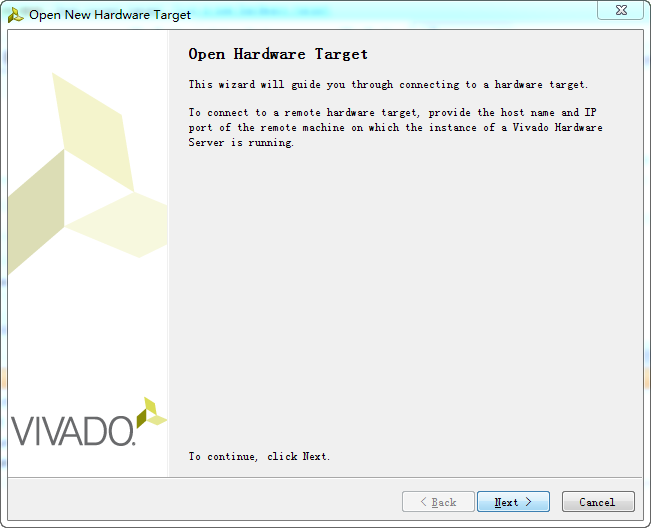

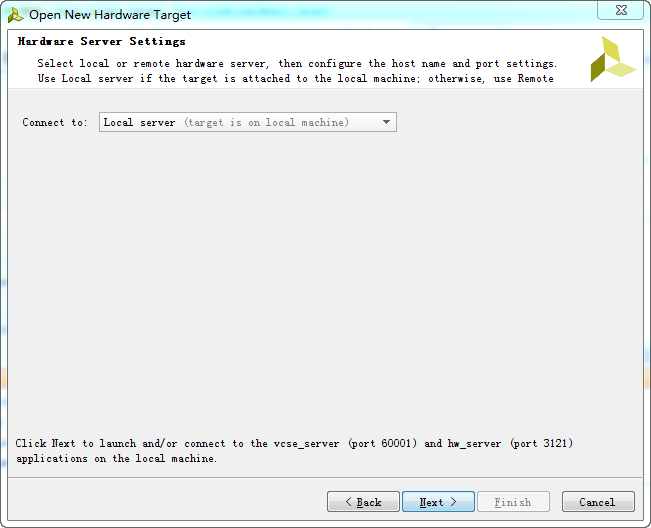

点击Next。

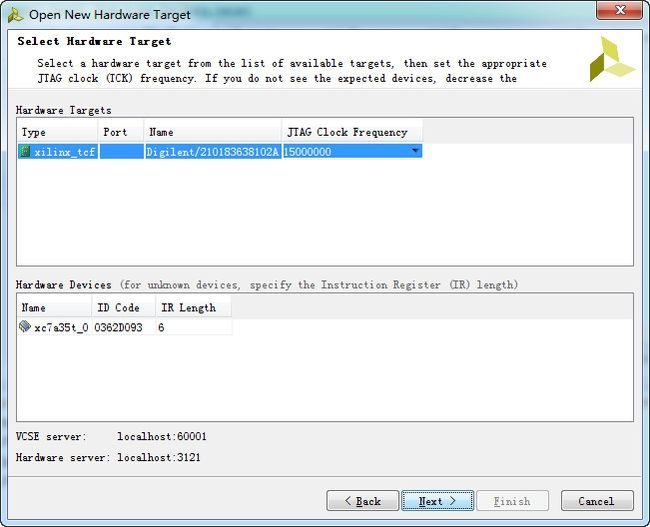

还是点击Next。

显示下面窗口,稍后即可打开硬件设备。

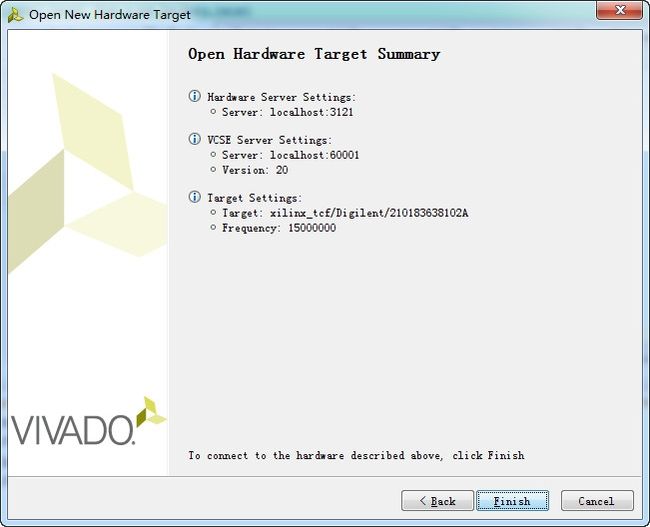

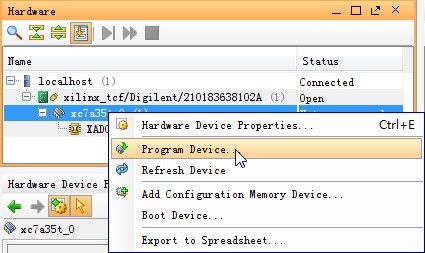

打开设备后,就会在Hardware窗口显示。右击设备并选择Program Device,或者直接点击绿色栏的Program Device。

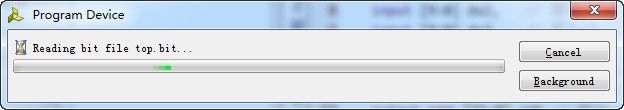

弹出比特流文件选择窗口,一般直接按默认值点击确认,即可烧写程序到板子中。