(4个月前写的)上篇介绍了关于CPU性能两个重要指标之一的架构,过了这么久,也应该把第二篇,关于CPU的工艺(制程)的相关内容补全,两篇结合起来作为一篇「科普文」来供大家一起探讨。

其实在书写这篇之前没有什么思路,因为「工艺」这部分的专业性较强,应该属于电子信息类的范畴,比如有个高大上的专业叫做「微电子学与固体电子学」就是专门研究VLSI(Very Large Scale Integration)的。我所学专业为电气信息类(电气工程及其自动化),更偏强电一些,只接触一些必备的电子技术基础(模拟部分与数字部分,当然只是很浅显的进行了学习)。说来也巧,寒假时候买了一本书《电的旅程》,这本书详细的介绍了电子、电力的发展过程,也给我一些启发,看完这本书,对人类驾驭电子的历史过程有了初步的认识。那好,不如趁热打铁,多看几本关于处理器书来完整知识;不如现学现卖,再以学习笔记的形式记下所学所想。

二 CPU的工艺

首先开宗明义:无论是CPU还是GPU或是其他芯片,更优秀的工艺都是性能提高的重要条件。当一个芯片能借助新工艺容纳更多的晶体管时,就能实现更多的功能和更强大的性能,同时也会有更低的功耗与发热量。回忆上篇内容对于架构的知识,可以发现无论架构设计的再合理,缺少优秀工艺都难以发挥芯片的应有性能。反之,优秀的工艺却能在很多时候弥补芯片设计上的不足。

2.1 0与1

我们知道,计算机特别笨,它只认识数字0和1,即我们所说的二进制:

- 电子线路的电平是高状态时表示 1

- 电子线路的电平是低时状态表示 0

那我们在电路中也很方便表示,如果电路导通便称之为1,电路断开就为0。这些0和1不断的组合,就成为了机器语言。而计算机进行运算,需要N多个开关组合起来,经过组合排列形成逻辑电路,这个逻辑电路越复杂,基本的线路越多,它可以实现的功能就越强大。因此,虽然计算机特别笨,只认识「0」与「1」,但是经过硬件上的排列和软件上的设计,它就却可以实现对人类来说很多繁重的计算任务了。

了解了基本原理,那如何在电路上实现开关功能呢?我们先从熟知的ENIAC说起。

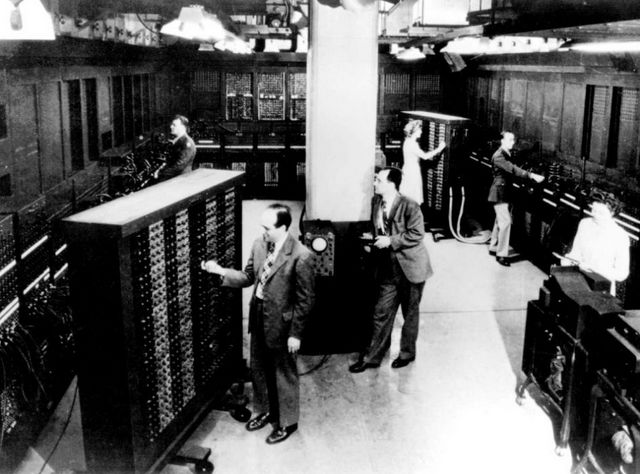

2.1.1 ENIAC

ENIAC的全称是Electronic Numerical Integrator And Calculator,即电子数字积分计算机,我们经常在IT基础课上听到他的名字,毕竟是世界上的第一台计算机嘛。他体积不小,仅仅用了 17468枚真空三极管, 500多万个焊点,重30吨,耗电量 160kW,它在当时的计算能力也是令人咋舌, 每秒可以进行500次计算!不过在现在的人看来,他的计算能力甚至不值一提,因为现在一台平常家用计算机中的微处理器性能就能达到 每秒100多亿次运算,但是耗电量平均只有300W不到!也就是说,计算性能提升了200万倍,耗电量下降到了1/500!从最初的电子计算机到现在仅仅用了60年的时间,到底是是什么让性能的提升如此显著?功劳最大的当然要数从真空管到晶体管再到VLSI的电路技术的进步,下面我们就要介绍,这令人惊叹的 电子时代!

2.1.2 驾驭电子:从真空电子到固态电子再到……

CPU的发展经历了真空管、晶体管、IC和LSI(Large Scale Integration)、VLSI几个时代。总体来说,CPU性能的不断提升得益于人类对于驾驭电子能力的不断进步,也是人类对材料科学、半导体技术方面研究越来越深入的实际表现。

- 第一代:真空管(1957年以前)

时间回溯到20世纪初,弗莱明发明了二极管。没过几年,德福雷斯特在对二极管的研究基础上,发明了真空三极管。真空三极管(triode)拥有用电子讯号控制“开关”的性能,极适合用于高速执行数字型的逻辑及算数运算,我们可以用真空三极管来控制电路的导通与断开,继而形成逻辑电路。具备了理论基础和物质基础,ENIAC的诞生也就是顺理成章的啦。

真空管是个抽成真空的玻璃管,阴极产生电子飞向施加了高电压的阳极,并利用阴极和阳极之间设置的细网格状电极控制电子的流量。电子管的开闭切换速度为微秒级。但是,真空管的阳极需要施加数百伏的高电压,因此耗电量巨大,而且寿命也不是特别长。不过在当时,相较于之前的机械开关的什么巴比奇差分机,人们已经对这个小东西构成的计算机十分的「依赖」啦。 - 第二代:晶体管(1958 - 1963年)

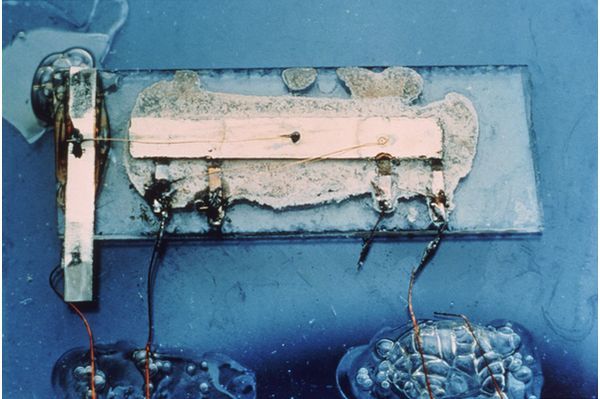

随着驾驭电子能力的进一步增强,同时半导体技术也突飞猛进,科学家终于可以在固态电子方面大施拳脚了。在极富盛名的贝尔实验室,三位伟大的科学家萧克莱(William Shockley)、约翰·巴顿(John Bardeen)和沃特·布拉顿(Walter Brattain)在1947年发明了晶体管(Bipolar transistor)。相较于真空三极管,晶体管在体积、寿命、制作工艺上都有极大的优势。由晶体管构成的计算机更小、更省电,同时运算速度也大幅度的提高。并且因为半导体材料相较于气体来说,科学家更容易控制。随着科学家对半导体研究的进一步深入,纯度和工艺越来越好,晶体管的寿命与稳定性也越来越受到一些芯片厂商的青睐。 - 第三代:集成电路(IC、LSI)(1964 - 1969年)

之前的电路还是分立元件构成,也就是在PCB(印刷电路板)把三极管、二极管焊接起来构成芯片。IC的发明却依赖于来自中国的神秘力量,德州扒鸡公司(大雾),其实是德州仪器(TI)公司的杰克·基尔比(Jack Kilby)啦,他在锗半导体芯片上生成了三极管等多个元件,并在元件之间用细金属连线连接,从而形成了集成电路。

优势是明显的!之前由分立元件构成的100cm²印刷电路板,在集成电路上只需要1mm²的芯片就可以实现相同的功能。至此,LSI将芯片技术领进了一个新的时代,下面的VLSI与LSI的界限并没有那么清晰,只是VLSI作为商家的噱头来说,更加能吸引消费者吧!

- 第四代:大规模集成电路(1970年以后)

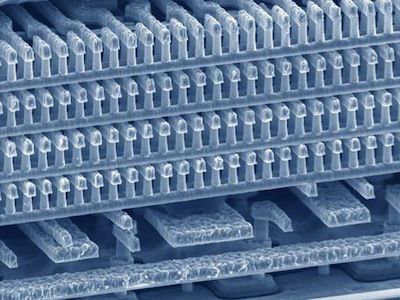

固态电子的不断发展,从晶体管的基础上,人们又继续研究出了FET(场效应晶体管,Field-Effect Transistor),与传统的晶体管相比,控制方式由电流变成了电压,在FET的栅极上加上合适的电压,就可以控制电流。在FET中,一种叫做MOSFET(金属-氧化物半导体场效应晶体管,Metal-Oxide-Semiconductor FET),MOSFET构造简单,在一块IC上的集成密度比三极管还要高,终于,经过四代的发展,「旧时王谢堂前燕」的IC通过VLSI工艺,可以飞入寻常百姓家了!Intel4004

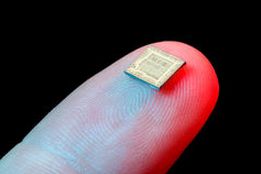

1971年,Intel4004这个划时代产品出现,它使用MOSFET集成电路技术,采用了10μm工艺,集成了2300个MOSFET,别看他这么小,和祖宗ENIAC的计算能力不相上下。25年,ENIAC从30吨越跑越小,最后摇身一变进到3mm*4mm的硅芯片中,功率甚至只有不到1W!

2.1.3 两个定律

2.1.3.1 摩尔定律(Moore's Law)

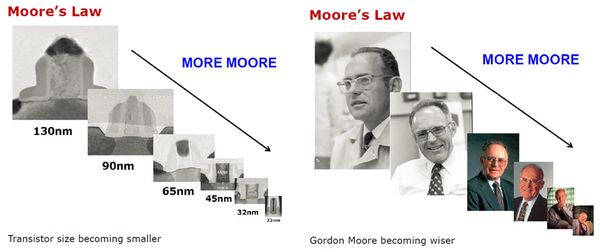

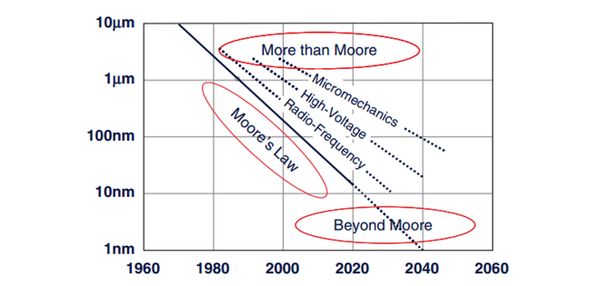

在越来越小的集成电路上放入越来越多晶体管是科学家们不断追求的目标,Intel的创始人之一戈登·摩尔(GordonMoore)在1965年提出一个理论:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。换言之,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。

如今摩尔定律已经过去50年了,集成电路的发展准确的沿着摩尔定律预测的那样前进,不过,在未来几年,摩尔定律有要失效的趋势,为什么呢?我们先看下面这个定律。

2.1.3.1 缩放定律(Dennard scaling)

1974年,IBM公司被誉为内存之父的罗伯特·登纳德(Robert Dennard)MOS晶体管的尺寸与运行速度 耗电量之间的关系,结果发现,如果将尺寸和电源电压减半,MOS晶体管的切换速度将提高两倍,耗电量则降至1/4。我们同时也可以发现,如果将尺寸减半,可以将半导体芯片的面积减至1/4,或者在同样的面积下制造4倍的晶体管。

2.1.4 一个问题

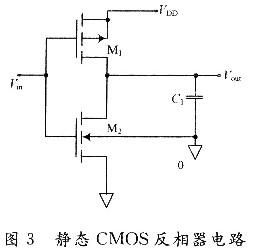

了解了摩尔定律以后,我们或许会想到,芯片在以后会不会尺寸无限小但性能却可以赶超天河二号了呢?恐怕没那么简单,我们看一个CMOS反相器。

简单分析一下原理,CMOS反相器在静止时不会产生电流耗费能量,仅在切换状态时就会有充放电电流,消耗能量为 1/2CV²焦耳(C为寄生电容,V为核心电压)。这些电能最后都成为了热量需要散发出去,主频越高,晶体管的数量越多,那么产生的热量便越多,给处理器散热的压力也就越大。在45nm、32nm、22nm的工艺进化过程中,每次进化C值都会提高1.4倍左右,因此,假设每次进化,同样芯片面积上的核心数加倍,而其他部分不变的话,耗电量就会每次进化增加1.4倍。对于高性能处理器,耗电量带来的热能限制了时钟频率的提高,对于移动设备而言,电池技术在没有技术突破的现有条件下,耗电量较大显然不是一个好消息。当工艺不断进化,还有一个客观事实不可以忽略,由缩放定律表明,C和F(频率)增加必然导致V的降低,这才能抑制耗电量的上升。刚才我们谈到CMOS数字电路在静止状态下不会消耗电能,而其实实际上即使在截止条件下,三极管也会有极其微弱的漏电流,从而缓慢的消耗电能。电源电压减去阈值电压小于一定程度时, 这时候的漏电流已经无法忽视了。那我们就心生疑问了,这可怎么办?难道之前提出的那个问题, 摩尔定律还会延续他的神奇吗?带着问题,我们继续往下看。

2.2 沙子的逆袭

上面一节都是关于工艺的前期准备知识,应该能初步了解计算机通过很多的晶体管构成的集成电路来完成工作的过程,也就是模拟电路器件构成数字电路,来完成预定的任务的过程。上一节都是对于模拟电路中科学家驾驭电子过程的介绍,下面我们具体到一块CPU,看看不同的工艺,对CPU的性能究竟有什么影响。

2.2.1 做个CPU吧

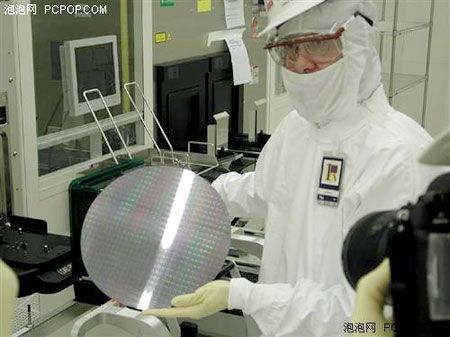

如果问及CPU的原料是什么,大家都会轻而易举的给出答案—是硅。这是不假,但硅又来自哪里呢?其实就是那些最不起眼的沙子。难以想象吧,价格昂贵,结构复杂,功能强大,充满着神秘感的CPU竟然来自那根本一文不值的沙子。当然这中间必然要经历一个复杂的制造过程才行。不过不是随便抓一把沙子就可以做原料的,一定要精挑细选,从中提取出最最纯净的硅原料才行。试想一下,如果用那最最廉价而又储量充足的原料做成CPU,那么成品的质量会怎样,你还能用上像现在这样高性能的处理器吗?接下来的工序简单带过:对硅化学提纯、整形、溶化硅原料,然后将液态硅注入大型高温石英容器。为了达到高性能处理器的要求,整块硅原料必须高度纯净,及单晶硅。然后从高温容器中采用旋转拉伸的方式将硅原料取出,此时一个圆柱体的硅锭就产生了。

2010年最先进的半导体最小尺寸到了22nm,要形成如此细微的线路,只能利用ArF(氟化氩)紫外线激光像银盐照相那样再硅晶圆上进行刻制。ArF激光的波长位193nm,其半波长96.5nm就相当于笔尖。要用它刻出22nm的线路,就像用1mm的自动铅笔绘制0.3的线一样,几乎是不可能的事。现在通过在镜头和硅晶圆之间充满春水,将实际波长缩短到3/4左右,再加上各种其他技术,尽管能勉强达到要求,但已经是极限了。

不断的追求工艺进步,就能在相同的硅晶圆里面刻出更多的基本电路。

如果想看CPU的制作过程,请看下面的链接!

2.2.2 什么是CPU的工艺?

首先说一下,这一部分我只是粗略的了解,大部分内容是源自参考书和知乎,如果想详细了解,请查阅相关教材\参考书!

2.2.2.1 什么是CPU的工艺?

那么到底什么是工艺呢?我查了不少资料,可以总结如下:半导体制程指的是制造芯片的工厂在硅晶圆上可以制造出的MOSFET的最小沟道长度。制程越先进(即这个长度越小),说明这个工厂就拥有更先进的光刻设备来制造这么小的晶体管(晶体管是用光刻在硅晶圆上的)。也就是我们经常在前面说到的,长度越小,可以排布在芯片上的元器件就可以更多,综合之前我们谈到的知识(缩放定律),缩减元器件之间的距离之后,晶体管之间的电容也会更低,从而提升它们的开关频率。

当然,工艺越先进,意味着在硅晶圆可以放下更多的元器件。组件越小,同一片晶圆可切割出来的芯片就可以更多。即使更小的工艺需要更昂贵的设备,其投资成本也可以被更多的晶片所抵消。总结先进的工艺优点如下:

- 性能提高(切换速度提高即主频升高)

- 单位晶体管的成本降低

- 耗电量下降

这三个优点对于芯片设计生产者和消费者来说,好处是显而易见的。可是,工艺要进步,即便是有摩尔定律的加持,可在最近几年也是困难重重,因为随着工艺的提高,硅晶圆在光刻蚀的过程中,也渐渐的力不从心,比方说良品率下降这个最显著的问题。

2.2.2.2 什么是CPU的制程?

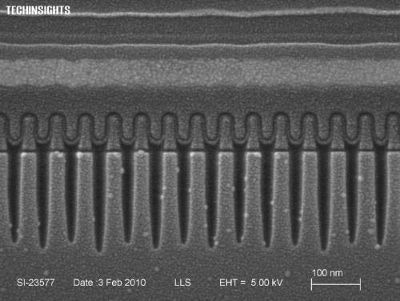

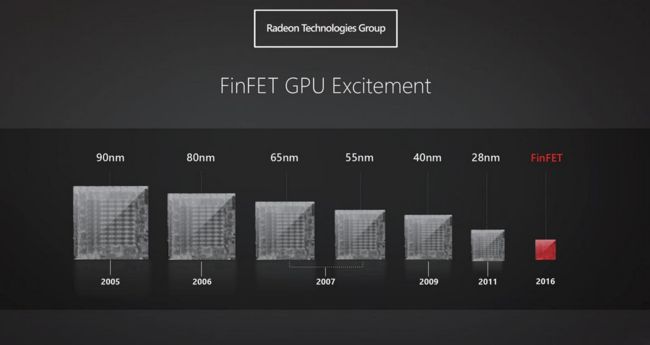

CPU制程指的是MOS管实际制造结束时的栅级引线宽度,也就是栅级多晶硅的宽度。当然,实际中源极和漏极会有少量延伸到栅级下面,所以源极和漏极的实际分隔距离小于栅级宽度。这个有效分开距离被称为有效沟道长度,对晶体管而言是最重要的参数。不过这个参数很难测量,所以一般直接用栅级引线宽度来比较不同的工艺。因此我们常常以闸极长度来代表半导体制程的进步程度,这就是所谓的“制程线宽”。闸极长度会随制程技术的进步而变 小,从早期的 0.18μm、0.13μm,进步到 90nm、65nm、45nm、22nm,再到目前最新制程 10nm。

随着制程的进步,带来了非常多的好处,同时,也会带来很多问题。接下来就说说i3 i5 与 i7处理器和制程进步一些有趣的问题。(背景音乐响起,intel的等 等等~~~~~~ 等~~~)

2.2.3 i3 i5 与 i7

打开京东,到CPU品类里发现,i3要卖700多,i7要卖2000多,咋差这么些钱呢?同一代的处理器,在工艺和架构上都差不多啊,有区别主要是在核心数、主频、缓存大小上,好吧,差了这么多你说忍了,买,毕竟2000多就是壕好好,肯定比那i3高到不知道哪里去了!可是,如果我告诉你,其实,i3、i5其实都(曾经)是i7的话呢?你会不会去炸了intel的老窝呢?好吧,其实应该这么说:i3,i5只是阉割版的i7。

数字电路设计过程并生产之前,是不区分i7,i5或者i3的,只是光刻蚀的流程是不完美的,有可能某些该连着刻开了,很多该刻开的地方没有刻开,导致每一个小器件体质难免有差异比如:第四个核心不能用;频率升到3GHz 以后挂掉;比如它在缓存功能上有缺陷(这种缺陷足以导致绝大多数的CPU瘫痪)等等。这时候,扔掉太浪费!那该怎么版呢?合理的做法就是将“坏区”隔离起来,只用其中能用的地方,并锁定在安全的频率下工作,屏蔽掉一些缓存容量,降低了性能,当然也就降低了产品的售价。也有一种办法,就是给处理器增加冗余块。处理器增加了冗余块,芯片面积会变成9/8倍,但整体面积会降到0.62倍,因此能节省38%的成本。

所以说,700多的i3和2000多的i7其实是一个成本……不过,又说明个问题,体质好的人就是比体质差的的人要受欢迎啊:)

2.3 展望未来

1971年的第一片微处理器Intel 4004使用了大约2300个晶体管,而2010年的微处理器集成了大约几亿甚至十几亿个晶体管。40年中的VLSI中集成的元件数目增加了数十万甚至上百万倍。那以后呢?似乎半导体工艺已经进入了瓶颈,工艺的发展还会在高速公路上向前快速行驶吗?

2.3.1 一个答案

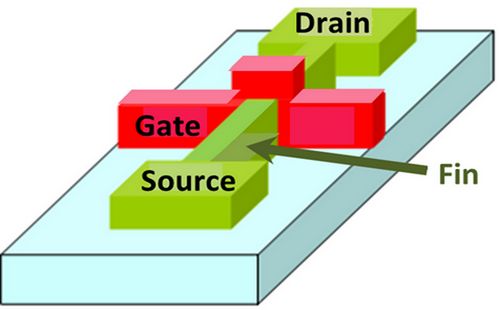

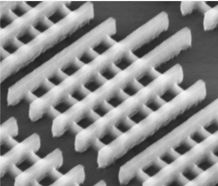

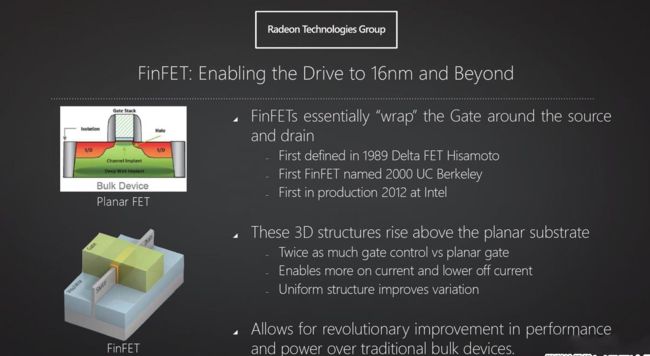

正如摩尔定律预测的那样,芯片工艺在不断进步,同样尺寸的芯片上塞入了越来越多的元件,可又受到缩放定律的限制,漏电流再也无法忽视了,这是由于CMOS的固有物理特性决定了,想要继续沿着摩尔定律预测向前进的话,必须在半导体工艺上有所突破,就像前几代那样。那么,现在是什么支撑摩尔定律的呢?其中的一个答案就是使用FinFET封装。

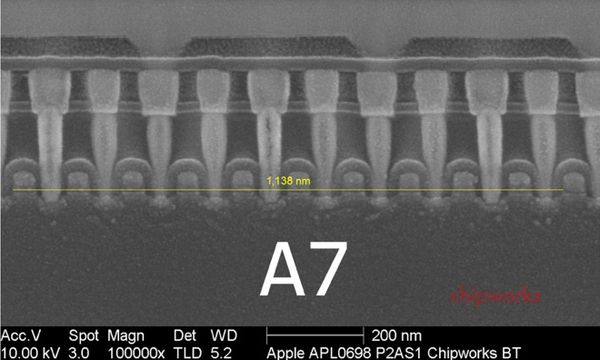

FinFET实际上就是当时英特尔大力宣传的“3D晶体管”,从技术角度来看,FinFET将原本扁平、薄而不可靠的漏极和源极之间的连接“竖立”起来,在另一个维度上变相增加了厚度(或者面积),使得晶体管在继续缩小后还能够有比较好的性能表现。在使用了FinFET后,原本比较令人烦恼的漏电电流得到了有效控制,同时还带来了很多优秀特性,比如使用更低电压即可驱动、晶体管可承受电流上限也更高等。

采用FinFET封装的目前可以继续让摩尔定律成功的预测下去,并且以后还有更多的办法,但是不得不承认的是,现在工艺的提升已经没有之前那样的飞速了。

2.3.2 Tick-Tock

在上一篇我们谈到了Intel公司著名的「Tick-Tock」战略,也就是分别在奇数年和偶数年来更新架构和工艺。Intel大概是在十年前提出的,依靠这个已经领先竞争对手好几代,不过现在,最近在公司文档中废止了“Tick-Tock”的芯片发展周期,从下一代10纳米制程CPU开始,英特尔会采用“制程-架构-优化”(PAO)的三步走战略。

在发展到14nm制程时,Intel已经“力不从心”,最新一代架构Skylake的发布时间比预料晚半年。当进入10nm制程后,原本的芯片周期已经无法适应每年发布一代CPU,Intel必须延长每一代制程的生命周期,也就是说每一代制程将沿用3年,共发布3代CPU。10nm制程还将面临芯片制造的难题,因为10nm仅仅相当于20个硅原子宽度。Intel在文档中表示,优化芯片制程和架构将维持每年发布一代CPU的市场需求。

不知道Intel到底是因为竞争对手不给力(AMD:我还会做PPT!),还是战略有意为之,还是真的在工艺制程上出现了瓶颈,作为科技爱好者或者是消费者,也可以隐约的感到,相较于架构,工艺的「军备竞赛」已经逐渐降温了。

2.4 谈谈其他

2.4.1 台积电(TSMC)

台湾积体电路制造公司(TSMC,Taiwan Semiconductor Manufacturing Company),是台湾一家半导体制造公司,成立于1987年,是全球第一家、以及最大的专业集成电路制造服务(晶圆代工)企业。宝岛湾湾在20世纪80年代末期,由于传统工业收到了严重的局限,在当时台湾地区领导人蒋经国的指示下,台湾要大力发展半导体工业,此时,TSMC就应运而生了。 之前我们介绍了,很多芯片厂商通过对架构的改进,绘制与设计集成电路,而生产,需要交付给有能力生产的厂家去。台积电专门性的对芯片设计顾客提供最佳生产制造服务,因为自己没有产品,对所有顾客都没有直接利益冲突。台积电不需要设计市场上瞬息万变的芯片产品,只要把精力集中在提供最先进的制造技术与服务上,以静制动。打个比方,芯片设计者就像是书的作者,内容及表达技巧才是一本书的精华。而芯片生产商就是书籍印刷厂,只有将书稿发给印刷厂来印制,才能将想表达的东西实现。

随着摩尔定律的演变,晶体管越变越小,但硅晶圆则越来越大,每一片硅晶圆上可容纳更多芯片,因为可降低每片芯片的成本。但是,掌握这个技术的公司并不多,我们现在了解的只有台积电、三星、Intel等等,因为这个行业的前期投资非常大,只有良性循环的企业才能生存下来。

所以之前有人提出,世界上其实只需要3家芯片厂和他们的产品就够了:英特尔的微处理器、韩国三星的DRAM内存、以及台积电的晶圆代工,来生产所有其他公司的设计。

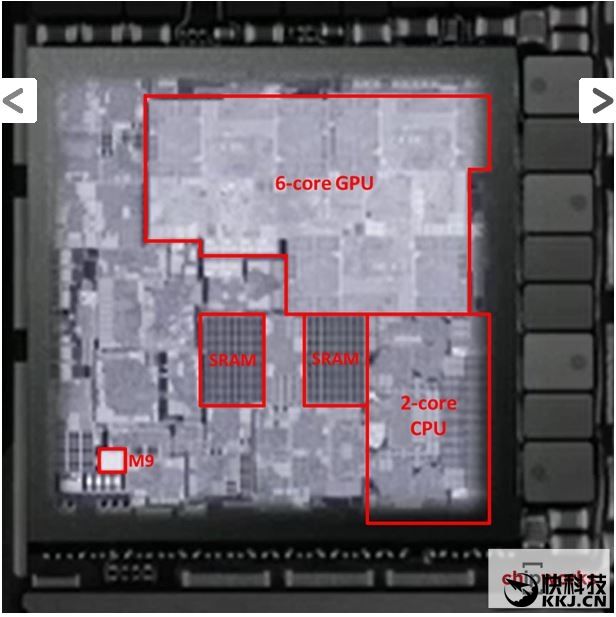

2.4.2 苹果6s的处理器

在苹果6s发布会后,果粉和科技人士都高潮了,不仅是因为又可充值信仰了,而是因为6s并没有和6长的没什么不同!开玩笑的。

在苹果6s上搭配了最新的A9处理器,当时科技新闻标题如下:「iPhone 6S A9处理器称霸全球!安卓集体崩溃」、「号称秒80%桌面PC:苹果A9系列达到桌面级」、「主流手机CPU跑分对比:苹果A9单核默默全秒杀」。看起来一切悲壮,除了高通骁龙810不给力以外,只能赞叹苹果在处理器设计上的登峰造极了。

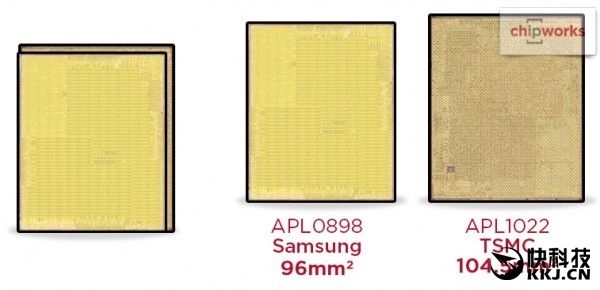

不过当6s发售,消费者纷纷拿到最新的6s手机时,一个争议出现了,好像分了两个厂家代工6s啊,分别是三星和台积电,按道理说制程差不多、架构一样,好像在实际表现上差了很多呢?下面一起来看看。

「A9台积电完爆三星!iPhone 6S现大范围退货潮」,这是当时的标题,问题出在哪?

iPhone 6S A9处理器上有两个版本,一个是出自台积电,而另外一个是三星,前者基于16nm制程,而后者则是14nm制程,由于工艺上的不同,导致它们性能、续航上有了不同。

A9处理器的不同,让iPhone 6S的表现也不一样,如果性能上的差距还能忍受的话,那么续航上的不同,则是用户最难受的,毕竟这是硬伤。

不少国外网友纷纷在Reddit上晒出的自己的实测成绩,即同样设置、使用情况下,搭载台积电A9的iPhone 6S续航要比三星A9长近两个小时。

2.4.3 安迪-比尔定律

安迪是原英特尔公司 CEO 安迪·格鲁夫(Andy Grove),比尔就是微软的创始人比尔·盖茨。在过去的二十年里,英特尔处理器的速度每十八个月翻一番,计算机内存和硬盘的容量以更快的速度在增长。但是,微软的操作系统等应用软件越来越慢,也越做越大。所以,现在的计算机虽然比十年前快了一百倍,运行软件感觉上还是和以前差不多。而且,过去整个视窗操作系统不过十几兆大小,现在要几千兆,应用软件也是如此。虽然新的软件功能比以前的版本强了一些,但是,增加的功能绝对不是和它的大小成比例的。因此,一台十年前的计算机能装多少应用程序,现在的也不过装这么多,虽然硬盘的容量增加了一千倍。更糟糕的是,用户发现,如果不更新计算机,现在很多新的软件就用不了,连上网也是个问题。而十年前买得起的车却照样可以跑。安迪-比尔定理,即比尔要拿走安迪所给的。

What Andy gives, Bill takes away.

我想大家肯定也有这样的感觉,电脑越用越慢、手机越用越卡。这就是这定律最真实的体现咯。

2016年3月21日,安迪·格鲁夫离我们而去了,R.I.P.

2.4.4 量子力学

不懂量子力学,只是引用一位网友的回复,抛砖引玉。

单原子大小工艺?小编无知就不要瞎说。听说过量子力学吗?知道隧道效应吗?几纳米下隧道效应已经够明显了,这种情况下,“1”有很大的概率变成“0”,晶体管就变得不稳定。这就是现在摩尔定律失灵的原因。以前18个月集成度翻一翻,现在呢?

2.5 后记

写作的感觉只有一个就是,累。不断的查资料,并且还要综合、总结。蹲坑的时候在反复看,下课的时候在反复看,有时候有了灵感抓紧写下来,还要不断修改、不断删改,说来也搞笑,居然做梦也在写写写。

不过终于写完了,觉得好轻松。在Deadline之前完成了,当作给自己的生日礼物吧!

当然,写的肯定还是漏洞百出,希望大家可以多多给予批评和意见!谢谢大家!

2.6 一些感想

计算机发展的如此快,最重要的就是芯片发展的速度远远的超过了其他方面的发展速度。而芯片之所以可以发展的这么快,硅谷发挥的作用功不可没。不管是因为美国政府或者是军方在这方面肯投资,更多的是美国给科学家创造了一个优良的环境,让他们可以专心于自己的工作,如前文所说,发展的速度快也就是顺理成章了。基础物理、材料物理、材料科学、半导体科学等等等,需要社会有一个好的大环境来让这些方面的科学家沉下心来专心于自己的研究方向,有时候我也在想,我们的贝尔实验室会出现在哪里呢?我们的硅谷出现在哪里呢?又是一个问题,希望十年后、二十年后我可以再来写一篇blog,给出一个答案。

------------------------分割线------------------------

若需转载,请留言或联系我!请尊重劳动成果!

本文援引了很多的数据、观点、资料,若有侵权,立删!

部分参考资料:

书籍:

《电的旅程:探索人类驾驭电子的历史过程》(张大凯)湖南科技出版社

《浪潮之巅》(吴军)电子工业出版社

《支撑处理器的技术:永无止境地追求速度的世界》(Hisa Ando,李剑 译)电子工业出版社 本文很多资料都出自于此,五星推荐!

视频:

CPU的制造过程(Intel Chip with 22nm 3D Transistors):

http://v.youku.com/v_show/id_XNjIxNTgyNTQ4.html

网络:

难道上帝的电脑慢了?

http://weibo.com/ttarticle/p/show?id=2309403958723717545653

CPU 的摩尔定律是不是因为 10 纳米的限制已经失效了?10 纳米之后怎么办?:

https://www.zhihu.com/question/26446061

如果芯片工艺发展不能满足摩尔定律,是否会引发 IT 界的一场创新?:

https://www.zhihu.com/question/22225070

CPU 每一代之间的差距体现在什么地方?:

https://www.zhihu.com/question/22365274

Intel i3 和 i7 的成本差是多少?如果成本相当,为什么不全生产 i7 呢?:

https://www.zhihu.com/question/23919992

工艺架构双双逆袭 AMD下代显卡抢先看!:

http://cniti.com/index.php/article/index/id/14772/viewall/1

Tick-Tock终结:Intel宣布3年更新一次制程:

http://news.mydrivers.com/1/475/475221.htm

台积电:20nm输掉底裤 16nm秒杀三星!:

http://news.mydrivers.com/1/450/450666.htm

A9台积电完爆三星!iPhone 6S现大范围退货潮:

http://news.mydrivers.com/1/450/450950.htm

iPhone 6S芯片门?苹果自己设计有问题:

http://news.mydrivers.com/1/453/453138.htm

FinFET是什么? 移动14nm战斗正式开始:

http://news.imobile.com.cn/articles/2015/0303/151149.shtml

解析CPU制造全过程:如何由一堆沙变成集成电路:

http://tech.163.com/07/0709/09/3IUVDJF6000926PT.html

为何14nm芯片更强?科普浅谈“制程工艺”:

http://network.pconline.com.cn/579/5797876.html