- Verilog呼吸灯项目实战指南

酸甜草莓二侠

本文还有配套的精品资源,点击获取简介:本项目“breathLED.zip”详细介绍了利用Verilog硬件描述语言实现呼吸灯效果的完整流程。从Verilog基础到C语言仿真,再到实际的Verilog仿真、工程建立和硬件烧录,详细讲述了在FPGA设计中的每个关键步骤。涵盖了时钟信号定义、计数器和比较器的设计、Testbench编写、编译综合、布局布线以及最终的硬件烧录与调试。本项目不仅提供了实践指南

- [读书日志]8051软核处理器设计实战(基于FPGA)第六篇:8051软核处理器指令支持添加(verilog)

JoneMaster

JM读书日志系列fpga开发

5.4为主体程序添加指令接下来我们来为主体程序添加指令。在开始之前,我们有必要先把目前的代码展示出来://`defineTYPE8052moduler8051(inputwireclk,inputwirerst,inputwirecpu_en,inputwirecpu_restart,outputregrom_en,outputreg[15:0]rom_addr,inputwire[7:0]rom

- FPGA USB2.0串口通信项目设计与实现

瞬泉

本文还有配套的精品资源,点击获取简介:本项目主要围绕FPGA(Field-ProgrammableGateArray)和Verilog语言,实现USB(通用串行总线)2.0标准的串口通信功能。项目涵盖了从时钟配置到物理层接口的全套设计过程,包括UART通信的帧同步、波特率生成、握手协议等。项目文档和代码可能包含Verilog代码文件、测试平台配置、波形记录文件、编译脚本和用户手册,以助于开发者理解

- FPGA开发中的团队协作:构建高效协同的关键路径

whik1194

fpga开发

一、团队成员角色与职责FPGA工程师核心设计:负责FPGA的逻辑设计与代码实现,依据项目需求,运用硬件描述语言(如Verilog或VHDL)完成模块功能编写。例如在设计一个高速数据采集系统时,编写数据采集、缓存及预处理的逻辑代码。功能仿真与验证:使用仿真工具对所编写的代码进行功能验证,确保逻辑设计符合预期。像在完成数字滤波器模块代码后,通过仿真测试不同输入信号下的输出,检查滤波效果。时序分析与优化

- 自己动手写CPU - 1

qq85058522

自己动手写CPUfpga开发

电脑,手机,单片机,都有一个核心部件:CPU.今天开始学verilog,就尝试一下动手写一个可以工作的CPU.目标就是可以计算从1加到10等于几?分析一下,大概需要几个指令:LdrAddSubCmpJmp第一步,先写一个运算部件:ALU.modulealu0(input[3:0]op,input[7:0]in1,in2,outputreg[7:0]out1);always@(*)begincase

- 【自用】Verilog笔记

QCCX_bY

笔记

一、语法1、模块moduletest(A,B,C,D,F1,F2);//test为模块名inputA,B,C,D;//输入端口,默认为wire类型信号,一般都是wireoutputF1,F2;//输出端口,默认wirewireF1;//连线reg[2:0]F2;//3bit寄存器endmodulemoduletop_module(inputa,inputb,outputout);//模块实例化语法

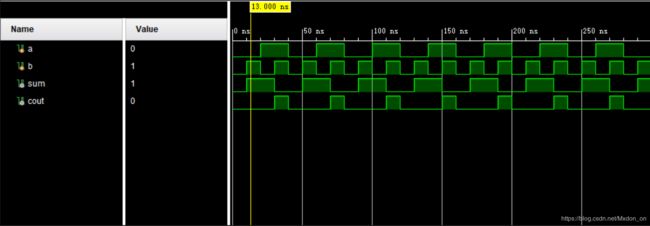

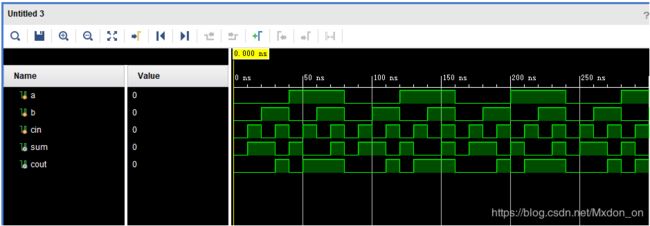

- [Mac + Icarus Verilog + gtkwave] Mac运行Verilog及查看波形图

Xminyang

MacVerilogHDLmacosverilog

目录1.MAC安装环境1.1IcarusVerilog编译1.2gtkwave查看波形2.安装遇到的问题2.1macOScannotverifythatthisappisfreefrommalware2.2gtkwave-binisnotcompatiblewithmacOS14orlater3.运行示例3.1源代码3.2编译Verilog3.3生成.vcd文件3.3查看波形3.4脚本运行参考1.

- Verilog中阻塞赋值和非阻塞赋值的区别?

张小侃

数字IC知识fpga硬件

阻塞赋值“=”对应组合逻辑电路赋值(无存储功能,立即赋值),并且会阻塞后面的赋值操作,非阻塞赋值“<=”对应时序逻辑电路赋值(有存储功能),所有非阻塞赋值操作在同一时刻进行赋值。下面分别通过vivado综合不同情况赋值的代码。第一种:在时序逻辑电路中使用阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路时立即执行赋值操作,和组合逻辑电路特性一致,无缓存功能,out_o直接被优化掉了。alw

- FPGA Verilog 阻塞赋值和非阻塞赋值

杭州秃头程序猿

fpga开发嵌入式硬件

阻塞赋值和非阻塞赋值的区别阻塞赋值阻塞赋值(=)必须是阻塞赋值完成后,才进行下一条语句的执行;赋值一旦完成,等号左边的变量值立即变化。串行,立即生效。如b=a;赋值语句执行完后,块才结束。b的值在赋值语句执行完后立刻就改变的。可能会产生意想不到的结果。非阻塞赋值非阻塞赋值(<=),在赋值开始时计算表达式右边的值,在本次仿真周期结束时才更新被赋值变量,即赋值不是立即生效的;非阻塞赋值允许块中其他语句

- 分频器code

一条九漏鱼

verilog开发实战指南fpga开发

理论学习数字电路中时钟占有非常重要的地位。时间的计算都依靠时钟信号作为基本单元。一般而言,一块板子只有一个晶振,即只有一种频率的时钟,但是数字系统中,经常需要对基准时钟进行不同倍数的分频,进而得到各模块所需的频率。若想得到比系统时钟更慢的时钟,可以将基准时钟进行分频。若想得到比系统时钟更快的时钟,可以将基准时钟进行倍频。不管是分频还是倍频,都通过PLL实现或者用verilog描述实现。我们用ver

- verilog中的阻塞赋值和非阻塞赋值的仿真

DL_Zl

Verilog数字电路设计verilogsystemverilog

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、阻塞赋值语句二、非阻塞赋值语句总结前言Verilog中的赋值语句类型主要分为两类,阻塞赋值语句和非阻塞赋值语句,关于赋值赋值语句和非阻塞赋值语句的区别,下面我们将通过实际代码以及仿真结果来进行形象的讲解。一、阻塞赋值语句阻塞赋值操作实质上是一次性连续完成的,即计算等号右边变量(或表达式)的值并立即赋值给等号左边的变量。

- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (121)DAC接口--->(006)基于FPGA实现DAC8811接口

FPGA系统设计指南针

FPGA接口开发(项目实战)fpga开发FPGAIC

1目录(a)FPGA简介(b)IC简介(c)Verilog简介(d)基于FPGA实现DAC8811接口(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电

- FPGA复位专题---(3)上电复位?

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发

(3)上电复位?1目录(a)FPGA简介(b)Verilog简介(c)复位简介(d)上电复位?(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- Quartus sdc UI界面设置(二)

落雨无风

IC设计fpgafpga开发

Quartussdc设置根据一配置quartus综合简单流程(一)上次文章中,说了自己写sdc需要配置的分类点,这次将说明在UI界面配置sdc。1.在Quartus软件中,导入verilog设计之后,打开Tools/TimeQuestTimingAnalyzer界面大致分为上下两部分,上半部分左侧显示Report、Tasks,右侧显示欢迎界面;下半部分显示Console和History,此处缺图,

- 牛客Verilog语法刷题Day 1

SAChemAdvance

刷题fpga开发

校验器的输入是由原始数据位和校验位组成对于奇偶校验,若合法编码中奇数位发生了错误,也就是编码中的1变成0或0变成1,则编码中1的个数的奇偶性就发生了变化,从而可以发现错误,但不能检测出是哪些位出错。对于一个设置为50MHz的移位寄存器,把16左移到128,需要()nsA.30B.40C.50D.60本题答案选D,从16到128需要3位,50MHz的时钟为20ns,移动3位则为60ns时间(s)=1

- 连续发送多个数据(uart串口RS232协议/verilog详细代码+仿真)

勇敢牛牛(FPGA学习版)

fpga开发嵌入式硬件matlab智能硬件

写在前言以下内容详细源文件,已经上传个人主页资源,需要自取~目录写在前言需求分析UART简介整体架构流程小结需求分析使用串口(rs232协议)间隔1s连续发送16byte的数据。由于每次发送的数据只有8bit,16byte=128bit,所以要发送16帧。UART简介这里实验所使用的参数有:rs232通信协议+9600bps+quartus18.0+modelsim2020异步通信:UART是一种

- 第11周作业---HLS编程环境入门

pss_runner

目录HLS概念HLS是什么HLS与VHDL/Verilog有什么关系?HLS技术问题HLS开发步骤环境搭建编写test.cpp文件预编译cpp文件HLS概念HLS是什么高层次综合(High-levelSynthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时

- VCS简介

XtremeDV

VCS快速实战指南

1.2.1关于VCSVCS是VerilogCompiledSimulator的缩写。VCSMX®是一个编译型的代码仿真器。它使你能够分析,编译和仿真Verilog,VHDL,混合HDL,SystemVerilog,OpenVera和SystemC描述的设计。它还为您提供了一系列仿真和调试功能,以验证您的设计。这些功能提供了源码调试和仿真结果查看功能。vcs提供了一系列的feature,如下图:业界

- vcs 入门

hemmingway

Xilinx/FPGA

synopsysvcs软件是仿真和验证的软件,必须掌握。vcs即verilogcompilesimulator支持verilog,systemVerilog,openvera,systemC等语言,同时也有代码覆盖率检测等功能。可以合第三方软件集合使用,例如Vera,Debussy,Specman等等。在linux下调用vcs,需要设置相应的环境变量。1、学习vcs最好的资料肯定是官方的说明书,安

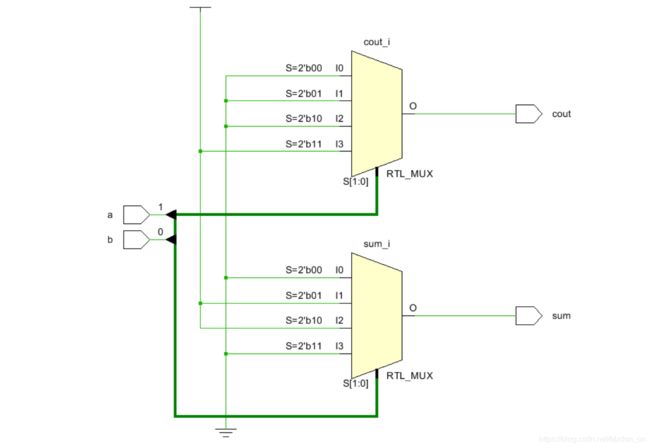

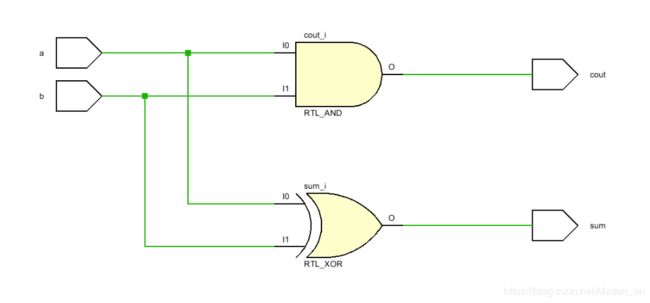

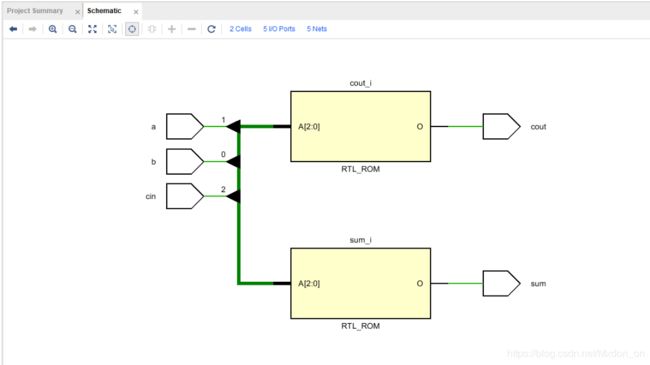

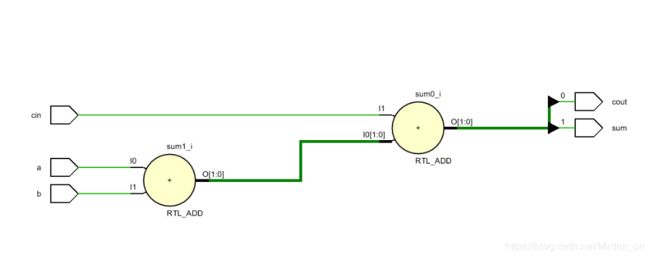

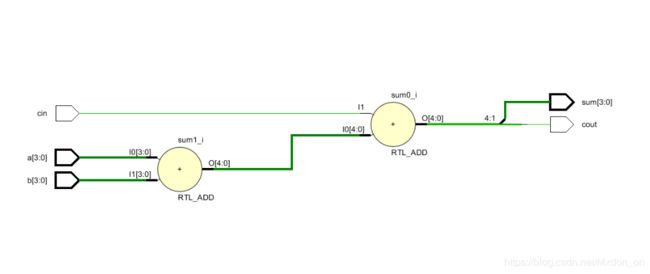

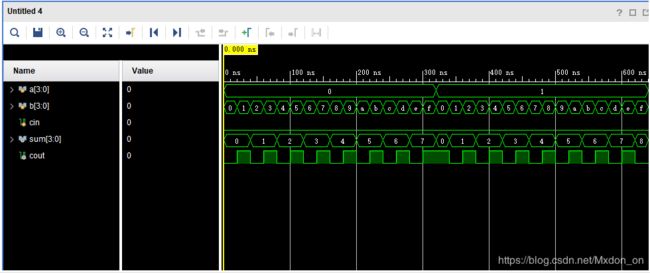

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- 1. Verilog2. C语言3. 数组4. 关键词5. 模块

行者..................

c语言fpga开发开发语言FPGA

###5.2.4Verilog数组VSC语言数组####Verilog数组在Verilog语言中,数组通常被称作内存。以下是一个定义的例子:```verilog(*ram_style="distributed"*)reg[0:31]MyMem[0:7]```这行代码定义了一个长度为32位,包含7个元素的数组。具体来说:-`reg[0:31]`表示每个数组元素是一个32位的寄存器。-`MyMem[0

- (170)时序收敛--->(20)时序收敛二十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 初识 Verilog

栀栀栀

笔记

Verilog综述:类C,并行,自顶向下,硬件描述语言,VHDL,VerilogHDL。VHDL,VerilogHDL,两种不同描述语言。Verilog语言(并行,硬件)类似C语言(串行,软件)。基础知识:1.Verilog的四值逻辑系统0低电平1高电平X不确定Z高阻态2.Verilog的数据类型寄存器数据类型表示一个抽象的数据存储单元,只能在always语句和initial语句等过程语句中被赋值

- jQuery 键盘事件keydown ,keypress ,keyup介绍

107x

jsjquerykeydownkeypresskeyup

本文章总结了下些关于jQuery 键盘事件keydown ,keypress ,keyup介绍,有需要了解的朋友可参考。

一、首先需要知道的是: 1、keydown() keydown事件会在键盘按下时触发. 2、keyup() 代码如下 复制代码

$('input').keyup(funciton(){

- AngularJS中的Promise

bijian1013

JavaScriptAngularJSPromise

一.Promise

Promise是一个接口,它用来处理的对象具有这样的特点:在未来某一时刻(主要是异步调用)会从服务端返回或者被填充属性。其核心是,promise是一个带有then()函数的对象。

为了展示它的优点,下面来看一个例子,其中需要获取用户当前的配置文件:

var cu

- c++ 用数组实现栈类

CrazyMizzz

数据结构C++

#include<iostream>

#include<cassert>

using namespace std;

template<class T, int SIZE = 50>

class Stack{

private:

T list[SIZE];//数组存放栈的元素

int top;//栈顶位置

public:

Stack(

- java和c语言的雷同

麦田的设计者

java递归scaner

软件启动时的初始化代码,加载用户信息2015年5月27号

从头学java二

1、语言的三种基本结构:顺序、选择、循环。废话不多说,需要指出一下几点:

a、return语句的功能除了作为函数返回值以外,还起到结束本函数的功能,return后的语句

不会再继续执行。

b、for循环相比于whi

- LINUX环境并发服务器的三种实现模型

被触发

linux

服务器设计技术有很多,按使用的协议来分有TCP服务器和UDP服务器。按处理方式来分有循环服务器和并发服务器。

1 循环服务器与并发服务器模型

在网络程序里面,一般来说都是许多客户对应一个服务器,为了处理客户的请求,对服务端的程序就提出了特殊的要求。

目前最常用的服务器模型有:

·循环服务器:服务器在同一时刻只能响应一个客户端的请求

·并发服务器:服

- Oracle数据库查询指令

肆无忌惮_

oracle数据库

20140920

单表查询

-- 查询************************************************************************************************************

-- 使用scott用户登录

-- 查看emp表

desc emp

- ext右下角浮动窗口

知了ing

JavaScriptext

第一种

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/

- 浅谈REDIS数据库的键值设计

矮蛋蛋

redis

http://www.cnblogs.com/aidandan/

原文地址:http://www.hoterran.info/redis_kv_design

丰富的数据结构使得redis的设计非常的有趣。不像关系型数据库那样,DEV和DBA需要深度沟通,review每行sql语句,也不像memcached那样,不需要DBA的参与。redis的DBA需要熟悉数据结构,并能了解使用场景。

- maven编译可执行jar包

alleni123

maven

http://stackoverflow.com/questions/574594/how-can-i-create-an-executable-jar-with-dependencies-using-maven

<build>

<plugins>

<plugin>

<artifactId>maven-asse

- 人力资源在现代企业中的作用

百合不是茶

HR 企业管理

//人力资源在在企业中的作用人力资源为什么会存在,人力资源究竟是干什么的 人力资源管理是对管理模式一次大的创新,人力资源兴起的原因有以下点: 工业时代的国际化竞争,现代市场的风险管控等等。所以人力资源 在现代经济竞争中的优势明显的存在,人力资源在集团类公司中存在着 明显的优势(鸿海集团),有一次笔者亲自去体验过红海集团的招聘,只 知道人力资源是管理企业招聘的 当时我被招聘上了,当时给我们培训 的人

- Linux自启动设置详解

bijian1013

linux

linux有自己一套完整的启动体系,抓住了linux启动的脉络,linux的启动过程将不再神秘。

阅读之前建议先看一下附图。

本文中假设inittab中设置的init tree为:

/etc/rc.d/rc0.d

/etc/rc.d/rc1.d

/etc/rc.d/rc2.d

/etc/rc.d/rc3.d

/etc/rc.d/rc4.d

/etc/rc.d/rc5.d

/etc

- Spring Aop Schema实现

bijian1013

javaspringAOP

本例使用的是Spring2.5

1.Aop配置文件spring-aop.xml

<?xml version="1.0" encoding="UTF-8"?>

<beans

xmlns="http://www.springframework.org/schema/beans"

xmln

- 【Gson七】Gson预定义类型适配器

bit1129

gson

Gson提供了丰富的预定义类型适配器,在对象和JSON串之间进行序列化和反序列化时,指定对象和字符串之间的转换方式,

DateTypeAdapter

public final class DateTypeAdapter extends TypeAdapter<Date> {

public static final TypeAdapterFacto

- 【Spark八十八】Spark Streaming累加器操作(updateStateByKey)

bit1129

update

在实时计算的实际应用中,有时除了需要关心一个时间间隔内的数据,有时还可能会对整个实时计算的所有时间间隔内产生的相关数据进行统计。

比如: 对Nginx的access.log实时监控请求404时,有时除了需要统计某个时间间隔内出现的次数,有时还需要统计一整天出现了多少次404,也就是说404监控横跨多个时间间隔。

Spark Streaming的解决方案是累加器,工作原理是,定义

- linux系统下通过shell脚本快速找到哪个进程在写文件

ronin47

一个文件正在被进程写 我想查看这个进程 文件一直在增大 找不到谁在写 使用lsof也没找到

这个问题挺有普遍性的,解决方法应该很多,这里我给大家提个比较直观的方法。

linux下每个文件都会在某个块设备上存放,当然也都有相应的inode, 那么透过vfs.write我们就可以知道谁在不停的写入特定的设备上的inode。

幸运的是systemtap的安装包里带了inodewatch.stp,位

- java-两种方法求第一个最长的可重复子串

bylijinnan

java算法

import java.util.Arrays;

import java.util.Collections;

import java.util.List;

public class MaxPrefix {

public static void main(String[] args) {

String str="abbdabcdabcx";

- Netty源码学习-ServerBootstrap启动及事件处理过程

bylijinnan

javanetty

Netty是采用了Reactor模式的多线程版本,建议先看下面这篇文章了解一下Reactor模式:

http://bylijinnan.iteye.com/blog/1992325

Netty的启动及事件处理的流程,基本上是按照上面这篇文章来走的

文章里面提到的操作,每一步都能在Netty里面找到对应的代码

其中Reactor里面的Acceptor就对应Netty的ServerBo

- servelt filter listener 的生命周期

cngolon

filterlistenerservelt生命周期

1. servlet 当第一次请求一个servlet资源时,servlet容器创建这个servlet实例,并调用他的 init(ServletConfig config)做一些初始化的工作,然后调用它的service方法处理请求。当第二次请求这个servlet资源时,servlet容器就不在创建实例,而是直接调用它的service方法处理请求,也就是说

- jmpopups获取input元素值

ctrain

JavaScript

jmpopups 获取弹出层form表单

首先,我有一个div,里面包含了一个表单,默认是隐藏的,使用jmpopups时,会弹出这个隐藏的div,其实jmpopups是将我们的代码生成一份拷贝。

当我直接获取这个form表单中的文本框时,使用方法:$('#form input[name=test1]').val();这样是获取不到的。

我们必须到jmpopups生成的代码中去查找这个值,$(

- vi查找替换命令详解

daizj

linux正则表达式替换查找vim

一、查找

查找命令

/pattern<Enter> :向下查找pattern匹配字符串

?pattern<Enter>:向上查找pattern匹配字符串

使用了查找命令之后,使用如下两个键快速查找:

n:按照同一方向继续查找

N:按照反方向查找

字符串匹配

pattern是需要匹配的字符串,例如:

1: /abc<En

- 对网站中的js,css文件进行打包

dcj3sjt126com

PHP打包

一,为什么要用smarty进行打包

apache中也有给js,css这样的静态文件进行打包压缩的模块,但是本文所说的不是以这种方式进行的打包,而是和smarty结合的方式来把网站中的js,css文件进行打包。

为什么要进行打包呢,主要目的是为了合理的管理自己的代码 。现在有好多网站,你查看一下网站的源码的话,你会发现网站的头部有大量的JS文件和CSS文件,网站的尾部也有可能有大量的J

- php Yii: 出现undefined offset 或者 undefined index解决方案

dcj3sjt126com

undefined

在开发Yii 时,在程序中定义了如下方式:

if($this->menuoption[2] === 'test'),那么在运行程序时会报:undefined offset:2,这样的错误主要是由于php.ini 里的错误等级太高了,在windows下错误等级

- linux 文件格式(1) sed工具

eksliang

linuxlinux sed工具sed工具linux sed详解

转载请出自出处:

http://eksliang.iteye.com/blog/2106082

简介

sed 是一种在线编辑器,它一次处理一行内容。处理时,把当前处理的行存储在临时缓冲区中,称为“模式空间”(pattern space),接着用sed命令处理缓冲区中的内容,处理完成后,把缓冲区的内容送往屏幕。接着处理下一行,这样不断重复,直到文件末尾

- Android应用程序获取系统权限

gqdy365

android

引用

如何使Android应用程序获取系统权限

第一个方法简单点,不过需要在Android系统源码的环境下用make来编译:

1. 在应用程序的AndroidManifest.xml中的manifest节点

- HoverTree开发日志之验证码

hvt

.netC#asp.nethovertreewebform

HoverTree是一个ASP.NET的开源CMS,目前包含文章系统,图库和留言板功能。代码完全开放,文章内容页生成了静态的HTM页面,留言板提供留言审核功能,文章可以发布HTML源代码,图片上传同时生成高品质缩略图。推出之后得到许多网友的支持,再此表示感谢!留言板不断收到许多有益留言,但同时也有不少广告,因此决定在提交留言页面增加验证码功能。ASP.NET验证码在网上找,如果不是很多,就是特别多

- JSON API:用 JSON 构建 API 的标准指南中文版

justjavac

json

译文地址:https://github.com/justjavac/json-api-zh_CN

如果你和你的团队曾经争论过使用什么方式构建合理 JSON 响应格式, 那么 JSON API 就是你的 anti-bikeshedding 武器。

通过遵循共同的约定,可以提高开发效率,利用更普遍的工具,可以是你更加专注于开发重点:你的程序。

基于 JSON API 的客户端还能够充分利用缓存,

- 数据结构随记_2

lx.asymmetric

数据结构笔记

第三章 栈与队列

一.简答题

1. 在一个循环队列中,队首指针指向队首元素的 前一个 位置。

2.在具有n个单元的循环队列中,队满时共有 n-1 个元素。

3. 向栈中压入元素的操作是先 移动栈顶指针&n

- Linux下的监控工具dstat

网络接口

linux

1) 工具说明dstat是一个用来替换 vmstat,iostat netstat,nfsstat和ifstat这些命令的工具, 是一个全能系统信息统计工具. 与sysstat相比, dstat拥有一个彩色的界面, 在手动观察性能状况时, 数据比较显眼容易观察; 而且dstat支持即时刷新, 譬如输入dstat 3, 即每三秒收集一次, 但最新的数据都会每秒刷新显示. 和sysstat相同的是,

- C 语言初级入门--二维数组和指针

1140566087

二维数组c/c++指针

/*

二维数组的定义和二维数组元素的引用

二维数组的定义:

当数组中的每个元素带有两个下标时,称这样的数组为二维数组;

(逻辑上把数组看成一个具有行和列的表格或一个矩阵);

语法:

类型名 数组名[常量表达式1][常量表达式2]

二维数组的引用:

引用二维数组元素时必须带有两个下标,引用形式如下:

例如:

int a[3][4]; 引用:

- 10点睛Spring4.1-Application Event

wiselyman

application

10.1 Application Event

Spring使用Application Event给bean之间的消息通讯提供了手段

应按照如下部分实现bean之间的消息通讯

继承ApplicationEvent类实现自己的事件

实现继承ApplicationListener接口实现监听事件

使用ApplicationContext发布消息