第四节 16位全加器的设计

第四节 16位全加器的设计

这节课将要学习一个重要的设计方法,即top to down,从顶层到底层的设计方法。我们将要学习到实例化这个重要方法。一个复杂的系统,总是由许多简单的单元组成的。一个机构也是由许多的科室组成,简单的工作才能组成复杂的网络。

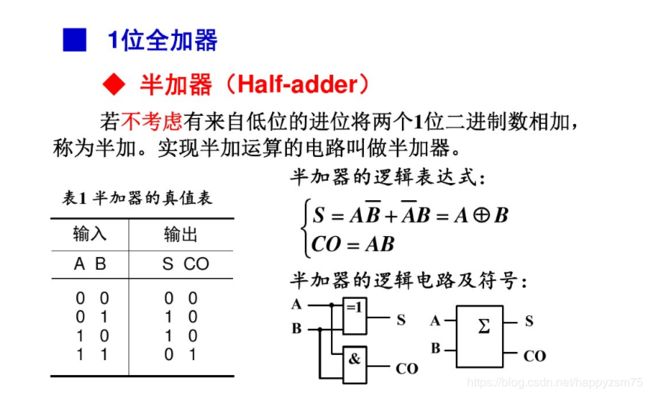

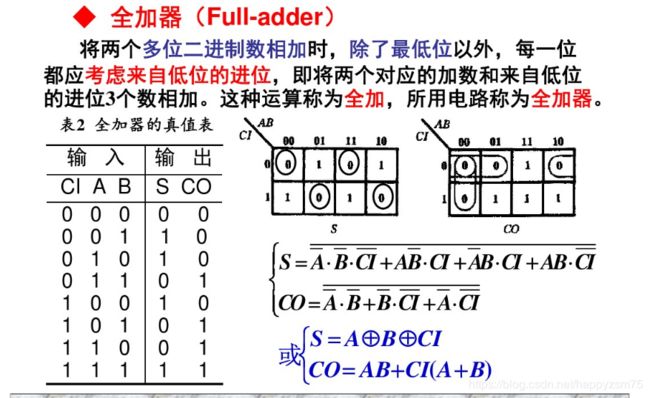

先来复习一下加法器的知识吧。

A、B是输入,CO是进位,Sum是和。对于半加器来说,Sum是A、B的异或运算。

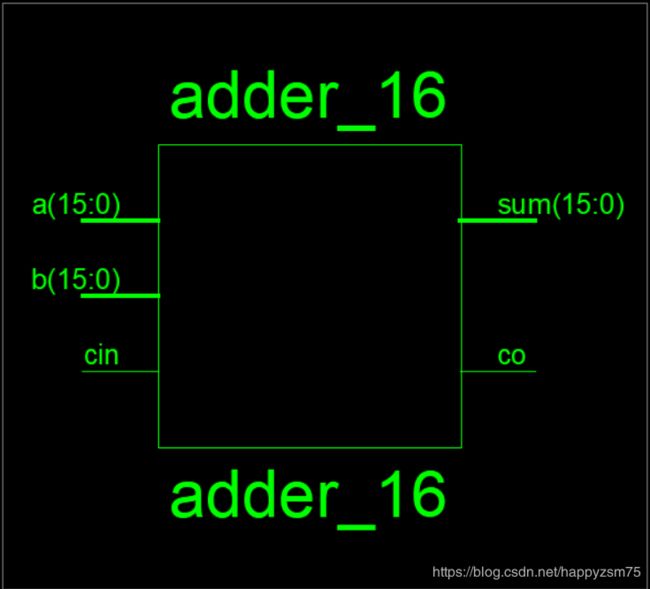

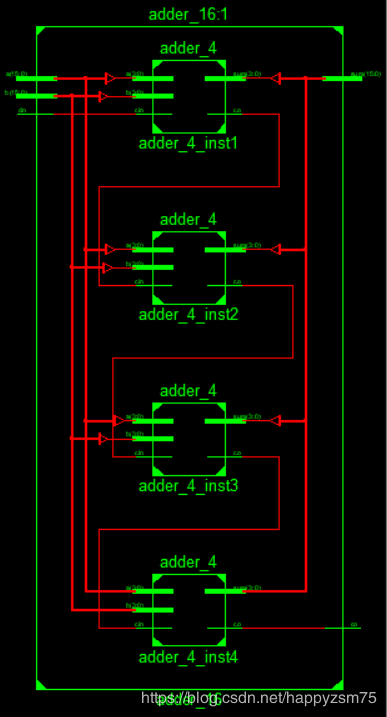

先写顶层模块adder_16;

再写一个四位加法器模块;

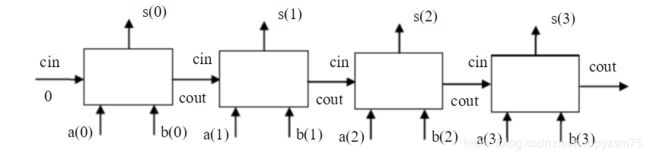

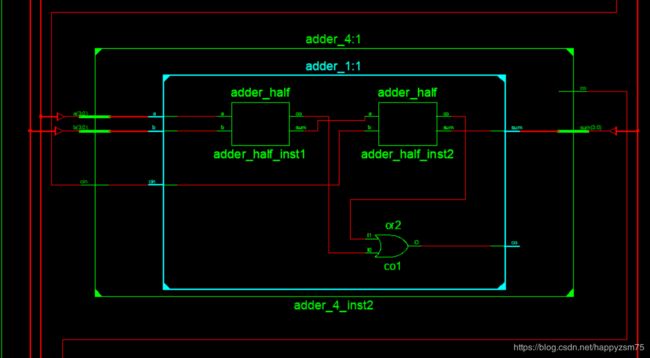

四位全加器可对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项(Ci),以得到输出为和(S)和进位(C0)。其中CIN表示输入进位位,COUT表示输出进位位,输入A和B分别表示加数和被加数。输出SUM=A+B+CIN,当SUM大于255时,COUT置‘1’。下图为四位加法器原理图。

/16路全加器

module adder_16(

input wire [15:0]a,

input wire [15:0]b,

input wire cin,

output wire [15:0]sum,

output wire co

);

wire c0;

adder_4 adder_4_inst1(

.a (a[3:0]),

.b (b[3:0]),

.cin (cin),

.sum (sum[3:0]),

.co (c0)

);

wire c1;

adder_4 adder_4_inst2(

.a (a[7:4]),

.b (b[7:4]),

.cin (c0),

.sum (sum[7:4]),

.co (c1)

);

wire c2;

adder_4 adder_4_inst3(

.a (a[11:8]),

.b (b[11:8]),

.cin (c1),

.sum (sum[11:8]),

.co (c2)

);

adder_4 adder_4_inst4(

.a (a[15:12]),

.b (b[15:12]),

.cin (c2),

.sum (sum[15:12]),

.co (co)

);

endmodule

在新建一个模块adder_1;1位的全加器真值表在最上面。仍然很麻烦,所以考虑用半加器。先例化到adder_4中。

module adder_4(

input wire [3:0]a,

input wire [3:0]b,

input wire cin,

output wire [3:0]sum,

output wire co

);

wire c0;

adder_1 adder_1_inst1(

.a (a[0]),

.b (b[0]),

.cin (cin),

.sum (sum[0]),

.co (c0)

);

wire c1;

adder_1 adder_1_inst2(

.a (a[1]),

.b (b[1]),

.cin (c0),

.sum (sum[1]),

.co (c1)

);

wire c2;

adder_1 adder_1_inst3(

.a (a[2]),

.b (b[2]),

.cin (c1),

.sum (sum[2]),

.co (c2)

);

adder_1 adder_1_inst4(

.a (a[3]),

.b (b[3]),

.cin (c2),

.sum (sum[3]),

.co (co)

);

endmodule

再新建一个模块adder_half;例化到adder_1

module adder_1(

input wire a,

input wire b,

input wire cin,

output wire sum,

output wire co

);

wire s0,c0;

adder_half adder_half_inst1(

.a (a),

.b (b),

.sum (s0),

.co (c0)

);

wire c1;

adder_half adder_half_inst2(

.a (s0),

.b (cin),

.sum (sum),

.co (c1)

);

assign co=c0|c1;

endmodule

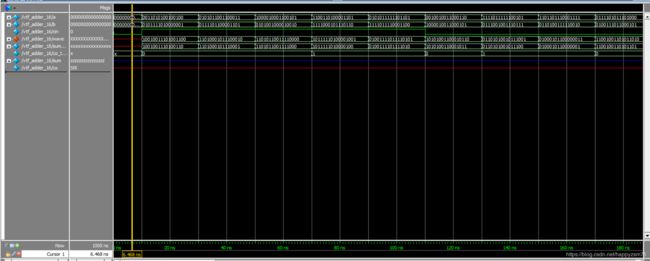

这样一个16位全加器就设计完啦,接下来看下仿真。

仿真代码如下:

initial begin

// Initialize Inputs

a = 0;

b = 0;

cin = 0;

// Wait 100 ns for global reset to finish

#10;

repeat(20) begin

a={$random}%17'h10000;

b={$random}%17'h10000;

cin={$random}%2;

{co_test,sum_test}=a+b+cin;

#20;

end

// Add stimulus here

end学会实例化、时序写法、状态机后就需要自己不断的大量练习写代码才行。