姓名:高新诚 学号:17021223282

来源:雷锋网

【嵌牛导读】:谈起半导体技术的发展,总是回避不了“摩尔定律”这四个字——当价格不变时,集成电路上可容纳的元器件的数目,约每隔18~24个月便会增加一倍,性能也将提升一倍。芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。

【嵌牛鼻子】:摩尔定律 半导体

【嵌牛正文】:

所谓的XXnm指的是集成电路的MOSFET晶体管栅极的宽度,也被称为栅长。栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管。

目前,业内最重要的代工企业台积电、三星和GF(格罗方德),在半导体工艺的发展上越来越迅猛,10nm制程才刚刚应用一年半,7nm制程便已经好似近在眼前。

在业界盛行的摩尔定律将死的论调下,如此猛烈的突击7nm制程需要克服怎样的困难?几方大佬又是如何布局这一关键节点?

半导体工艺的Tick-Tock

Tick-Tock,是Intel的芯片技术发展的战略模式,在半导体工艺和核心架构这两条道路上交替提升。半导体工艺领域也有类似的形式存在,在14nm/16nm节点之前,半导体工艺在相当长的历史时期里有着“整代”和“半代”的差别。

在戈登·摩尔提出著名的摩尔定律后,半导体产业一直坚持以18个月为周期升级半导体工艺。直观结果是,制程演进一直在以大约0.7的倍数逐级缩减,如1000nm->700nm->500nm->350nm->250nm等。

而在制程迈过180nm节点后,台积电等代工厂提出了一种相比Intel的制程缩减0.9倍的工艺。这种工艺可以在不对产线进行大改的同时,提供1.24倍电路密度的芯片。Intel对此等技术非常不感冒,还为其挂上了半代工艺的名号。

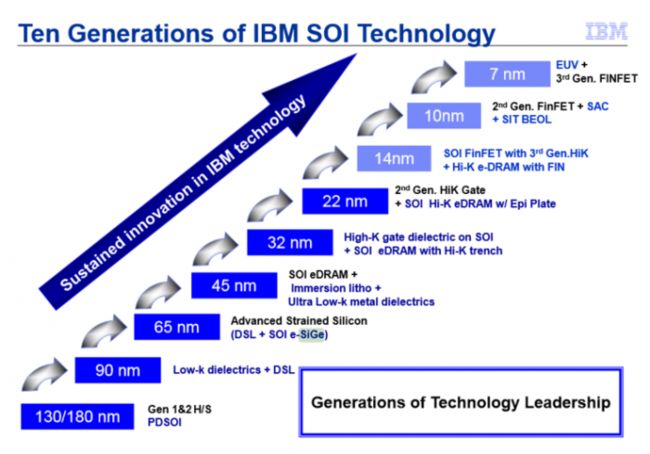

自此,Intel和IBM制造技术联盟(包括三星和GF等)依然严格按着180nm->130nm->90nm->65nm->45nm->32nm->22nm的步调前行(三星和GF在32nm后转向28nm),而台积电等半导体晶圆代工厂则走上了150nm->110nm->80nm->55nm->40nm->28nm->20nm的路线。

不过当半导体工艺继续向前演进时,由于随着晶体管尺寸逐渐缩小至接近物理极限,在各种物理定律的束缚下,半导体工厂如同戴着镣铐跳舞,因此在几家厂商纷纷出现“异常状况”:本应属于整代工艺的16nm制程被台积电所用,Intel的14nm制程字面上却应该属于半代工艺的范畴。再接下来,几家则不约而同的选择了10nm->7nm->5nm的路线,整代和半代的区别自此成为历史。

也正是因为这个原因,半导体厂商们进军7nm制程的道路并不顺利,还需要掀翻“光刻”、“晶体管架构”和“沟道材料”三座大山。

工欲善其事,先搞光刻机

作为半导体工艺中最具代表性的,光刻技术可称为现代集成电路上最大的难题,没有之一。

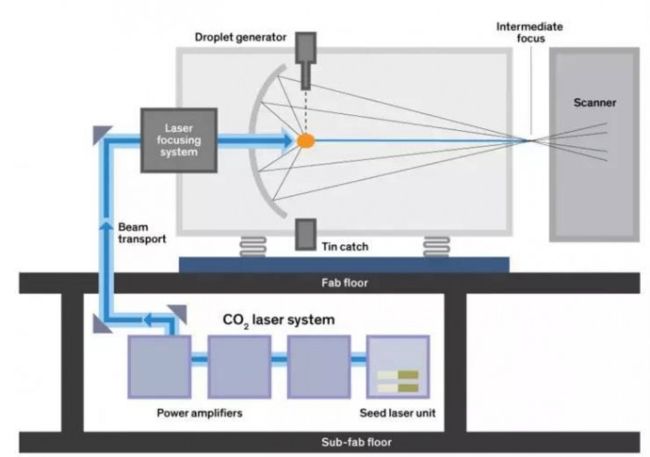

所谓光刻其实很好理解,就是让光通过掩膜投射到涂抹了光刻胶的硅片上,将电路构造印在上面,类似于“投影描图”,只是描图的不是人手,而是机器,照射图样的也不再是可见光,而是紫外线。

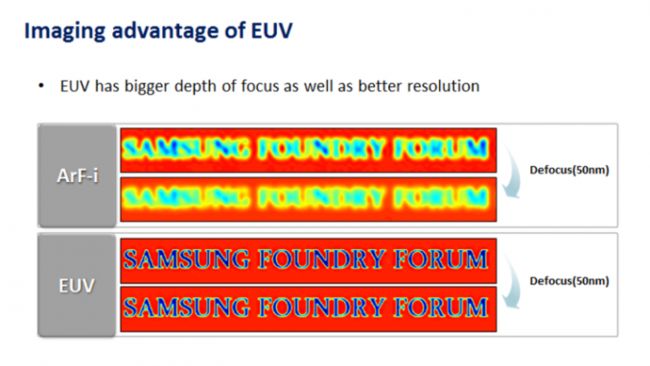

目前半导体生产中使用的是波长193nm的深紫外(DUV)光刻。实际上,在制程发展到130nm之前,人们就曾指出193nm深紫外光会发生严重的衍射现象而无法继续使用,需要换用波长为13.5nm的极紫外(EUV)光刻才能继续缩小半导体工艺。

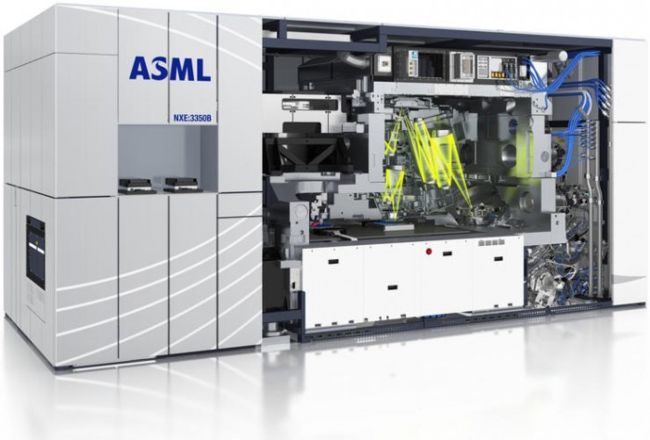

EUV的研发始于20世纪90年代,最早希望在90nm制程节点投入应用,然而EUV光刻机一直达不到正式生产的要求。无奈之下,人们只能通过沉浸式光刻、多重曝光等手段,将DUV一路推进到了10nm阶段。

目前ASML的EUV光刻机使用40对蔡司镜面构成光路,每个镜面的反光率为70%。这也就是说,EUV光束通过该系统中的每一对镜面时都会减半,在经过40对镜面反射后,只有不到2%的光线能投射到晶元上。

到达晶圆的光线越少,光刻所需的曝光时间就越长,相应的生产成本也就越高。为了抵消镜面反射过程中的光能损耗,EUV光源发出的光束必须足够强,这样才能与现在非常成熟的DUV光刻技术比拼时间成本。

但是多年以来,光照亮度的提升始终未能达到人们的预期,ASML的EUV产品市场负责人Hans Meiling曾表示,人们严重低估了EUV的难度。正在实验中的EUV光源焦点功率刚刚达到250瓦,可以支撑机器每小时处理125个晶片,效率仅有现今DUV的一半。

如果再加上价格和能耗,EUV取代DUV还会更加艰难。最新的EUV光刻机价格超过1亿欧元,是DUV光刻机价格的二倍有余,且使用EUV光刻机进行批量生产时会消耗1.5兆瓦的电力,远超现有的DUV光刻机。

ASML方面表示,EUV光刻设备尚未彻底准备完成,最快也要到2019年才能应用于正式生产,因此几大半导体代工厂均在DUV+多重曝光技术上继续深挖,以求撑过EUV光刻机的真空期。

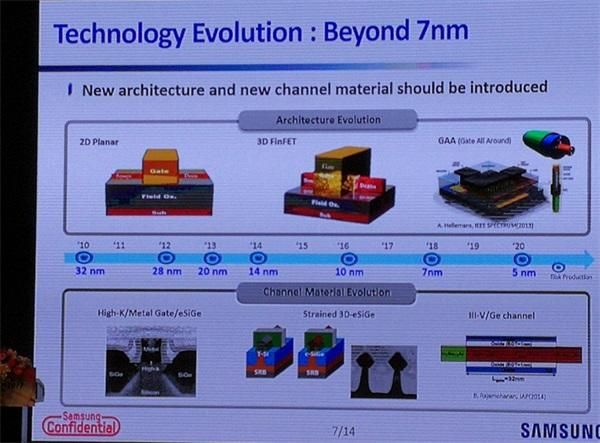

全新晶体管架构和沟道材料

通过DUV+多重曝光或EUV光刻缩小栅极宽度,进而刻画出更小的晶体管,只是实现7nm的关键要素之一。随着半导体工艺的发展,半导体沟道上的“门”会在尺寸进入亚原子级后变得极不稳定,这需要换用全新晶体管架构和沟道材料来解决。

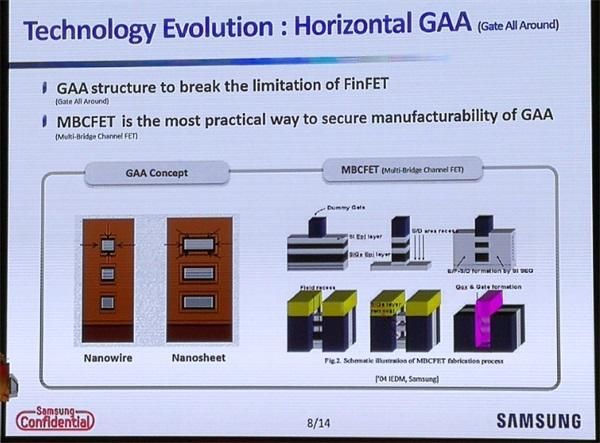

根据三星在CSTIC大会的报告,GAAFET(Gate All Around)是7nm制程节点上最好的选择。GAAFET是一个周边环绕着gate的FinFET,和目前垂直使用fin的FinFET不同,GAAFET的fin设计在旁边,能够提供比普通FinFET更好的电路特性。

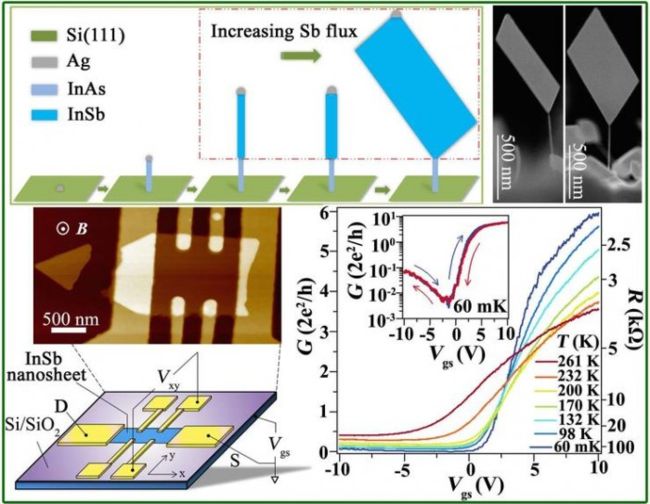

此外在进入7nm工艺时,半导体中连接PN结的沟道材料也必须要作改变。由于硅的电子迁移率为1500c㎡/Vs,而锗可达3900c㎡/Vs,同时硅器件的运行电压是0.75~0.8V,而锗器件仅为0.5V,因而锗在某一时期曾被认为是MOSFET晶体管的首选材料,IBM实验室的第一块7nm芯片使用的就是Ge-Si材料。

IMEC(微电子研究中心)对新的掺锗材料进行了研究,筛选出两种可用于7nm的沟道材料:一种是由80%锗组成的PFET,另一种是25%到50%混合锗的FET或0到25%混合锗的NFET。

但是近来,III-V族材料开始受到厂商的更多关注。III-V族化合物半导体拥有更大的能隙和更高的电子迁移率,可以让芯片承受更高的温度并运行在更高的频率上。且现有硅半导体工艺中的很多技术都可以应用到III-V族材料半导体上,因此III-V族材料也被视为取代硅的理想材料。

7nm群英会

了解了3大技术难题后,我们来看看几大半导体代工厂分别如何部署7nm制程节点。

三星

作为芯片代工行业的后来者,三星是“全球IBM制造技术联盟”中激进派的代表,早早就宣布了7nm时代将采用EUV。今年4月,三星刚刚宣布已经完成了7nm新工艺的研发,并成功试产了7nm EUV晶元,比原进度提早了半年。

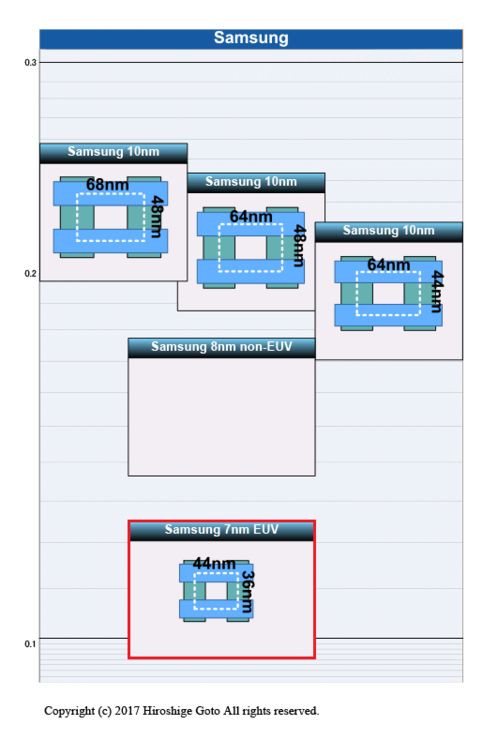

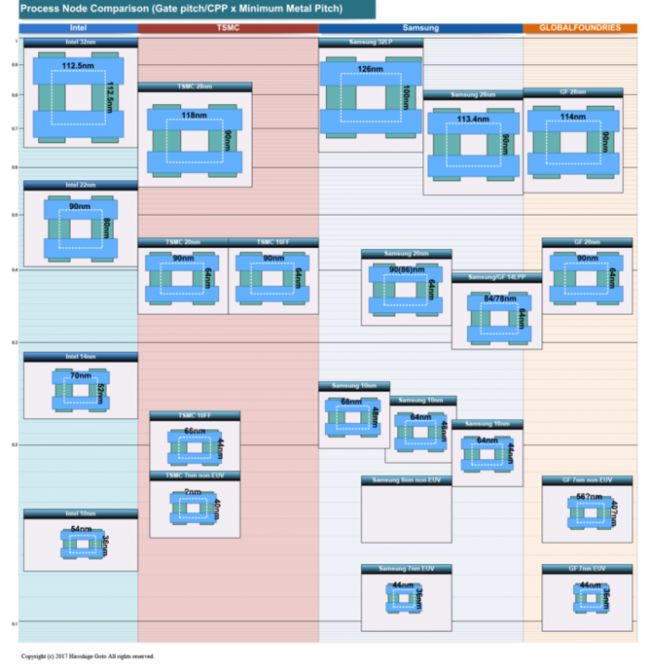

据日本PC WATCH网站上後藤弘茂的分析,三星7nm EUV的特征尺寸为44nm*36nm(Gate Pitch*Metal Pitch),仅为10nm DUV工艺的一半左右。

除了一步到位的7nm EUV外,三星还规划了一种8nm制程。这个制程实际上是使用DUV光刻+多重曝光生产的7nm制程,继承所有10nm工艺上的技术和特性。

由于DUV光刻的分辨率较差,因而芯片的电气性能不如使用7nm EUV,所以三星为其商业命名为8nm。从这一点来看,8nm相比现有的10nm,很可能在晶体管密度、性能、功耗等方面做出了终极的优化,基本上可看做深紫外光刻下的技术极限了。

此外,三星在7nm EUV之后,还规划了使用第二代EUV光刻技术的6nm制程,它和8nm同样是商业命名,属于7nm EUV制程的加强版,电气性能会更好。

根据三星的路线,三星将于今年下半年试产7nm EUV晶元,大规模投产时间为2019年秋季。8nm制程大约在2019年第一季度登场,而6nm制程应该会在2020年后出现。

台积电

相比三星直接引入EUV光刻的激进,台积电在7nm上选择了求稳路线,并没有急于进入极紫外光刻时代。台积电表示将继续使用DUV光刻,利用沉浸式光刻和多重曝光等技术平滑进入7nm时代,然后再转换到EUV光刻。

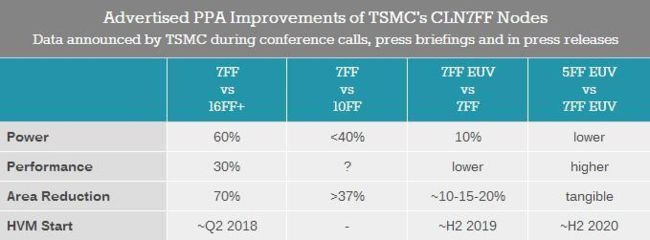

台积电使用DUV光刻的第一代7nm FinFET已经在2017年第二季度进入试产阶段。与目前的10nm FinFET制程相比,7nm FinFET将可在晶体管数量的情况下使芯片尺寸37%,或在电路复杂度相同的情况下降低40%的功耗。

在接下来的第二代7nm FinFET+制程上,台积电将开始使用EUV光刻。针对EUV优化的布线密度可带来约10~20%的面积减少,或在电路复杂度相同的情况下,相比7nm FinFET再降低10%的功耗。

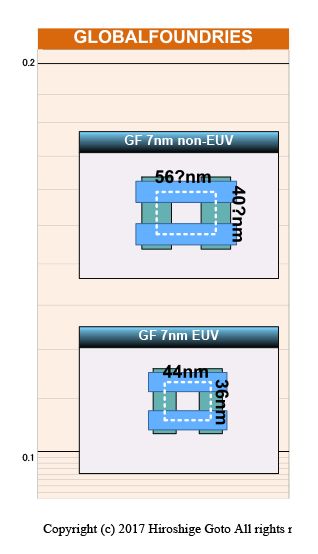

而根据後藤弘茂的分析,台积电7nm DUV的特征尺寸介于台积电10nm FinFET和三星7nm EUV之间,Metal Pitch特征尺寸40nm,Gate Pitch特征尺寸尚不明确,但必定小于10nm时的66nm。

此外,与完全使用DUV工具制造的芯片相比,使用EUV光刻生产芯片的周期也将缩短,台积电计划在2018年第二季度开始试产7nm FinFET+晶元。

GF

GF此前曾是AMD自家的半导体工厂,后由于AMD资金问题而拆分独立。GF同样属于IBM“全球IBM制造技术联盟”的一员,其半导体工艺和三星同宗同源。然而GF在28nm、14nm两个节点上都遇到了重大技术难题,不得不向“后来者”三星购买生产技术。

介于此,GF在14nm之后决定放弃10nm节点,直接向7nm制程进军。虽然这个决策稍显激进,但GF也明白步子大了容易扯到啥的道理,决定在光刻技术上稳中求进,使用现有的DUV光刻技术实现第一代7nm工艺的制造,随后再使用EUV光刻进行两次升级迭代。

去年7月曾报道过GF名为7LP的7nm DUV制程细节,据其在阿尔伯尼纽约州立大学理工学院负责评估多重光刻技术的George Gomba以及其他IBM的同事透露,GF将在第一代7nm DUV产品上,使用四重光刻法。

相比之前的14nm LPP制程,7LP制程在功率和晶体管数量相同的前提下,可以带来40%的效率提升,或者在频率和复杂性相同的情况下,将功耗降低60%。但受限于四重光刻这一复杂流程,GF表示根据不同应用场景,7LP只能将芯片功耗降低30~45%。

从後藤弘茂分析中可以看到,GF的7nm DUV特征尺寸为56nm*40nm(Gate Pitch*Metal Pitch),应当与台积电7nm DUV的基本相当。而7nm EUV的特征尺寸为44nm*36nm,与三星7nm EUV完全一致(毕竟同源)。

不过在EUV的部署上,GF尚存在一些阻碍。目前ASML提供的保护膜仅适用于每小时85个晶片的生产率(WpH),而GF今年的计划是达到125WpH,这意味着现有的保护膜无法应对量产所需的强大光源。

目前,GF尚未透露将于何时开始使用EUV光刻,只说要等到“准备就绪”以后,不过看起来难以在2018年以前准备就绪。因此业界普遍猜测GF最早也要到2019年才能使用EUV光刻生产芯片。

Intel:我不是针对谁……

Intel作为全球最大的半导体企业,在半导体工艺方面一直保持着领先地位,并且引领了大量全新技术的发展。不过近几年,Intel半导体工艺的发展速度似乎逐渐慢了下来,比如14nm工艺竟然用了三代,10nm工艺也被竞争对手抢先。

实际上,三星和台积电在进入16/14nm节点后,在制程上常使用一些商业命名,比如上面提到的三星7nm制程,优化一下就变成了6nm。而Intel的14nm制程虽然历经两次优化,却只是以14nm、14nm+和14nm++来命名,二者已经不存在直接的可比性。

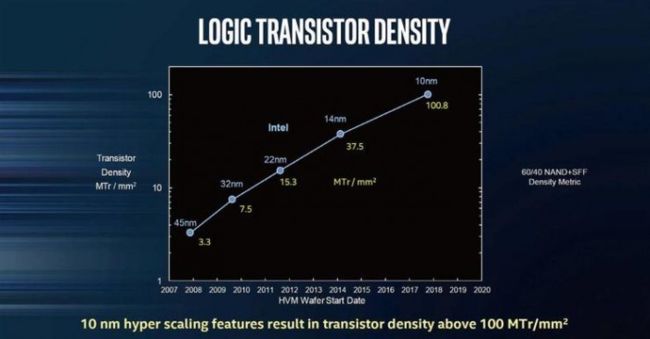

由于晶体管制造的复杂性,每代晶体管工艺中有面向不同用途的制造技术版本,不同厂商的代次之间统计算法也完全不同,单纯用代次来对比是不准确的。目前业内常用晶体管密度来衡量制程水平,实际上,Intel最新10nm制程的晶体管密度甚至反而要比三星、台积电的7nm制程更高。

根据Intel公布的晶体管密度表格,其45nm制程的晶体管密度约为3.3MTr/mm²(百万晶体管每平方毫米),32nm为7.5MTr/mm²,22nm为15.3MTr/mm²,上升倍数大约为2.1倍。但是14nm时晶体管密度大幅提升了2.5倍,为37.5MTr/mm²,10nm更是比14nm提升了2.7倍之多,达到100.8MTr/mm²。

而根据後藤弘茂的分析,如果将Intel、台积电、三星和GF近些年制程的特征尺寸放在一起对比,也可以看出Intel的14nm制程确实要优于三星和GF的14nm LPP以及台积电的16nm FinFET,仅略输于三星早期的10nm制程。

Intel的10nm制程则更是全面胜过台积电和三星的10nm制程,甚至比台积电和GF的第一批7nm DUV都要更好。虽然不如三星和GF的第二批7nm EUV制程,但Intel肯定也会深挖10nm制程,第二代10nm赶超三星和GF的7nm EUV也不是不可能。

国外网站Semiwiki日前也讨论到了三星的10nm、8nm以及7nm制程的情况,其中10nm制程的晶体管密度是55.5MTr/mm²,8mm是64.4MTr/mm²,7nm也不过101.23MTr/mm²,堪堪超过Intel 10nm制程一点点。

下一站,5nm

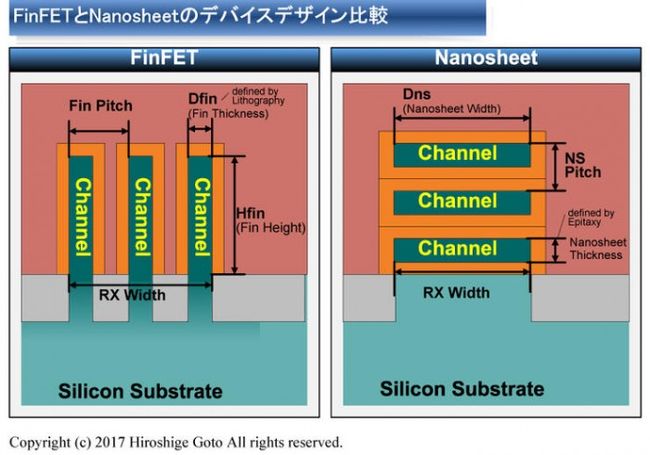

从眼下7nm制程的种种困难可以看出,在5nm及以后的节点上,晶体管的结构很有可能仍然需要进行改进,目前比较受关注的是一种类似罗汉塔式的Nanosheet晶体管。

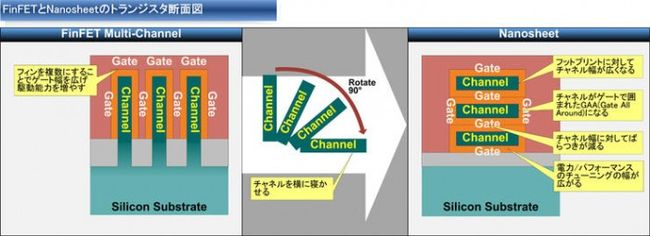

Nanosheet是“IBM联盟”在2017年6月的Symposia on VLSI Technology and Circuits半导体会议上提出的,其晶体管为“将FinFET 90度放倒”的扁平堆栈化结构。

在查看了後藤弘茂的分析后粗略得知,IBM联盟展示了沿着从源级(source)到漏级(drain)方向90度切开的晶体管横截面,可以看到FinFET工艺上Channel是直立的,就如同鳍片的造型,将这些鳍片90度放到后,就变成了Nanowire的形状。

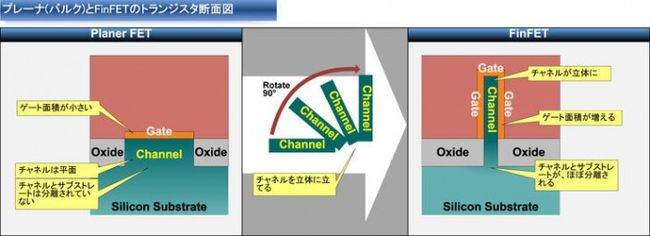

有趣的是,本来FinFET就是将原来的Planer型晶体管90度“放倒”而成。Planer型晶体管是在平面内生成,在其上面紧接着生成栅极(gate)。

而FinFET将平面的Channel给90度立了起来,这样变成三个方向都有栅极的三重门(Tri-gate)电路。Channel基本上脱离了硅基板,不仅抑制了电子迁移,而且增加了栅极的长度。

而与FinFET的三面栅极不同,Nanosheet是4面360度全包,可以进一步抑制电子迁移,提高栅极长度,加强电子驱动能力。如果都是三鳍片结构,Nanosheet栅极长度是FinFET的1.3倍。

Nanosheet在良品率方面也比FinFET更有优势。垂直Channel的FinFET更依靠曝光技术,而水平Channel的Nanosheet更依靠薄膜生成技术。根据实验室的说法,垂直加工比水平加工在半导体制程上更加困难。

但是正如7nm有三座大山一样,5nm制程要解决的也不只有晶体管架构,还有全新布线层材料等难点的存在。根据几家半导体厂商的roadmap,5nm制程被暂定在2020年上马,至少Nanosheet是以此为目标的。

硅半导体的夕阳红

如同过去一样,摩尔定律的命运不仅取决于芯片工艺的尺寸,也取决于物理学家和工程师,对生产出的晶体管和电路可以改善到何种程度。三星、台积电和GF的技术进步,让我们看到了7nm制程时代的发展方向。即便需要克服大量物理与工程难题,集成电路产业也在一步一步向前走。

不过当未来半导体工艺进一步发展到5nm甚至3nm后,电路中最窄的地方甚至只有十几个原子的厚度,届时硅半导体工艺可能真的要面临极限,如今几方竞相角逐7nm制程的情景完全可以说是硅半导体的夕阳红。

在这样的情况下,我们希望这些半导体企业携起手来,在未来的半导体产业上继续努力,继续遵循着摩尔定律的脚步,将人类的计算能力和制造能力推向一个全新的高峰。