最近在复习计算机体系结构,选用的教材是名闻遐迩的《计算机体系结构 量化研究方法 第五版》(Computer Architecture A Quantitative Approach), 关于cache部分,书中着重讲的是如何优化cache,提高cache性能,提出了10种优化策略,但是关于cache与内存(一般称主存)之间的读写过程,cache与主存的地址映射书中讲的比较少,所以本文参考了coursera上 北京大学陆俊林的《 计算机组成》以及上海交通大学邓倩妮老师的《计算机体系结构》的相关ppt及参阅部分网上资料写成,欢迎批评指正。

CPU对存储器的访问,通常是一次读写一个字单元。当CPU访Cache不命中时,需将存储在主存中的字单元连同其后若干个字一同调入Cache中,之所以这样做,是为了使其后的访存能在Cache中命中。因此,主存和Cache之间一次交换的数据单位应该是一个数据块。数据块的大小是固定的,由若干个字组成,且主存和Cache的数据块大小是相同的。

从Cache-主存层次实现的目标看,一方面既要使CPU的访存速度接近于访Cache的速度,另一方面为用户程 序提供的运行空间应保持为主存容量大小的存储空间。在采用Cache-主存层次的系统中,Cache对用户程序而言是透明的,也就是说,用户程序可以不需要知道Cache的存在。因此,CPU每次访存时,依然和未使用Cache的情况一样,给出的是一个主存地址。但在Cache-主存层次中,CPU首先访问的是Cache,并不是主存。为此,需要一种机制将CPU的访主存地址转换成访Cache地址。而主存地址与Cache地址之间的转换是与主存块与 Cache块之间的映射关系紧密联系的,也就是说,当CPU访Cache未命中时,需要将欲访问的字所在主存中的块调入Cache中,按什么样的策略调入,直接影响到主存地址与Cache地址的对应关系,这也就是本小节要解决的主存与Cache的地址映射问题。

主要有三种地址映射方式,分别为全相联映射、直接相联映射和组相联映射。

1. 全相联映射

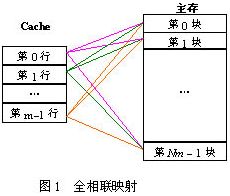

全相联映射是指主存中任一块都可以映射到Cache中任一块的方式,也就是说,当主存中的一块需调入Cache时,可根据当时Cache的块占用或分配情况,选择一个块给主存块存储,所选的Cache块可以是Cache中的任意一块。例如,设Cache共有2C块,主存共有2M块,当主存的某一块j需调进Cache中时,它可以存入Cache的块0、块1、…、块i、… 或块2C -1的任意一块上。如图4-28所示。

图4-28全相联映射方式

在全相联映射方式下,CPU的访主存地址为如下形式:

其中,M为主存的块号,W为块内的字号。而CPU访Cache的地址形式为:

其中,C为Cache的块号,W为块内的字号。

主存地址到Cache地址的转换是通过查找一个由相联存储器实现的块表来完成的,其形成过程如图4-29示。

图4-29全相联映射的地址转换

当 一个主存块调入Cache中时,会同时在一个存储主存块号和Cache块号映射表的相联存储器中进行登记。CPU访存时,首先,根据主存地址中的主存块号 M在相联存储器中查找Cache块号,若找到,则本次访Cache命中,于是将对应的Cache块号取出,并送访Cache地址的块号C字段;紧接着将主 存地址的块内字号W直接送Cache地址的块内字号W字段,从而形成一个访Cache的地址;最后根据该地址完成对Cache单元的访问.

全相联映射方式的优点是Cache的空间利用率高,但缺点是相联存储器庞大,比较电路复杂,因此只适合于小容量的Cache之用。

2. 直接相联映射

直接相联映射方式是指主存的某块j只能映射到满足如下特定关系的Cache块i中:

i=j mod 2C (4.2)

图4-30直接相联映射方式

上图中,主存的第0、2C、2C+1、… 块只能映射到Cache的第0块,主存的第1、2C+1、2C+1+1、… 块只能映射到Cache的第1块,… … ,主存的第2C-1、2C+1-1、…2M-1块只能映射到Cache的第2C-1块。

在直接相联映射方式下,CPU的访主存地址为如下形式:

其中,T为标志号,C为Cache的块号,W为块内的字号。在这里,原主存的块号M实际上被分成了两个字段:T和C,其中C用于指出主存的块可以映射的Cache的块。一般来讲,主存的块数是Cache的块数的整数倍,也就是说主存的块数2M和Cache的块数2C满足关系式:2M=n·2C

在直接相联映射方式下,标志号T是随Cache的每个块一起存储的,其地址转换过程如图4-31所示。

图4-31直接相联映射的地址转换

当一个主存块调入 Cache中时,会同时将主存地址的T标志存入Cache块的标志字段中。当CPU送来一个访存地址时,首先,根据该主存地址的C字段找到Cache的相 应块,然后将该块标志字段中存放的标志与主存地址的T标志进行比较,若相符,说明主存的块目前已调入该Cache块中,则命中,于是使用主存地址的W字段 访问该Cache块的相应字单元;若不相符,则未命中,于是使用主存地址直接访主存。

直接相联映射方式的优点 是比较电路最简单,但缺点是Cache块冲突率较高,从而降低了Cache的利用率。由于主存的每一块只能映射到Cache的一个特定块上,当主存的某块 需调入Cache时,如果对应的Cache特定块已被占用,而Cache中的其它块即使空闲,主存的块也只能通过替换的方式调入特定块的位置,不能放置到 其它块的位置上。

3. 组相联映射

以上两种方式各有优缺 点,而且非常有趣的是,它们的优缺点正好相反,也就是说,对于全相联映射方式来说为优点的恰是直接相联映射方式的缺点,而对于全相联映射方式来说为缺点的 恰是直接相联映射方式的优点。那么,可否找到一种能较好地兼顾这两种方式的优点的映射方式呢?下面我们就来看看组相联映射方式 在这种方式下,将Cache分成2u组,每组包含2v块。主存的块与Cache的组之间采用直接相联映射,而与组内的各块则采用全相联映射。也就是说,主存的某块只能映射到Cache的特定组中的任意一块。主存的某块j与Cache的组k之间满足如下关系:

k=j mod 2u (4.3)

设主存共有2s×2u块(即M=s+u),则它们的映射关系如下图4-32示。

图4-32组相联映射方式

图中,主存的块0、2u、2u+1、…、(2s-1)2u可以映射到Cache的第0组的任意一块,主存的块1、2u+1、2u+1+1、…、(2s-1)2u+1可以映射到Cache的第1组的任意一块,… … ,主存的块2u-1、2u+1-1、…、2M-1可以映射到Cache的第2u-1组的任意一块。

在组相联映射方式下,CPU的访主存地址和访Cache地址分别为如下形式:

其中,u为Cache的组号,v为组内的块号。Cache的块号C=u+v,而主存的块号M=s+u。也就是说,主存块地址的后u位指出了主存的这一块所能映射的Cache的组。

与全相联映射方式类似的是,在组相联映射方式下,主存地址到Cache地址的转换也是通过查找一个由相联存储器实现的块表来完成的,其形成过程如图4-33所示。

图4-33组相联映射的地址转换

当一个主存块调入Cache中时,会同时将其主存块地址的前s位写入一个由相联存储器实现的快表的对应Cache块项的s字段中。例如,设主存的某块调入Cache的第1组的第2块中,则在快表的组1第3项的s字段会登记下该主存块地址的前s位。

CPU访存时,首先,根据主存地址中的主存块号中的u字段找到快表的相应组,然后将该组的所有项的前s位同时与主 存地址的s字段作比较,若相符,则说明主存块在Cache中,于是将Cache中该项的v字段取出,作为Cache地址的v字段,而Cache地址的u、 W字段直接由主存地址的u、W字段形成,最后形成一个完整的访Cache地址。当然,若比较结果是没有相符项,则未命中,由主存地址直接访主存。

其实,全相联映射和直接相联映射可以看成是组相联映射的两个极端情况。若u=0,v=C,则Cache只包含1组,此即全相联映射方式;若u=C,v=0,则组内的块数等于1,此即直接相联映射。

在实际应用中,相联映射方式每组的块数一般取值较小,典型值为2、4、8、16等,分别称为两路组相联、四路组相 联等。这样一方面使得比较器的规模较小,实现较容易,例如两路组相联采用两路比较,四路组相联采用四路比较等;另一方面,Cache每组增加的可映射块数 可有效减少冲突,提高Cache访问的命中率。

1.高速缓冲存储器的功能、结构与工作原理

高速缓冲存储器是存在于主存与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。 Cache的功能是用来存放那些近期需要运行的指令与数据。目的是提高CPU对存储器的访问速度。为此需要解决2个技术问题:一是主存地址与缓存地址的映象及转换; 二是按一定原则对Cache的内容进行替换。

Cache的结构和工作原理如图2.3.1所示。

主要由三大部分组成:

Cache存储体:存放由主存调入的指令与数据块。

地址转换部件:建立目录表以实现主存地址到缓存地址的转换。

替换部件:在缓存已满时按一定策略进行数据块替换,并修改地址转换部件。

2.地址映象与转换

地址映象是指某一数据在内存中的地址与在缓冲中的地址,两者之间的对应关系。下面介绍三种地址映象的方式。

1.全相联方式

地址映象规则:主存的任意一块可以映象到Cache中的任意一块

(1) 主存与缓存分成相同大小的数据块。

(2) 主存的某一数据块可以装入缓存的任意一块空间中。

全相联方式的对应关系如图2.3.2所示。如果Cache的块数为Cb,主存的块数为Mb,则映象关系共有Cb×Mb种。

图2.3.3示出了目录表的格式及地址变换规则。 目录表存放在相关(联)存储器中,其中包括三部分:数据块在主存的块地址、存入缓存后的块地址、及有效位(也称装入位)。由于是全相联方式,因此,目录表的容量应当与缓存的块数相同。

举例:某机主存容量为1M,Cache的容量为32KB, 每块的大小为16个字(或字节)。 划出主、缓存的地址格式、 目录表格式及其容量。

容量:与缓冲块数量相同即211=2048(或32K/16=2048)。

优点:命中率比较高,Cache存储空间利用率高。

缺点:访问相关存储器时,每次都要与全部内容比较,速度低,成本高,因而应用少。

2.直接相联方式

地址映象规则: 主存储器中一块只能映象到Cache的一个特定的块中。

(1) 主存与缓存分成相同大小的数据块。

(2) 主存容量应是缓存容量的整数倍,将主存空间按缓存的容量分成区,主存中每一区的块数与缓存的总块数相等。

(3) 主存中某区的一块存入缓存时只能存入缓存中块号相同的位置。

图2.3.4示出了直接相联映象规则。 可见,主存中各区内相同块号的数据块都可以分别调入缓存中块号相同的地址中,但同时只能有一个区的块存入缓存。由于主、缓存块号相同,因此,目录登记时,只记录调入块的区号即可。

图2.3.5示出了主、 缓冲地址格式、目录表的格式及地址变换规则。主、缓存块号及块内地址两个字段完全相同。目录表存放在高速小容量存储器中,其中包括二部分:数据块在主存的区号和有效位。目录表的容量与缓存的块数相同。

地址变换过程:用主存地址中的块号B去访问目录存储器, 把读出来的区号与主存地址中的区号E进行比较, 比较结果相等,有效位为1,则Cache命中,可以直接用块号及块内地址组成的缓冲地址到缓存中取数;比较结果不相等,有效位为1, 可以进行替换,如果有效位为0,可以直接调入所需块。

优点:地址映象方式简单,数据访问时,只需检查区号是否相等即可,因而可以得到比较快的访问速度,硬件设备简单。

缺点:替换操作频繁,命中率比较低。

举例:上例中,主存容量为1M, Cache的容量为32KB,每块的大小为16个字(或字节)。划出主、缓存的地址格式、目录表格式及其容量。

容量:与缓冲块数量相同即211=2048(或32K/16=2048)。

3.组相联映象方式

组相联的映象规则:

(1) 主存和Cache按同样大小划分成块。

(2) 主存和Cache按同样大小划分成组。

(3) 主存容量是缓存容量的整数倍,将主存空间按缓冲区的大小分成区,主存中每一区的组数与缓存的组数相同。

(4) 当主存的数据调入缓存时,主存与缓存的组号应相等,也就是各区中的某一块只能存入缓存的同组号的空间内,但组内各块地址之间则可以任意存放, 即从主存的组到Cache的组之间采用直接映象方式;在两个对应的组内部采用全相联映象方式。

图2.3.6示出了组相联的映象关系, 图中缓存共分Cg个组,每组包含有Gb块; 主存是缓存的Me倍,所以共分有Me个区, 每个区有Cg组,每组有Gb块。那么, 主存地址格式中应包含4个字段:区号、区内组

号、组内块号和块内地址。 而缓存中包含3个字段:组号、组内块号、块内地址。主存地址与缓存地址的转换有两部分,组地址是按直接映象方式,按地址进行访问,而块地址是采用全相联方式,按内容访问。组相联的地址转换部件也是采用相关存储器实现,见图2.3.7。

相关存储器中每个单元包含有: 主存地址中的区号E与组内块号B,两者结合在一起,其对应的字段是缓存块地址b。相关存储器的容量,应与缓存的块数相同。当进行数据访问时,先根据组号,在目录表中找到该组所包含的各块的目录,然后将被访数据的主存区号与组内块号,与本组内各块的目录同时进行比较。如果比较相等,而且有效位为“1”则命中。

可将其对应的缓存块地址b送到缓存地址寄存器的块地址字段,与组号及块内地址组装即形成缓存地址。如果比较不相等,说明没命中,所访问的数据块尚没有进入缓存,则进行组内替换;如果有效位为0,则说明缓存的该块尚未利用, 或是原来数据作废,可重新调入新块。

优点:块的冲突概率比较低,块的利用率大幅度提高,块失效率明显降低。

缺点:实现难度和造价要比直接映象方式高。

主存与Cache的地址映射

由于Cache比主存小的多,因此必须使用一种机制将主存地址定位到Cache中,即地址映射。这个映射过程全部由硬件实现,对程序员透明。

1. 地址映射方法:

采用查表法(用专用快速硬件实现表格)

表中内容:映射的Cache地址、标记(命中判断)、有效位

2. 地址映射的三种方式:

(1)全相联映射方式

| · 任一主存块能映射到Cache中任意行(主存块的容量等于Cache行的容量),见图1: · 映射过程:(见图2) ① 存入Cache:块表标记中存放主存的块号 · 符合, 即数据在Cache中,形成访问Cache的地址(地址映射),访问Cache; · 优点:灵活,不易产生冲突; 例:设访问存储器地址的块号序列为22、26、22、26、16、4、16、18,采用全相联映射方式时,Cache行分配情况(见图3)。 |

全相联映射方式实例演示

(2)直接映射方式

直接映射方式实例演示

| · 某一主存块只能能映射到Cache的特定行,见图4: i = j mod m 其中: i:Cache的行号; · 映射过程:(见图5) ① 存入Cache:快表标记中存放主存地址的区号 ② 检索:根据访问主存地址的中间字段(行号),找到Cache快表中的这一行,读取该行中的标记字段与主存地址高位字段(区号)比较(图5阴影区) · 符合:即数据在Cache中,形成访问Cache的地址(地址映射),访问Cache; 颠簸:例:频繁访问主存地址块序列0、m、0、m,则Cache中 第0行信息只能频繁调进调出,即出现颠簸现象。 例:访问存储器地址序列为22、26、22、26、16、4、16、18,采用直接映射方式时,Cache行分配情况(见图6)。 |

(3)组相联映射方式

组相联映射方式实例演示

| 组相联映射方式 是全相联映射方式和直接相联映射方式的结合,结合两者的优点 · 方法:把Cache分为若干组,每组含有若干行。 · 映射过程:(见图8) ① 存入Cache:快表标记中存放主存地址的区号及块号(将块地址分为三部分: · 块(行)地址· 组号· 标记(区号)) ② 检索:根据访问主存地址的第二字段(组号),找到Cache中的相应组,读取该组中的每一行标记字段与主存地址高位字段(区号)及块号比较(图8阴影区) · 优点:结合上面两种的优点。 ① 因为组内行数较少,比较器容易实现; 例1:设Cache有8个行,分成2个组,设访问存储器地址的块号序列为22、26、22、26、16、4、16、18,采用组相联映射方式时,Cache行分配情况(见图9)。 |

参考:

主存与Cache的地址映射

Cache和主存的三种映射方式