FPGA学习历程-AX4010:Warning收录(持续更新)

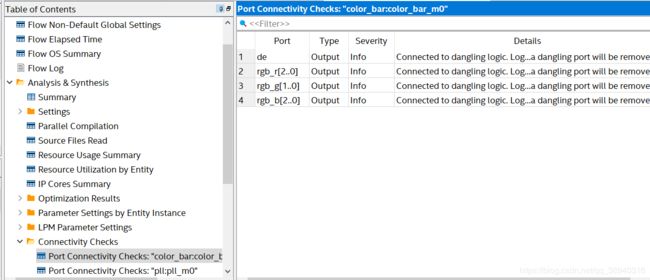

1.Warning (12241): 1 hierarchies have connectivity warnings - see the Connectivity Checks report folder

译:1层次结构有连接警告-见连接检查报告文件夹

解决:这个位置有详细的描述

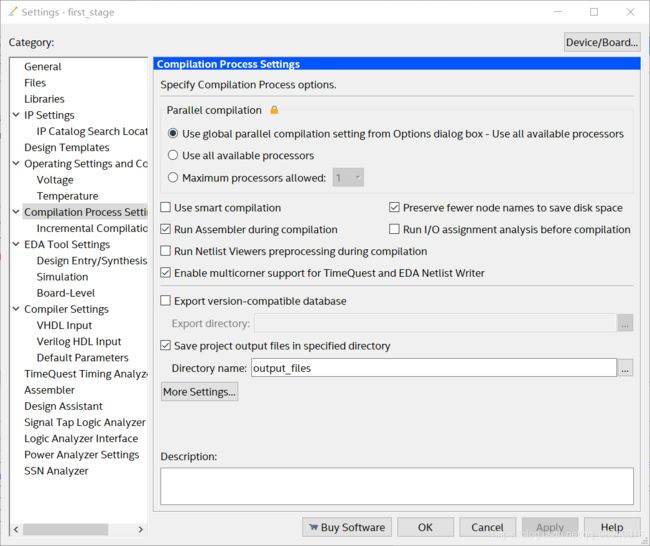

2.Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

译:没有指定处理器的数量,这可能导致共享机器过载。将QSF中的全局分配NUM_PARALLEL_PROCESSORS设置为适当的值以获得最佳性能。

解决:就是个关于影响编译速度的警告,没什么大问题。

Assignments —— Settings —— Compilation Process Settings —— Parallel compilation勾选第二项就可以消除掉。

3.Warning (292013): Feature LogicLock is only available with a valid subscription license. You can purchase a software subscription to gain full access to this feature.

译:功能LogicLock只有在获得有效的订阅许可证时才可用。您可以购买软件订阅以获得对该功能的完全访问权。

4.Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details.

译:一些引脚有不完整的I/O分配。有关详细信息,请参阅I/O作业警告报告。

原因说明:此警告主要是因为分配I/O引脚时,采用了默认的参数,主要是用来提醒懒人的,养成良好的设计习惯,一定要仔细对每一个管脚进行计算后,设置合理的参数,而不是简单用个默认值来搪塞。

解决:打开Pin Planner,选择Current Strength和Slew Rate的参数,将默认值改成非默认值。

5.Critical Warning (332012): Synopsys Design Constraints File file not found: ‘first_stage.sdc’. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.

译:Synopsys设计约束文件文件未找到:‘first_stage.sdc’。TimeQuest定时分析器需要一个Synopsys设计约束文件来获得合适的定时约束。没有它,编译器就不能正确地优化设计。

原因说明:该电路没有时序约束文件。在Quartus II 13.0和之后的版本,软件都默认要求开发者提供时序约束文件,如果没有提供,就会给出 “332012” 警告。再者,如果没有提供,软件会自动按照1GHz的要求来进行编译,时序要求如果达不到了,就会得到“332148”警告。

解决:还没到“332148”的程度,能先凑合着用,且暂时还不会写约束,先晾着,会了再来返工。

6.Warning (169177): 2 pins must meet Intel FPGA requirements for 3.3-, 3.0-, and 2.5-V interfaces. For more information, refer to AN 447: Interfacing Cyclone IV E Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems.

Info (169178): Pin sys_rst_n uses I/O standard 3.3-V LVTTL at N13

Info (169178): Pin sys_clk uses I/O standard 3.3-V LVTTL at E1

译:2个引脚必须满足Intel FPGA 3.3-、3.0-和2.5-V接口的要求。有关更多信息,请参考一个447:3.3/3.0/2.5 v LVTTL/LVCMOS I/O系统接口的Cyclone IV E设备。

原因说明:只是针对Cyclone IV E器件,要求设计者注意器件电平匹配的连接方法,而且还不能消除掉…

7.Warning (15058): PLL “pll:pll_m0|altpll:altpll_component|pll_altpll: auto_generated|pll1” is in normal or source synchronous mode with output clock “compensate_clock” set to clk[0] that is not fully compensated because it feeds an output pin – only PLLs in zero delay buffer mode can fully compensate output pins.

译:PLL“PLL:pll_m0|altpll:altpll_component|pll_altpll:auto_generated|pll1”处于正常或源同步模式,输出时钟“compensation ate_clock”设置为clk[0],因为它提供了一个输出引脚,所以没有完全补偿——只有在零延迟缓冲模式下的PLL才能完全补偿输出引脚。

8.Warning (15064): PLL “pll:pll_m0|altpll:altpll_component|pll_altpll: auto_generated|pll1” output port clk[0] feeds output pin “clk_25m~output” via non-dedicated routing – jitter performance depends on switching rate of other design elements. Use PLL dedicated clock outputs to ensure jitter performance.

译:PLL " PLL:pll_m0|altpll:altpll_component|pll_altpll:auto_generated|pll1"输出端口clk[0]通过非专用路由馈送输出引脚“clk_25m~output”——抖动性能取决于其他设计元素的切换速率。使用锁相环专用时钟输出以确保抖动性能。

原因说明:PLL的输出用在了非专属的PLL_OUT

解决:设计电路板的时候最好将PLL_OUT用在相关的时钟信号上,如果没有使用,则这个警告不理会也可。

9.Critical Warning (35025): Partially connected in-system debug instance “auto_signaltap_0” to 171 of its 299 required data inputs, trigger inputs, acquisition clocks, and dynamic pins. There were 0 illegal, 0 inaccessible, and 128 missing sources or connections.

译:编译器无法完全连接信号Tap逻辑分析仪或其他系统内调试实例,因为某些连接无效或不可用。

解决:Signal Tap II那边的连接问题,酌情自行处理。

10.Critical Warning (332168): The following clock transfers have no clock uncertainty assignment. For more accurate results, apply clock uncertainty assignments or use the derive_clock_uncertainty command.

译:下列时钟传输没有时钟不确定性分配。要获得更精确的结果,请应用时钟不确定性分配或使用derive_clock_uncertainty命令。

解决:说到底还是约束问题,先放着。

PS:新发现-在编译信息栏给出的Warning条目中选中指定的Warning,右键单击后点击help项,会自动弹出该Warning项的产生原因及对应的解决方案(虽然解决方案未必看得懂到底该干嘛)