ARM硬件知识和常见通信协议

ARM处理器

ARM(Advanced RISC Machines)一个32位元精简指令集(RISC)处理器架构,ARM处理器广泛地使用在许多嵌入式系统设计。ARM处理器的特点有指令长度固定,执行效率高,低成本等。

特点

1、体积小、低功耗、低成本、高性能;

2、支持Thumb(16位)/ARM(32位!)双指令集,能很好的兼容8位/16位器件;

3、大量使用寄存器,指令执行速度更快;

4、大多数数据操作都在寄存器中完成;

5、寻址方式灵活简单,执行效率高;

6、指令长度固定。

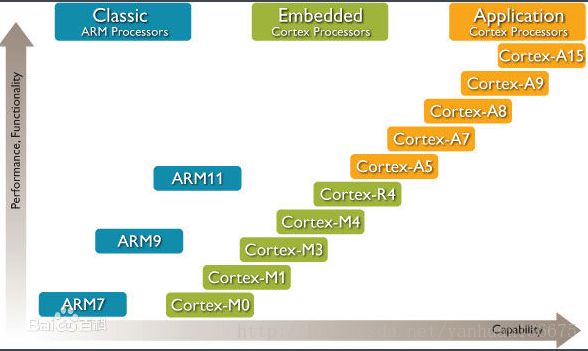

如图为ARM处理器的发展和产品:

①ARM Cortex™-A 系列应用型处理器可向托管丰富OS平台和用户应用程序的设备提供全方位的解决方案,从超低成本手机、智能手机、移动计算平台、数字电视和机顶盒到企业网络、打印机和服务器解决方案。—移动应用端

②ARM Cortex-R实时处理器为要求可靠性、高可用性、容错功能、可维护性和实时响应的嵌入式系统提供高性能计算解决方案。—实时性处理器

③ARM Cortex™-M处理器系列是一系列可向上兼容的高能效、易于使用的处理器,这些处理器旨在帮助开发人员满足将来的嵌入式应用的需要。这些需要包括以更低的成本提供更多功能、不断增加连接、改善代码重用和提高能效。Cortex-M 系列针对成本和功耗敏感的MCU和终端应用。—微控制器

ARM处理器的通信图(示例为ARM920T)

详细解说:

ARM9TDMI为处理器核心(速度400MHz),从MMU(Memory Management Unit的缩写,中文名是内存管理单元,包括数据cache和指令cache)调取数据(当MMU中有数据为cache命中,当MMU中没有数据为cache未命中),cache中没有数据时从内存中调取数据。 —– 内存管理算法。

BUS(总线)分为AHB BUS(高速总线)和APB BUS(外设总线)。

AHB BUS用来高速传输,如LCD ( Liquid Crystal Display 的液晶显示器的简称)挂载在高速总线上(在ARM920T中为100MHz),USB Host,NAND Ctrl,Camera。

APB BUS上挂载USB Device,GPIO。

Ps:速度要匹配才能够准确通信。

总线(Bus)

是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束, 按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。

详细解说:

地址总线是CPU用来指定存储单元(二进制编码),决定了CPU能访问的最大内存空间,如10根总线能最大访问1024位二进制数据(1B),32位系统能最大访问4GB(2^32-1)。

数据总线是CPU与其他器件之间的数据传输通道,数据总线的宽度决定了CPU和外界的数据传输数据。每条数据线一次只能传输一位二进制数据,如8根数据线一次课传输一个8位二进制数据(即1个字节)。

控制总线是对外部器件进行控制,控制线的宽度决定了CPU对外部器件的控制能力。

总线通信方式

①串行通信和并行通信

串行通信是指使用一条数据线,将数据一位一位地依次传输,每一位数据占据一个固定的时间长度。其只需要少数几条线就可以在系统间交换信息,特别适用于计算机与计算机、计算机与外设之间的远距离通信。(最低只需要1根数据线,数据按位传输)

并行通信是指一组数据的各数据位在多条线上同时被传输,各数据位同时传输,传输速度快、效率高。并行数据传输只适用于近距离的通信。

Ps:并行接口的数据传输率比串行接口快8倍,标准并口的数据传输率理论值为1Mbps(兆比特/秒)

②单工、半双工和全双工

信息只能单向传送为单工;

信息能双向传送但不能同时双向传送称为半双工;

信息能够同时双向传送则称为全双工。

③同步通信和异步通信

同步通信是一种bit同步通信技术,要求发收双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使发收双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

异步通信在发送字符时,所发送的字符之间的时隙可以是任意的。但是接收端必须时刻做好接收的准备。发送端可以在任意时刻开始发送字符,因此必须在每一个字符的开始和结束的地方加上标志,即加上开始位和停止位,以便使接收端能够正确地将每一个字符接收下来。

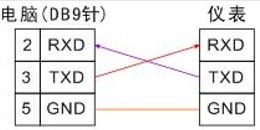

串口总线通信

DB9串口示意图

Ps:DB9属于串行(按位传输),异步(没有时钟线),全双工(分为RXD和TXD)。

电脑上常见的DB接口有:

串行通信接口RS232 9针 –DB9

显示器 VGA 15针 – DB15

并行打印机 LPT 25孔 -DB25

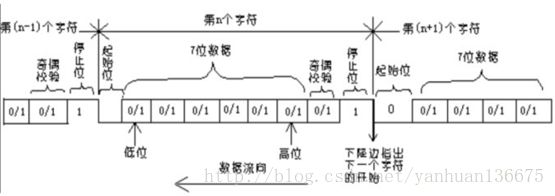

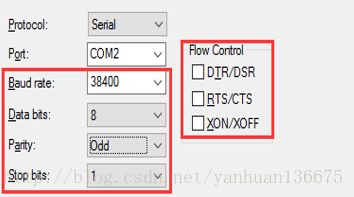

串口通信时序

详细解说:

Baud rate(波特率):单位时间内载波参数变化的次数,如每秒钟传送240个字符,而每个字符格式包含10位(1个起始位,1个停止位,8个数据位),这时的波特率为240Bd,比特率为10位*240个/秒=2400bps。

Data bits:一次传输的位数,两者一定要匹配,在一次传输之后有校验位,不包含校验位;

奇校验(Odd Parity): 就是让原有数据序列中(包括你要加上的一位)1的个数为奇数;

偶校验(Even Parity):就是让原有数据序列中(包括你要加上的一位)1的个数为偶数;

只能检查奇数个位的变化,当一次变化偶数变化就检查不出来。

Row Control:流控

DTR(Data Terminal Ready):数据终端准备

DSR(Data Set Ready):数据发送准备

RTS(Request To Send):请求发送

CTS(Clear To Send):清除发送

XON/XOFF(通信速率匹配协议):异步通信中,用于数据传输速率大于等于1200b/s时进行速率匹配,方法是控制发送方的发速率以匹配双方的速率。

过程:起始位->地位…高位->校验位->停止位

TTL、RS232、RS485(电平标准)

单片机CPU一般都提供TTL电平的UART(Universal Asynchronous Receiver and Transmitter,通用异步收发器)通信接口,它是一种通用的数据通信协议,它包括了RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范。

▶TTL电平:输出低电平要小于0.8V,高电平要大于2.4V;输入低于1.2V就认为是0,高于2.0V就认为是1;

▶RS232电平:逻辑1的电平为-3~-15V,逻辑0的电平为+3~+15V,介于-3~+3V之间的电压无意义;

▶RS485电平:差分信号-2500mv~-200mv为逻辑0;差分信号+2500mv~+200mv为逻辑1;-200mv~+200mv为高阻状态。

MAX232芯片是 TTL电平与RS232电平的专用双向转换芯片,可以TTL转RS-232,也可以RS-232转TTL。

TTL电平一般用于芯片与芯片之间的通信;RS232采用了正负逻辑电平,提高线路的抗干扰性最远可以达到15米左右;如果更远的距离会采样RS485,它使用两线制的差分信号传输,最远可至1200米;RS232全双工只支持点对点通讯(1:1),RS485半双工或单双工支持总线形式通讯(1:N)。

I2C总线(串行,半双工,同步)

I2C是由Philips公司发明的一种串行数据通信协议,仅使用两根信号线:SerialClock(简称SCL)和SerialData(简称SDA)。

I2C是总线结构,1个Master,1个或多个Slave,各Slave设备以7位地址区分,地址后面再跟1位读写位,表示读(=1)或者写(=0),所以我们有时也可看到8位形式的设备地址,此时每个设备有读、写两个地址,高7位地址其实是相同的。—地址+读(1)/写(0)

系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份,具体可以看相应芯片的datasheet。

I2C总线通信时序

过程:起始信号->地址(选址)->数据->应答信号(ack/nack)->结束信号

详细解说:

①空闲状态

I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线。

②起始位与停止位的定义

起始信号:当SCL为高期间,SDA由高到低的跳变;启动信号是一种电平跳变时序信号,而不是一个电平信号。

停止信号:当SCL为高期间,SDA由低到高的跳变;停止信号也是一种电平跳变时序信号,而不是一个电平信号。

③数据的有效性

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定(锁死),只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

Ps:SCL高,传输数据有效; SCL低,SDA才能变化。

④ACK/NACK

发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。 应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。 对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。 如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号P。

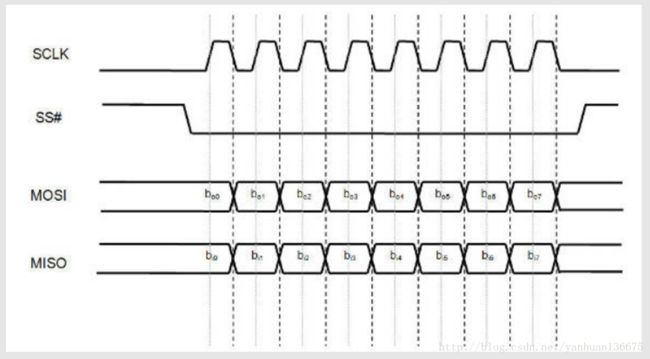

SPI总线(串行,半双工,同步)

SPI全称是串行外设接口(Serial Peripheral Interface),是由Motorola提出的一种全双工同步串行通信接口,通信波特率可以高达5Mbps,但具体速度大小取决于SPI硬件。SPI接口具有全双工操作,操作简单,数据传输速率较高的优点,但也存在没有指定的流控制,没有应答机制确认是否接收到数据的缺点。

SPI总线只需四条线(如图所示)就可以完成MCU与各种外围器件的通讯:

▶MOSI – Master数据输出,Slave数据输入

▶MISO – Master数据输入,Slave数据输出

▶SCK – 时钟信号,由Master产生

▶/CS – Slave使能信号,由Master控制,片选。

SPI通信采用主从模式(Master-Slave)架构,一般为一个Master和多个Slave的应用模式。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

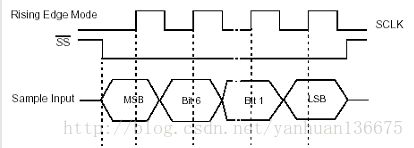

SPI总线通信

SPI是[单主设备(single-master )]通信协议,这意味着总线中的只有一支中心设备能发起通信。当SPI主设备想读/写[从设备]时,它首先拉低[从设备]对应的SS线(SS是低电平有效),接着开始发送工作脉冲到时钟线上,在相应的脉冲时间上,[主设备]把信号发到MOSI实现“写”,同时可对MISO采样而实现“读”。

详细解说:

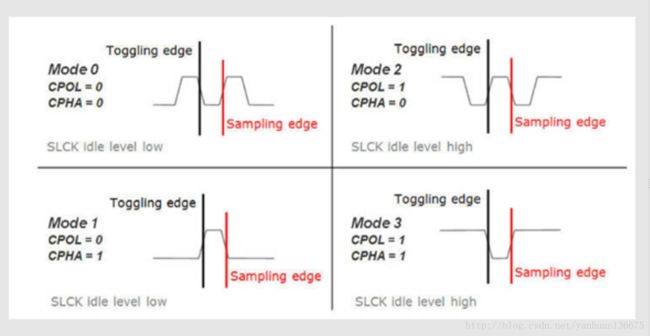

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响,SPI主模块和与之通信的外设音时钟相位和极性应该一致。

▶如果CPOL=0,串行同步时钟的空闲状态为低电平;

▶如果CPOL=1,串行同步时钟的空闲状态为高电平;

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

▶如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;

▶如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样;

一般根据从设备配置,需要两边相同。

详细解说:

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如上右图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。SPI接口没有指定的流控制,没有应答机制确认是否接收到数据。

内存

根据内存的工作原理划分出的两种内存:SRAM(Static Random Access Memory)与DRAM(Dynamic Random Access Memory)

▶DRAM是一种以电荷形式进行存储的半导体存储器,每个存储单元由一个晶体管和一个电容器组成。数据存储在电容器中。电容器会由于漏电而导致电荷丢失,因而DRAM器件是不稳定的。为了将数据保存在存储器中,DRAM器件必须有规律地进行刷新。

▶SRAM每个存储单元需要四到六个晶体管和其他零件,接通代表1,断开表示0,并且状态会保持到接收了一个改变信号为止。这些晶体管不需要刷新,但停机或断电时,它们同DRAM一样,会丢掉信息。SRAM的速度非常快,通常能以20ns或更快的速度工作。

Ps:除了价格较贵外,SRAM芯片在外形上也较大,与DRAM相比要占用更多的空间。SRAM的高速和静态特性使它们通常被用来作为Cache存储器。

SDRAM(Synchronous Dynamic Random Access Memory)在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;

DDR(Double Data Rate SDRAM)内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据;

在嵌入式MCU中,cache一般是SRAM,外接内存一般都支持SDRAM,现在的ARM处理器普遍都可以支持DDR内存。SDRAM单片大小一般最大到64MB左右,而DDRAM可以到GB。

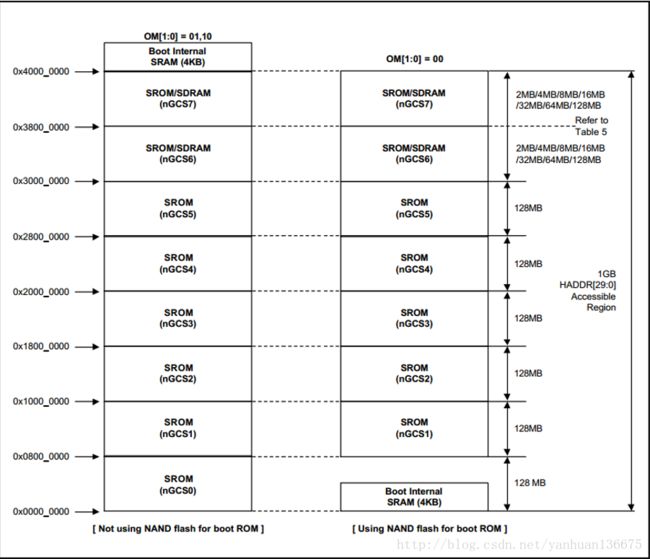

S3C2440 内存映射

详细解说:

S3C2440对外引出了27根地址线ADDR0~ADDR26,它最多能够寻址128MB,而S3C2440的寻址空间可以达到1GB,这是由于S3C2440将1GB的地址空间分成了8个BANKS(Bank0~Bank7),其中每一个BANK对应一根片选信号线nGCS0~nGCS7,当访问BANKx的时候,nGCSx管脚电平拉低,用来选中外接设备, S3C2440通过8根选信号线和27根地址线,就可以访问1GB。

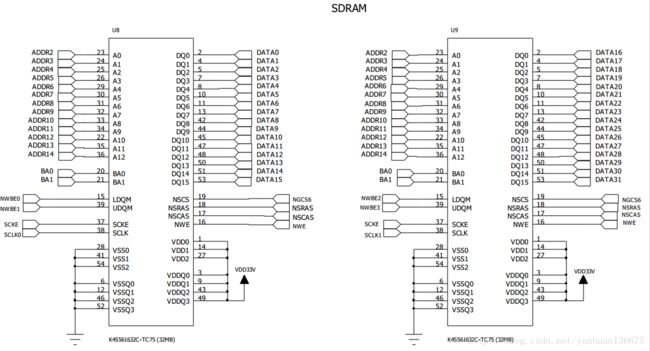

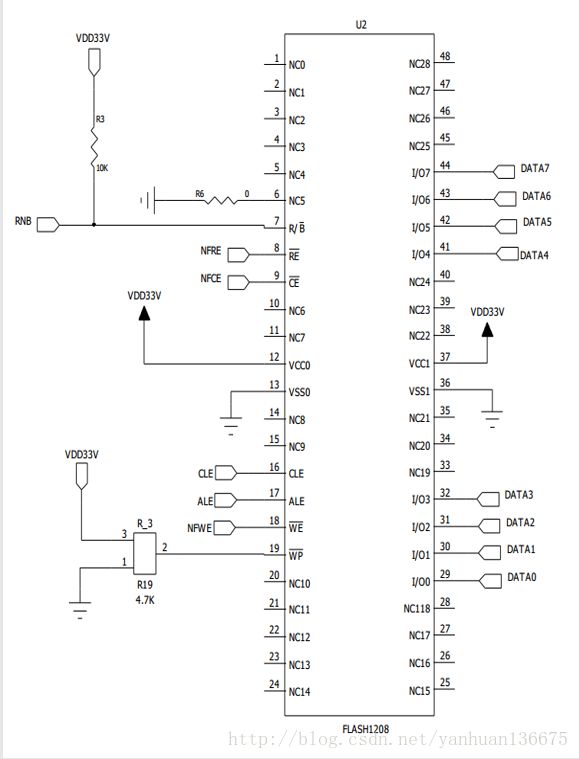

FL2440原理图

详细解说:

将两片32M内存的SDRAM串联,构造成64M内存的SDRAM。

SDRAM的内部是一个存储阵列,阵列就类似于表格一样,有行、列之分,这样我们要访问(读、写)一个单元,就要先指定一个行地址,一个列地址,这样就找到了该单元,这就是SDRAM的寻址的基本原理。这里的单元我们一般称为存储单元,而整个表格称为逻辑BANK(Logical Bank , L-BANK),一般每个SDRAM都会有4个L-BANK。SDRAM的逻辑结构如下图所示:

- 地址线从addr2~addr14、数据线data0~data31

- BA0、BA1

- 数据掩码信号DQM0,DQM1,DQM2,DQM3;

- SDRAM的时钟有效信号SCKE;

- SDRAM的时钟信号SCLK0,SCLK1;

- SDRAM片选信号nSCS0(它与nGCS6是同一引脚的两个功能);

- SDRAM行地址选通脉冲信号nSRAS;

- SDRAM列地址选通脉冲信号nSCAS;

- 写允许信号nWE(它不是专用于SDRAM的)。

过程:SCKE->SCLKn->nS3C->BANK->nSRAS,nSCAS->读2字节

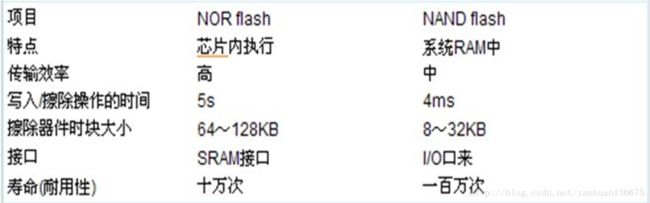

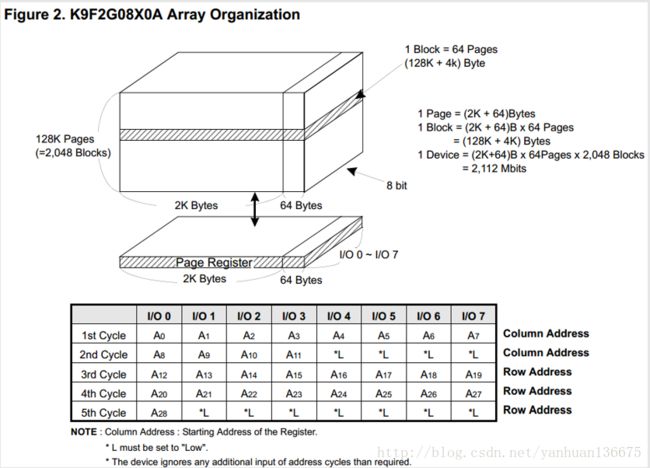

Flash存储器

详细解说:

Flash Memory中文名字叫闪存,是一种长寿命的非易失性(在断电情况下仍能保持所存储的数据信息)的存储器。按功能特性分为两种:一种是NOR型闪存,以编码应用为主,其功能多与运算相关;另一种为NAND型闪存,主要功能是存储资料,如数码相机中所用的记忆卡。Intel于1988年首先开发出Nor flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结结,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。

NorFlash 有自己的数据和地址总线,因此可采用类似RAM的随机访问。NorFlash的特点是芯片内执行(XIP: eXecute In Place),这样应用程序应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。如果uboot中的ro段就可以直接在 NorFlash上运行,只需要把rw段和zi段拷贝到RAM中运行即可。

Nand Flash器件使用复杂的I/O口来串行的存取数据,8个引脚用来传送控制,地址和数据信息。由于时序较为复杂,所以一般CPU最好集成NAND控制器。 另外由于NandFlash没有挂接在地址总线上,所以如果想用NandFlash作为系统的启动盘,就需要CPU具备特殊的功能。

NandFlash和NorFlash的共性首先表现在向芯片中写数据必须先将芯片中对应的内容清空,然后再写入,也就是通常说的“先檫后写”。只不过NorFlash只用檫写一个字,而NandFlash需要擦写整个块。

(1)应用程序对NorFlash操作以“字”为基本单位。为了方便对大容量NOR闪存的管理,通常将NOR闪存分成大小为128KB或者64KB的逻辑块,有时候块内还分成扇区。读写时需要同时逻辑块号和块内偏移。

(2)应用程序对NandFlash操作是以“块”为基本单位。NandFlash的块比较小,一般是8KB,然后每块又分成页,页的大小一般是512字节。要修改NandFlash中一个字节,必须重写整个数据块。

(2)Nandflash出于成本的考虑,出厂时允许有坏块,使用过程中也可以产生坏块,所以在进行数据读写时通常都会进行数据ECC检测。而Norflash则不存在坏块问题,这也导致不同flash今后选择的文件系统也不一样。

Ps:

1 Device = 2048 Block

1 Block = 64 Page

1 Page = 2048 + 64 B (此处的64B空间是判断2048 B是否存在坏块 —– CRC循环冗余校验)

擦除的最小单位是 1 个 Block (128KB)

写的最小单位是 1 个 Page (2KB—–0x20000)

参考网页资料

百度文库搜索: TTL RS232 RS485

串口基础知识: http://www.cnblogs.com/stevenxiu/p/5849337.html

百度文库搜索: i2c总线协议

I2C总线协议介绍 : http://blog.csdn.net/subkiller/article/details/6854910

GPIO模拟I2C总线代码: http://www.cnblogs.com/aceheart/articles/3307477.html

百度文库搜索: SPI总线协议

I2C和SPI协议: http://blog.csdn.net/ce123/article/details/6878547

SPI总线协议及时序图: http://blog.163.com/sunshine_linting/blog/static/44893323201181482335951/

SDRAM工作原理 : http://blog.sina.com.cn/s/blog_8e27098301019jgs.html

Nandflash Norflash比较: http://www.cnblogs.com/jingzhishen/p/4399110.html