FPGA高速收发器GTX/GTH关于外部参考时钟MGTREFCLK的设计

FPGA高速收发器GTX/GTH关于外部参考时钟MGTREFCLK的设计

0 背景

最近在调试多片FPGA基于GTX高速收发器的芯片间接口通信,FPGA型号为Kintex7-325T。硬件板卡是直接购买第三方厂家的产品。遇到了1个重要问题:“GTX外部参考时钟MGTREFCLK的设计对通信链路的影响”。详见下文。

1 问题描述 & 解决方法

(1) 主FPGA芯片的GTX收发器的外部参考时钟信号由125M差分晶振提供,从FPGA芯片的GTX收发器的外部参考时钟信号由150M差分晶振提供,二者参考时钟的频率不同。

遇到的问题是:当初程序设计2片FPGA之间接口通信速率为1.25Gbps。由于从FPGA的外部参考信号为150M时,GTX的IP核不支持倍频到1.25Gbps,故为满足二者接口两端的通信速率相互一致,我通过将接口通信速率由1.25Gbps修改为1.875Gbps时,才同时满足GTX的IP核的参考时钟为125M和150M均可。

于是,主FPGA端参考时钟MGTREFCLK为125MHz,从FPGA端参考时钟MGTREFCLK为150MHz,二者GTX的IP核lane rate均为1.875Gbps,理论上应该是满足链路通道的正确通信的。完成程序设计之后,开始进行仿真测试,发现主从FPGA的链路通信信道确实建立,但是却每隔一段时间,就会发生信号建立失败,GTX内核复位重启现象,参见下图所示。

至于为什么每隔一段时间后,主从FPGA的通信链路会建立失败,欢迎网友们的指教。

(2) 遇到问题1无法解决后,开始思考其他方法来解决。在以前的项目中有过经验,当主从FPGA基于GTX接口通信时,如果保证两端的外部参考时钟MGTREFCLK频率相同,则不会出现上述的问题1情况。于是重新查阅板卡原理图,发现从FPGA的GTX收发器接口当前Quad的外部参考时钟MGTREFCLK是150M,但是其相邻GTX的Quad的MGTREFCLK是125M。

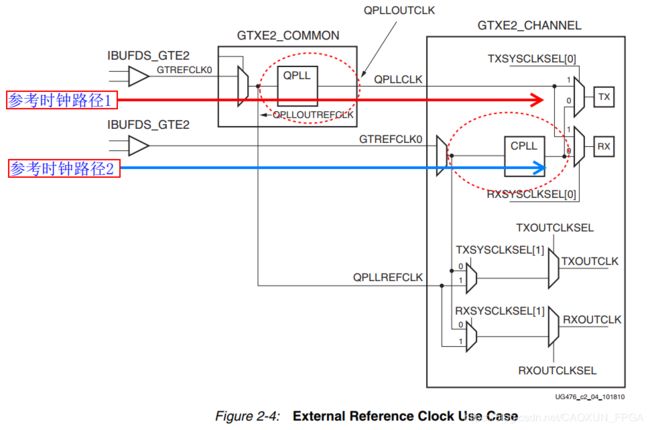

那么,如果当前Quad可以采用相邻Quad的外部参考时钟MGTREFCLK(125M),则从FPGA的GTX收发器能够与主FPGA物理连接的GTX的外部参考时钟保持一致,则问题1就可以解决了。于是查阅官方手册7 Series FPGAs GTX/GTH Transceivers User Guide(UG476),还真发现了该方法是可行的。参见下图所示。

具体程序需要修改的地方:

(1) 外部参考时钟信号MGTREFCLK需要修改。 由当前Quad修改为相邻Quad的参考时钟,这一点大家很容易实现。

本项目为 NET GTXQ0_P LOC=D6; NET GTXQ0_N LOC=D5;修改为 NET GTXQ0_P LOC=H6; NET GTXQ0_N LOC=H5;

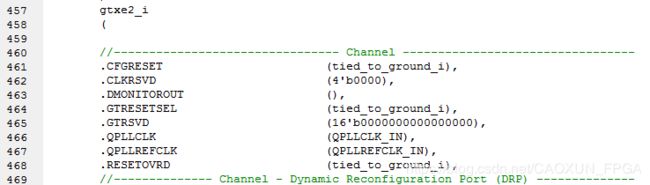

(2)相邻Quad的MGTREFCLK参考时钟信号只能通过GTNORTHREFCLK和GTSOUTHREFCLK时钟信号来给当前Quad提供参考时钟,故需要修改GTX的IP核GTXE2的底层程序。

gtxe2_i子文件需要具体修改的代码为:Line 第479,第481, 第493行。默认的参考时钟信号输入给第481行,但是本项目中因为需要用到相邻Quad外部参考信号,需要由GTNORTHREFCLK输入,故修改479行(根据实际情况修改,有可能是GTSOUTHREFCLK作为输入)。那么对应的CPLLREFCLKSEL信号(line493)也需要根据手册修改为相应的值。

然后通过板级调试,问题得到很好地解决。

2 QPLL和CPLL的异同及选择

由上图可知,QPLL和CPLL均为倍频器,都用于将外部参考时钟信号经过倍频器处理后,给GTXE2_CHANNEL提供链路收发时钟信号和用户工作时钟信号。路径1是MGTREFCLK经过QPLL的信号走向,路径2是MGTREFCLK经过QPLL的信号走向。

(1) QPLL和CPLL的区别?

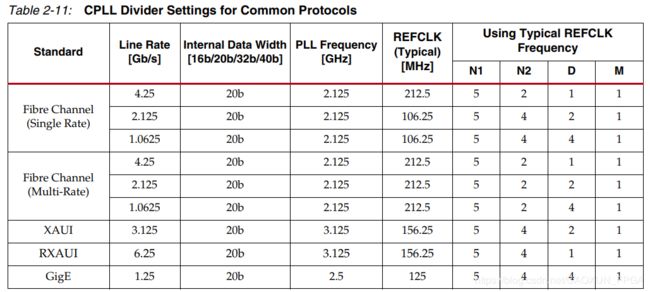

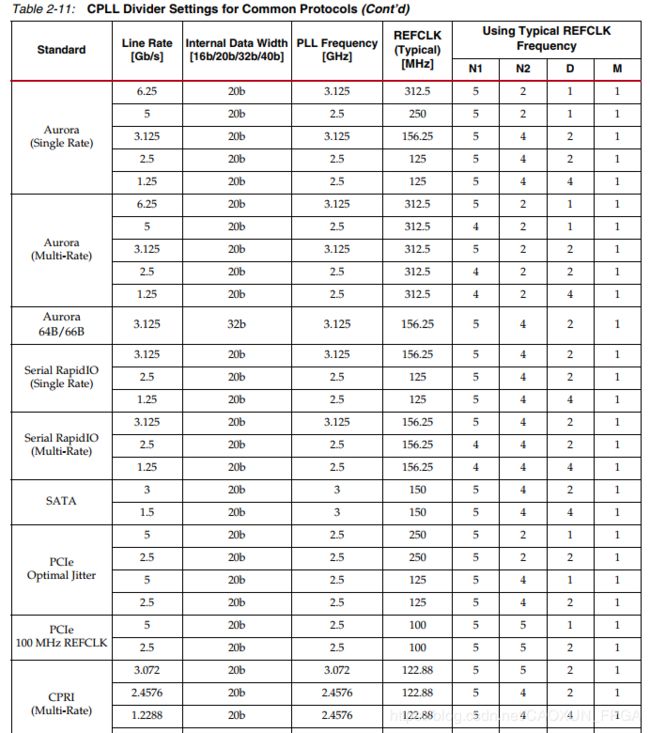

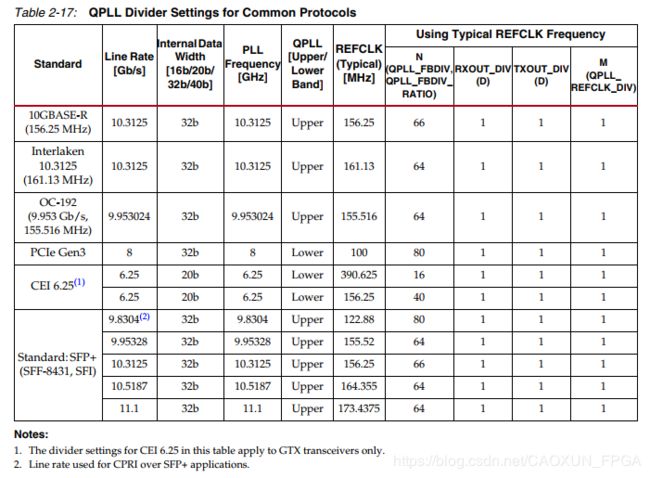

答: 查看手册UG476可知,Xilinx之所以设计2种不同时钟路径来给GTX高速收发器,原因在于二者支持的Line Rate链路通信速率不同。CPLL支持相对低速率的链路通信,QPLL支持相相对高速率的链路通信,且QPLL不支持低频段的链路速率。

例如本项目中,链路速率设定为1.25Gbps,故必须采用路径2的CPLL作为参考时钟的倍频器,如果选择路径1的QPLL倍频器,则GTX链路无法建立和工作,该情况我做过仿真测试验证。CPLL和QPLL支持的链路速率范围详见下图。

由上图可知,CPLL模式下,line rate链路速率范围为:1.25G ~ 6.25Gbps之间。低于1.25G的情况我没有测试过。

由上图可知,QPLL模式下,line rate链路速率范围为:6.25G ~ 11.1Gbps之间。如果在QPLL模式下,链路速率设计为1.25G的情况我测试过,链路信道是建立失败的。

(2) QPLL和CPLL在设计中具体如何选择?

由上图所示,TXSYSCLKSEL[1:0]和RXSYSCLKSEL[1:0]两个选择器的控制信号,来决定GTXE_channel的时钟信号源是采用QPLL路径1还是CPLL路径2。然后根据项目具体链路速率进行选择即可。本项目采用CPLL的路径2,链路速率为1.25Gbps,

故底层代码中 TXSYSCLKSEL[1:0] = 2'b00 , RXSYSCLKSEL[1:0] = 2'b00。

反之,QPLL路径1时,底层代码中 TXSYSCLKSEL[1:0] = 2'b11 , RXSYSCLKSEL[1:0] = 2'b11。