VGA接口电路设计

1.VGA介绍VGA(Video Graphics Array)即视频图形阵列,是IBM在1987年随PS/2(PS/2 原是“Personal System 2”的意思,“个人系统2”,

是IBM公司在1987年推出的一种个人电脑。PS/2电脑上使用的键盘鼠标接口就是现在的PS/2接口。因为标准不开放,PS/2电脑在市场中失败了。

只有PS/2接口一直沿用到今天)一起推出的使用模拟信号的一种视频传输标准,在当时具有分辨率高、显示速率快、颜色丰富等优点,

在彩色显示器领域得到了广泛的应用。这个标准对于现今的个人电脑市场已经十分过时。即使如此,VGA仍然是最多制造商所共同支持的一个标准,

个人电脑在加载自己的独特驱动程序之前,都必须支持VGA的标准。例如,微软Windows系列产品的开机画面仍然使用VGA显示模式,

这也说明其在显示标准中的重要性和兼容性。(来自百度百科)

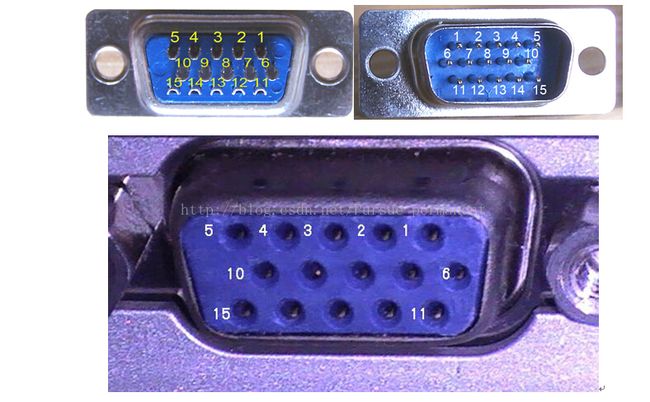

VGA接口就是显卡上面输出模拟信号的接口。VGA接口是一种D型接口,上面共有15针孔,分成3排,每排5个,

VGA接口是目前中低端配置电脑的主流接口。

实物图如下图所示:

VGA显示中,FPGA需要产生5个信号分别是:行同步信号HS、场同步信号VS、R、G、B三基色信号。

接口中最主要的几根线:

| 信号 | 定义 |

| HS | 行同步信号(3.3V) |

| VS | 场 / 帧 同步信号(3.3V) |

| R | 红基色 (0~0.714V 模拟信号) |

| G | 绿基色 (0~0.714V 模拟信号) |

| B | 蓝基色 (0~0.714V 模拟信号) |

2.VGA显示原理

2.1 色彩显示原理

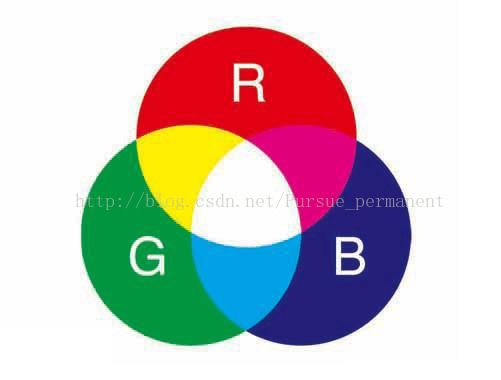

RGB三基色可以组成不同的颜色,如下图所示:

但是按照这个理解三基色(如上图所示)只能组成7种颜色,实际上还有黑色(0,0,0)

三基色颜色编码:

| 颜色 | 黑 | 蓝 | 红 | 紫 | 绿 | 清 | 黄 | 白 |

| R | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| G | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| B | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

实际上,对于显示器来说,RGB三个信号其实是模拟信号,其电平的高低可以表示颜色的深浅。

利用这个原理,我们就可以产生丰富的色彩。为了控制电压的高低,我们就必须用到DA芯片。

例如下图中,FPGA产生RGB三种信号,这时RGB都是多位的数字信号。DA芯片根据信号数字的值,

产生不同电压的模拟信号RGB。

2.2 扫描原理

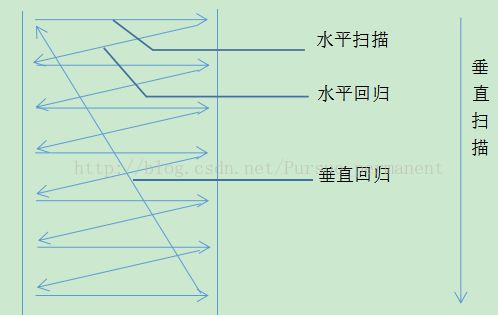

2.2.1光栅扫描过程如下:

显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT(Cathode Ray Tube 阴极射线显像管)屏幕上从左到右(受水平同步信号HSYNC控制)、从上到下(受垂直同步信号VSYNC控制)做有规律的运动。电子束采用光栅扫描方式,从屏幕做上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后完成一帧。此后电子束又回到左上方起点,

开始下一帧的扫描。这种方法也就是常说的逐行扫描显示。

2.2.2 扫描频率

完成一行扫描时间称为水平扫描时间,其倒数称之为行频率,完成一帧的扫描时间称为垂直扫描时间,其倒数称之为场频率,即刷新一屏的频率,

常见的有60hz、75hz等。

2.2.3 扫描时序

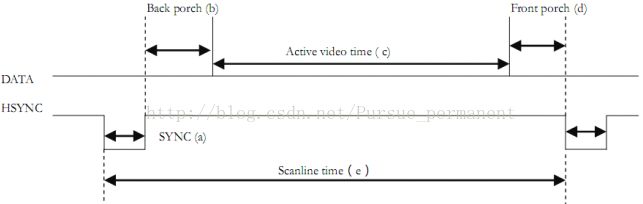

行时序

场时序

HSYNC Signal是用来控制“列填充”, 而一个HSYNC Signal可以分为4个段,也就是a (同步段),b(后廊段),c(激活段),d(前廊段)。

VSYNC Signal是用来控制“行扫描”。而一个VSYNC Signal同样可以分为4个段,也是o (同步段),p(后廊段),q(激活段),r(前廊段)。

2.2.4 VGA支持的规格

以640*480@60为例,一帧所需要的时间:1s/60=0.017s。 1行所需要的时间:0.017s/525=32.39us 单位‘’元素‘’ 所需要时间:32.39us/800=40.5ns

因此在这个显示模式下CRT所需要的时钟频率为:1s/40.5ns=24.69MHZ 四舍五入取 25MHZ可以满足要求。

3. 电路设计

本验证平台为黑金开发板。

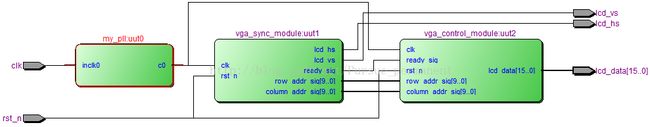

1. my_pll:uut0 为时钟模块 利用altera提供的IP核实现,产生的时钟频率为25MHZ。

2. vga_sync_module:uut1为同步模块,行同步lcd_hs、场同步lcd_vs在此模块产生。ready_sig为电子束打在CRT上面的指示信号,row_addr_sig、column_addr_sig为现在扫描第几行、第几列的指示信号。

3. vga_control_module:uut2 为控制显示什么图形的模块,黑金开发板用16位来控制RGB的混合。R-lcd_data[11:15]、G-lcd_data[5:10]、B-lcd_data[0:4]

module vga_port(

clk ,

rst_n ,

lcd_vs ,

lcd_hs ,

lcd_data

);

input clk ;

input rst_n ;

output lcd_vs ;

output lcd_hs ;

output[15:0] lcd_data ;

wire clk_25mhz ;

my_pll uut0(

.inclk0(clk) ,

.c0(clk_25mhz)

);

wire [9:0] row_addr_sig ;

wire [9:0] column_addr_sig ;

wire ready_sig;

vga_sync_module uut1(

.clk (clk_25mhz) ,

.rst_n (rst_n) ,

.lcd_vs (lcd_vs) ,

.lcd_hs (lcd_hs) ,

.row_addr_sig (row_addr_sig) ,

.column_addr_sig(column_addr_sig) ,

.ready_sig(ready_sig)

);

vga_control_module uut2(

.clk (clk_25mhz) ,

.rst_n (rst_n) ,

.lcd_data (lcd_data) ,

.row_addr_sig (row_addr_sig) ,

.column_addr_sig(column_addr_sig) ,

.ready_sig (ready_sig)

);

endmodule module vga_sync_module(

clk ,

rst_n ,

lcd_vs ,

lcd_hs ,

row_addr_sig ,

column_addr_sig ,

ready_sig

);

input clk ;

input rst_n ;

output lcd_vs ;

output lcd_hs ;

output ready_sig ;

output [9:0] row_addr_sig ;

output [9:0] column_addr_sig ;

reg ready_sig ;

reg [9:0] HS ;

reg [9:0] VS ;

always @ (posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

HS<=10'd0;

else if(HS==10'd799)

HS<=10'd0;

else

HS<=HS+1'b1;

end

always @ (posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

VS<=10'd0;

else if(VS==10'd524&&HS==10'd799)

VS<=10'd0;

else if(HS==10'd799)

VS<=VS+1'b1;

end

always @ (posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

ready_sig<=1'b0;

else if(HS>140&&HS<787&&VS>31&&VS<516)

ready_sig<=1'b1;

else

ready_sig<=1'b0;

end

assign row_addr_sig = ready_sig ? VS-10'd32 :10'd0 ;

assign column_addr_sig = ready_sig ? HS-10'd141 : 10'd0 ;

assign lcd_hs=(HS<96)?1'b0:1'b1;

assign lcd_vs=(VS<2) ?1'b0:1'b1;

endmodule

module vga_control_module(

clk ,

rst_n ,

lcd_data ,

row_addr_sig ,

column_addr_sig ,

ready_sig

);

input clk ;

input rst_n ;

input [9:0] row_addr_sig ;

input [9:0] column_addr_sig;

input ready_sig ;

output[15:0] lcd_data ;

reg [15:0] lcd_data ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_data <=16'd0;

end

else if(ready_sig&&column_addr_sig>=1&&column_addr_sig<=640&&row_addr_sig>=1&&row_addr_sig<=400) begin

lcd_data <=16'h3;

end

else

lcd_data<=16'h0;

end

endmodule always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_data <=16'd0;

end

else if(ready_sig&&column_addr_sig>=1&&column_addr_sig<=640&&row_addr_sig>=1&&row_addr_sig<=400) begin

lcd_data <=16'h3;

end

else

lcd_data<=16'h0;

end 完毕——————————————————————————————————————————————————————————————————