综合属性------parallel_case /tanslate_off/tanslate_on/use_dsp48

参考文档《ug901》

Vivado综合工具支持直接在RTL文件或XDC文件中设置综合属性。在Vivado开发套件中,Vivado综合器可综合几种类型的属性。大多数情况下,这些属性有相同语法和行为。

- 若综合器支持该属性,它将使用该属性,并创建反映已使用属性的逻辑。

- 若工具无法识别指定的属性,则Vivado综合会将属性及其值传递给生成的网表。

假设开发流程中,后续的工具可以使用该属性。 例如,LOC约束综合时候不会使用,但约束由Vivado布局器使用,则由Vivado综合器转发。

支持的属性

想要改进综合的结果,最有效的办法就是利用XDC约束文件来进行综合。

- PARALLEL_CASE (Verilog Only)

Parallel case 只适用于Verilog设计。此属性将强制将case语句构成为并行多路复用器,这也可防止将case语句转换为带有优先级的if-else级联

exe1:

(* parallel_case *)

casex select

4‘b1xxx: res = data1;

4‘bx1xx: res = data2;

4‘bxx1x: res = data3;

4‘bxxx1: res = data4;

endcaseexe2:

(* parallel_case *) case select

3’b100 : sig = val1;

3’b010 : sig = val2;

3’b001 : sig = val3;

endcase- TRANSLATE_OFF/TRANSLATE_ON

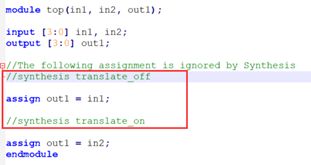

这指示综合工具忽略一段代码。该属性通过放在注释行中来实现,且注释必须以synthesis、synopsys、pragma中的一个关键词为开头。但注意:如果需要忽视的代码块会影响到设计功能表现,仿真器会试图调用这段代码,因此会出现“mismatch”的情况。该属性只能在RTL中设置,Verilog示例如下:

// synthesis translate_off

Code…

// synthesis translate ontranslate_off和TRANSLATE_ON两个属性用于指导综合工具忽略一片代码块(blocks of code)。这可以用于忽略与Synthesis无关的源代码,例如Simulation Code。这些属性在RTL代码的注释中给出。注释(comment)应该从一下的关键字之一开始

- synthesis

- synopsys

- pragma

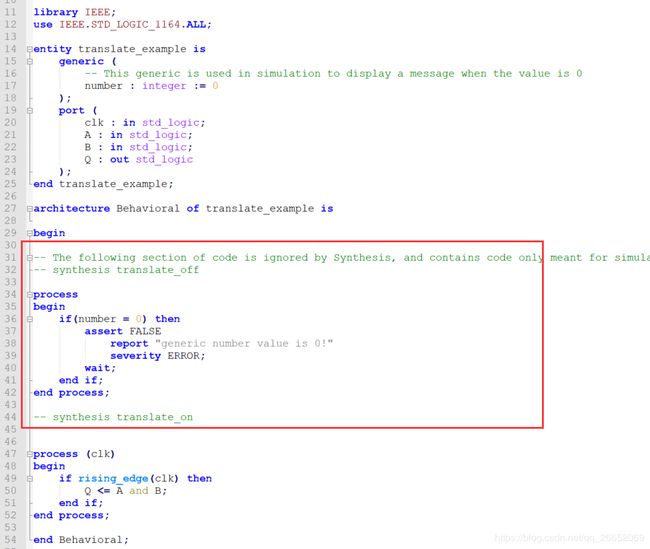

TRANSLATE_OFF 用于启动要忽略的代码段,而TRANSLATE_ON结束要忽略的代码段,且这些属性不能嵌套。

请注意translate语句之间包含的代码类型。如果是影响设计的行为的代码,则仿真器可以使用该代码并创建一个simulation mismatch。

Verilog Example

VHDL Example

-- synthesis translate_off

...Code to be ignored...

-- synthesis translate_on- USE_DSP48

该属性允许用户控制综合工具处理算术结构的方式。默认情况下,乘法器(mults),乘加器(mult-add),乘减(mult-sub)和乘累加(mult-accumulate)类型结构会进入DSP48模块。加法器、减法器和累加器也可以进入这些块(Bloacks),但默认情况下是使用结构(fabric)实现而不是用DSP48模块。如果未指定属性,则vivado Synthesis的默认行为是确定正确的行为。

该属性会覆盖默认行为并强制将这些结构强制转换为DSP48块,并将其置于RTL中signals,architectures和components,entities和module上,具有以下优先级:

- Signals

- Architectures and components

- Modules and entities

此属性的可接受值为“yes”和“no”。

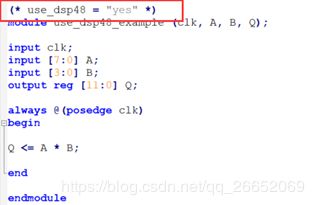

Verilog Example

(* use_dsp48 = "yes" *) module test(clk, in1, in2, out1);VHDL Example

attribute use_dsp48 : string;

attribute use_dsp48 of P_reg : signal is "no";

放置位置

重点说一下USE_DSP48,这句话可以放在模块的前面,也可以放在reg声明的前面,如下:

(*use_dsp48="yes"*)module COUNTER(

input clk,

input rst,

output [7:0] cnt

);

reg [7:0] cnt_tmp = 8‘b0;

always @(posedge clk,posedge rst)

if(rst)

cnt_tmp <= 8‘b0;

else

cnt_tmp <= cnt_tmp + 1‘b1;

assign cnt = cnt_tmp;

endmodule

综合后的资源占用如下:

放到寄存器声明前面

module COUNTER(

input clk,

input rst,

output [7:0] cnt

);

(*use_dsp48="yes"*)reg [7:0] cnt_tmp = 8‘b0;

always @(posedge clk,posedge rst)

if(rst)

cnt_tmp <= 8‘b0;

else

cnt_tmp <= cnt_tmp + 1‘b1;

assign cnt = cnt_tmp;

endmodule

综合后的资源占用如下,可以看到跟放到模块前面的资源使用情况是一样的。但这只是针对计数器这么一个简单的模块,如果你的模块中还有其它更复杂的逻辑,那么建议使用第二种方法,只对某些特定的逻辑使用DSP单元。