MYIR-ZYNQ7000系列-zturn教程(9):将bit文件固化到QSPI_Flash

开发板环境:vivado 2017.1 ,开发板型号xc7z020clg400-1。

我们用FPGA最后生成的是二进制bit文件,bit文件下载到开发板是在内存里运行如果断电程序会丢失。如果我们用FPGA生成的bit文件和zynq核生成的fsbl合成一个BOOT.bin文件,这个zynq核配置了DDR核QSPI_Flash,然后将这个BOOT.bin文件下载到QSPI_Flash让开发板运行在QSPI_Flash启动模式就能让开发板断电程序也不会丢失。如下图所示

Step1 这是已经新建好的一个vivado 流水灯的fpga工程

Step2 点击Flow Navigator 下的Create Block Desion新建一个Block Desion

点击OK

Step3 点击工作区的Add IP添加IP核,在弹出的搜索栏Search中输入zynq,发现可以搜到ZYNQ IP核,双击这个ZYNQ核添加到工作区内

添加好的ZYNQ核如下图所示

Step4 双击ZYNQ IP核添加tcl配置文件,然后点击OK(如果不知道怎样添加请参考hello_world工程里面有详细步骤)

已经配置好的zynq核,如下图所示

我们配置zynq核时一定不要忘记配置这个QSPI_Flash,有很多人没有这里没有配置

QSPI_Flash导致最后下载到QSPI_Flash时失败

Step 5 点击Run Block Automation进行自动布线

在弹出的对话框中点击OK

自动布线完成后如下图所示

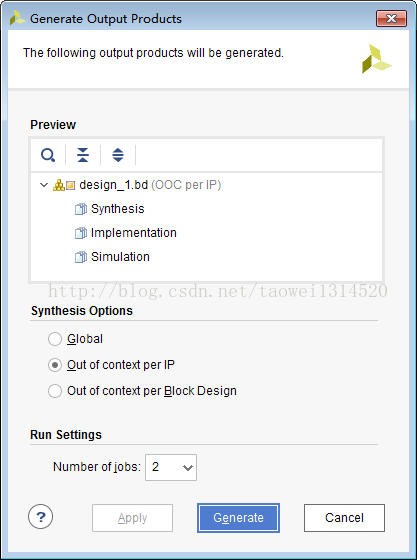

Step6 右击 design_1->Generate Ouput Products 生成综合文件

在弹出的对话框中点击Generate

Step7 右击 design_1->Create HDL Wrapper 生成顶层文件

在弹出的对话框中点击OK

顶层文件生成后如下图所示

将这个流水灯user_led例化到这个zynq核的顶层文件里,如下图所示

流水灯user_led例化到zynq核完成后,如下图所示

Step8 点击Generate Bitstream产生bit文件

点击Yes

点击OK

在弹出的对话框中可以看出bit文件生成成功 ,点击Cancel关闭对话框

Step9 点击菜单栏上的 File->Export->Export Hardware 导出硬件配置文件

在弹出的对话框中勾选Include bitstream ,然后点击OK

Step10 点击菜单栏上的 File->Launch SDK->OK启动SDK

点击OK

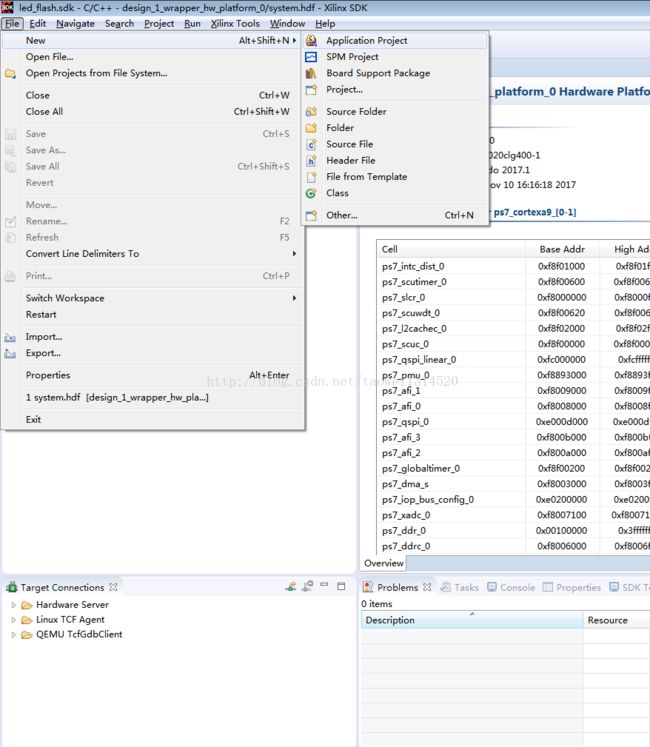

Step11 点击菜单栏上的 File->New->Application Project新建工程新建一个fsbl

在弹出的对话框中填写fsbl

在工程模板中选择Zynq FSBL

Step12 右击 fsbl->Create boot Image, 生成BOOT.bin启动文件

在弹出的对话框中点击Create Image ,生成BOOT.bin

连接开发板电源和jtag下载器,并且将开发板打到SD卡启动模式JP1断开、JP2闭合,如下图所示

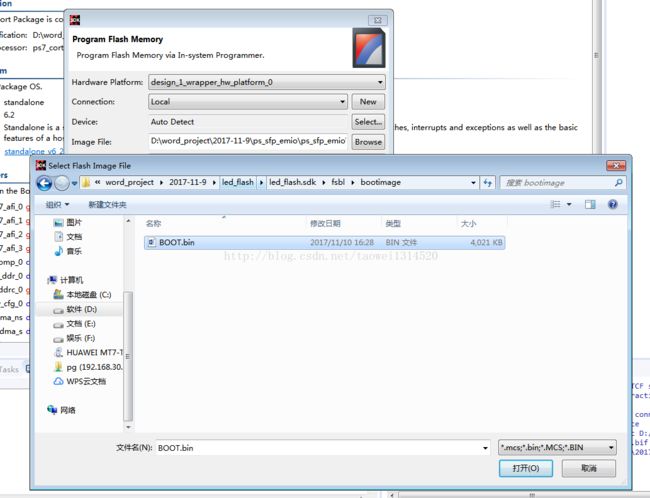

Step13 点击菜单栏上的xilinx Tools-->Program Flash

在弹出的对话框中点击Image File 的Browse将我们生成的BOOT.bin文件添加进来

找到我们生成的BOOT.bin文件,然后点击打开将BOOT.bin文件添加进来,如下图所示

点击Program 将BOOT.bin文件下载到QSPI_Flash

BOOT.bin文件正在往QSPI_Flash中下载,如下图所示

BOOT.bin文件往QSPI_Flash里下载成功,如下图所示

将开发板打到QSPI_Flash模式JP1闭合、JP2闭合,可以看到开发板三色灯D34不停的闪烁,如果将开发板电源断开,

然后重新连接上可以看到开发板依然可以正常运行,可以看到开发板断电程序没有丢失

链接:https://pan.baidu.com/s/1nGBd7itC3n5eI2cGxAfxiA 提取码:p9ma