手撸MIPS32——2、基本流水线设计与实现(理论部分)

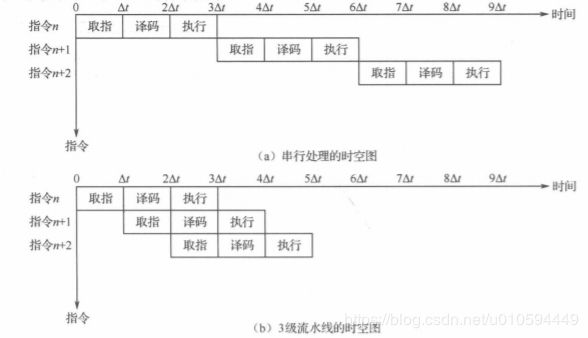

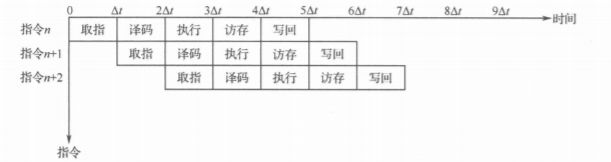

什么是流水线

流水线(pipeline)技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。流水线是Intel首次在486芯片中开始使用的。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。

——from百度百科

处理器流水线设计将微结构划分为两部分,数据通路和控制单元。数据通路完成对指令中操作数的运算处理,控制单元从数据通路中接收指令,并对其进行翻译以告知数据通路如何处理指令。

非转移类R-型(寄存器)指令的流水线数据通路设计

ALU运算指令

以AND 为例

取指阶段设计

程序计数器 PC

指令存储器 IM

PC自增加法器

多路选择器MUX

工作流程:

- 指令存储器IM可用,将PC寄存器的值作为访存地址访问指令存储器

- 从相应的存储单元中读出一条32位指令

- 将PC值+4形成下一条指令的地址

- 将取出的指令送入流水线下一阶段

- 返回步骤1

译码阶段设计

通用寄存器堆:两读一写(两个源一个目的)(每组读:寄存器堆读是能端口re,寄存器堆读地址端口ra,寄存器堆读数据端口rd。每组写:寄存器堆写使能端口we,寄存器堆写地址端口wa和寄存器堆写数据端口rd)

译码控制单元 DCU:产生,内部操作码aluop、操作类型alutype、通用寄存器堆控制信号(通用寄存器堆读使能信号rreg1,rreg2、寄存器堆写使能信号wreg)aluop用于指定当前指令具体操作,如加法、按位与。alutype用于指定操作的种类,如算术运算、逻辑运算、移位运算等。

工作流程以AND为例:

- 根据AND的op和func字段,由译码控制单元产生控制信号aluop、alutype、rreg1、rreg2和wreg。

- 因为rreg1、rreg2、wreg有效则令rs和rt字段作为寄存器索引访问通用存储寄存器堆,从堆里面读数据端口rd1和rd2获得两个源操作数

- 将aluop、alutype、wreg及rd确定过得目的寄存器索引和两个源操作数送入执行阶段

执行阶段设计

算术逻辑单元 ALU:在aluop下完成相应运算

多路选择器 MUX:根据alutype从ALU的输出结果选择一个作为最终结果,将结果写入目的寄存器,在流水线的最后阶段写入通用寄存器堆。

工作流程以AND为例

- 从译码阶段传递来的两个源操作数分别送入ALU的两个输入端src1,src2

- 由aluop控制信号确定对两个源操作数进行按位与,结果在alutype信号的控制下被作为执行阶段的最终结果

- 将寄存器写使能信号wreg、目的寄存器索引及待写入目的寄存器的的数据送入访存阶段

访存阶段设计

因为AND不需要对存储器进行任何访问,故只需要将写寄存器使能信号wreg、目的寄存器的索引和待写入目的寄存器的数据传给写回阶段

写回阶段设计

将写使能寄存器wreg、目的寄存器索引、及待写入目的寄存器的数据连接到寄存器堆的写端口,并在时钟上升沿将结果写入寄存器中。

乘法指令

以MULT为例

取指阶段设计

与之前相同

译码阶段设计

译码控制单元DCU产生一个新的控制信号whilo,称其为HILO寄存器写使能信号

工作流程以AND为例:

- 根据MULT的op和func字段,由译码控制单元产生控制信号aluop、alutype、rreg1、rreg2和wreg和whilo。

- rreg1、rreg2有效、wreg无效、whilo有效,rs和rt字段作为寄存器索引访问通用存储寄存器堆,从堆里面读数据端口rd1和rd2获得两个源操作数,

- 将aluop、alutype、wreg,whilo及两个源操作数送入执行阶段,rd字段尽管仍然送入,但对MULT而言无意义

执行阶段设计

算术逻辑单元 ALU:增加一个输出mulres(64位)用于保存乘法指令运算结果。

mulres不需要经过多路选择器MUX,而是与HILO寄存器写使能信号whilo及通用寄存器堆写使能信号wreg一起直接送入流水线下一级的访存阶段

访存阶段设计

因为MULT不需要对存储器进行任何访问,故将从执行阶段传来的控制信号、地址信号和数据信号再向下传递给写回阶段。比之前多了HILO寄存器写使能信号whilo和待写入HILO的数据

写回阶段设计

新增HILO寄存器(具有两个写数据端口hi_i和lo_i两个读数据端口hi_o和lo_o及一个写使能端口we)

写回阶段会将whilo及运算结果连接到HILO寄存器的写使能端口和写数据端口。其中hi_i连接乘法结果高32位,lo_i连接乘法结果低32位,并在上升沿处将结果写入HILO寄存器中。此外通用寄存器堆写使能信号wreg被设置为无效。

数据移动指令

以MFLO为例

取指阶段设计

与之前相同

译码阶段设计

- 根据MFLO的op和func字段,由译码控制单元产生控制信号aluop、alutype、rreg1、rreg2和wreg和whilo。

- rreg1、rreg2无效、wreg有效、whilo无效,将上述控制信号及rd字段送入执行阶段。rs,rt字段仍然会被送到两个读寄存器地址端看偶,但通用寄存器堆读使能信号无效故无法读取

执行阶段设计

相比之前多了一个多路选择器MUX,其输出称为moveres,该阶段从HILO寄存器读数据端口hi_o和lo_o获取HILO寄存器的值,然后根据aluop选择其中一个送给moveres,对于本例而言传递的是LO寄存器的值。然后在控制信号alutype的作用下,通过另一个mux选择moveres作为待写入目的寄存器的数据,传递给下一级,同时传递的还有目的寄存器索引、和控制信号whilo和wreg

访存阶段设计

与之前相同。

控制信号、地址信号和数据信号继续向下传递。

写回阶段设计

与之前相同。

对于本例而言,LO寄存器的值在通用寄存器写使能信号wreg的控制下,在时钟上升沿被写入通用寄存器。

移位指令

以SLL为例

SLL rd,rt,5

取指阶段设计

与之前相同

译码阶段设计

rt作为索引通用寄存器,sa确定移位位数,结果存入rd,rs未被使用全设为0。

rt字段作为索引被送入通用寄存器堆读地址端口ra2,从寄存器堆读数据端口rd2读出数据,并将其作为源操作数src2传送给流水线下一级。源操作数src1有两个来源,一个来自寄存器堆读数据端口rd1(其他R型地址),另一个来自于指令字的sa字段,即移位位数。因此为了区分,在译码阶段加了一个多路选择器和新的移位使能信号shift。

工作流程:

- 根据SLL指令的op字段和func字段由译码控制单元DCU产生的控制信号aluop、alutype、rreg1、rreg2、wreg、whilo和shift。对于SLL指令,两源操作数一个来自rt另一个来自sa字段,结果写入rd,故rreg1无效、rreg2有效、wreg有效、whilo无效,shift有效。

- 经指令字中rt字段作为索引访问通用寄存器堆,从寄存器堆rd2获得源操作数src2

- 在移位使能信号shift控制下,从多路选择器选择移位位数sa作为另一个源操作数src1

- 将aluop、alutype、wreg、whilo、shift即rd字段确定的目的寄存器索引和两个源操作数送入下一级

执行阶段设计

ALU增加一个输出信号shiftres用于传输移位运算结果,然后在alutype的作用下通过多路选择器选择shifters作为最终运算结果,即待写入目的寄存器的数据。待写入目的寄存器的数据、目的寄存器索引、whilo和wreg传给下一级。

访存阶段设计

与之前相同。

控制信号、地址信号和数据信号继续向下传递。

写回阶段设计

与之前相同。

对于本例而言,待写入目的寄存器结果在通用寄存器写使能信号wreg的控制下,在时钟上升沿被写入通用寄存器。

非转移类I-型(立即数)指令的流水线数据通路设计

ALU运算指令

以ORI rt,rs,imm为例

取指阶段设计

与之前相同

译码阶段设计

I-型ALU运算指令包括ORI、LUI、ADDIU、SLTIU,仅通过op字段可进行区分。出LUI外,剩下的指令需要两个源操作数,一个由rs字段确定通用寄存器,另一个来自于imm字段的16位立即数,需要将这个立即数扩展到32位,此时又分为符号扩展和无符号扩展。结果保存到rt字段的目的寄存器中。

新增模块:

立即数扩展模块ext:在新增的控制信号sext的控制下将16位立即数扩展到32位,sext为1时符号扩展如ADDIU和SLTIU,sext为0是,进行无符号扩展如ORI

左移模块:针对LUI(寄存器高半字置立即数),实现对立即数左移16位

多路选择器1:在新增信号upper的控制下,确定对立即数imm是进行立即数扩展还是左移16位

多路选择器2:因为I型的src2来源不同于R型。新增immsel确定操作数是来自于寄存器堆的读数据端口rd2还是立即数

多路选择器3:因为通用寄存器索引来自于rt而R型指令来自于rd,新增rtsel确定目的寄存器的索引是rt还是rd。

工作流程:

- DCU产生各种控制信号。rreg1、immsel、rtsel及wreg有效,rreg2、whilo、shift无效。立即数需要无符号扩展sext和upper无效

- 使用rs字段作为索引访问通用寄存器堆,在shift的作用下,将从读数据端口rd1获取数据作为src1。在控制信号sext、upper、immsel作用下,立即数无符号扩展后的值作为src2.在控制信号rtsel作用下,选择rt字段作为目的寄存器索引。

- 将wreg、whilo、aluop、alutype及rt确定的目的寄存器索引和两个源操作数送入执行阶段

执行阶段设计

设计和之前无差。

以ORI为例,ALU在aluop的控制下对src1和src2进行按位或操作,结果在alutype下,被作为待写入目的寄存器传到下一级。同时还有待写入目的寄存器索引和控制信号whilo和wreg

访存阶段设计

与之前相同。

控制信号、地址信号和数据信号继续向下传递。

写回阶段设计

与之前相同。

对于本例而言,待写入目的寄存器结果在通用寄存器写使能信号wreg的控制下,在时钟上升沿被写入通用寄存器。

加载指令

以LB rt,offset(base)为例

取指阶段设计

与之前相同

译码阶段设计

DCU多一个控制信号mreg(存储器到寄存器使能信号)

工作流程:

- DCU产生各种控制信号。rreg1、immsel、rtsel及wreg有效,rreg2、whilo、shift无效。立即数需要符号扩展sext有效和upper无效,mreg有效

- 使用rs字段作为索引访问通用寄存器堆,在shift的作用下,将从读数据端口rd1获取数据作为src1即访存基地址。在控制信号sext、upper、immsel作用下,立即数符号扩展后的值作为src2.在控制信号rtsel作用下,选择rt字段作为目的寄存器索引。

- 将mreg、wreg、whilo、aluop、alutype及rt确定的目的寄存器索引和两个源操作数送入执行阶段

执行阶段设计

设计和之前无差。

ALU接收两个源操作数,基地址和偏移量在控制信号aluop的作用下相加得到访存地址daddr,通过信号arithres输出。然后在alutype的作用下,通过多路选择器选择arithres作为最终运算结果,即访存地址daddr,然后传递给访存阶段。同时传递的还有目的寄存器索引,控制信号mreg、whilo和wreg。此外还要向内部操作码aluop传递给访存阶段,以便对访存类型进行判断。

访存阶段设计

新增两个模块:

数据存储器DM:采用可读可写的RAM构建,按字节编址,容量为8KB。I/O端口包括:数据存储使能端口dce、写字节使能端口we、访存地址端口daddr、待写入数据端口din及读取数据端口dout。其中we(4位)有些东西,0的时候读,其他是写,按位不同选择字节、半字和字。读永远读32位,后来会在访存阶段生成专门的读字节使能信号dre,对读出数据的有效字节进行选择

访存控制信号MCU:根据aluop和daddr产生各种控制信号,即dce、we和读字节使能信号dre其中dre,4位。写的时候dre=4’b0000,字节就是1

以LB为例

访存控制单元MCU将dce设置为1,we设置为0。小端模式dre设置为0100,然后根据访存地址从数据存储器端口dout读出数据dm将其送入下一级写回。同时传递得还有mreg、whilo、wreg和dre。执行阶段运算结果dreg也会被送入写回

写回阶段设计

相比之前多一个mux。

该多路选择器在控制信号mreg作用下,判断是将访存阶段的输出数据dm还是执行阶段的运算结果作为待写入目的寄存器的数据。本例而言,会在上升沿从访存阶段的输出数据dm中根据读字节使能信号dre选择有效字节,并扩展32位写入通用寄存器。

存储指令

以SW为例

取指阶段设计

与之前相同

译码阶段设计

多一个连接寄存器堆读数据端口读rd2的信号。

工作流程:

- DCU产生各种控制信号。rreg1、rreg2及immsel有效,mreg、whilo、wreg和shift无效,rtsel可以任何值。立即数需要进行有符号扩展,sext有效,upper无效。

- 使用rs字段作为索引访问通用寄存器堆,在shift的作用下,将从读数据端口rd1获取数据作为src1即访存基地址。在控制信号sext、upper、immsel作用下,立即数符号扩展后的值作为src2.在控制信号rreg2作用下,使rt作为索引访问寄存器堆,将读数据端口rd2获取的数据作为待写入数据存储器中的数据。

- 将mreg、wreg、whilo、aluop、alutype及两个源操作数和待写入存储器数据送入执行阶段

执行阶段设计

增加一条信号线用于将待写入数据存储器中的数据传递给流水线下一级。同时传递的还有daddr及mreg、whilo和wreg

访存阶段设计

增加一条数据线用于将待写入数据存储器中的数据送入数据存储器端口din。

以SW为例

为字存储指令,对存储器进行写操作。访问控制单元MCU将数据存储器的dce设置为1,we设置为4’b1111,dre设置为0.然后根据访存地址将din端口数据存入数据存储器中,同时将控制信号mreg、whilo、wreg、dre传递到写回。

写回阶段设计

因为存储指令在访存阶段已经将数据写入数据存储器,并且控制信号wreg和whilo为无效,因此写回无需任何操作。