Verilog之i2c协议

说明:i2c的作业,有很多东西是参考网上。

时间:2014年5月6日星期二

1.问题描述:

如图所示,已知时钟clk为100k,rst为复位信号,上升沿有效,基于Verilog HDL或者VHDL语言,将A器件内的六个8位数据,按照I2C协议规格送入总线sda,并产生相应的串行时钟scl.

要求(1):写出完整代码;

要求(2):给出仿真波形图。

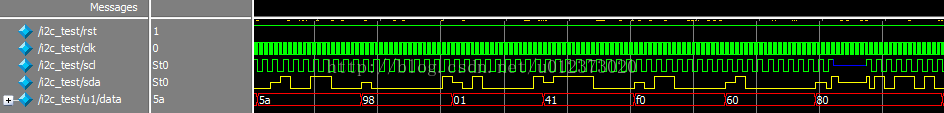

1.1仿真波形图

在波形图中,黄色波形表示sda,红色波形data是为了方便观察sda所传输的数据而设立的。所要传输的6个数据分别为:8’h98, 8’h01, 8’h41, 8’hf0,8’h60, 8’h90;器件地址是自己定义的7'b1011010(因为I2C器件的地址是7位,作业给出的地址是8位)。

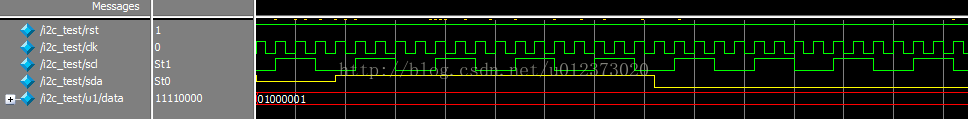

发送数据的放大波形图如下(以发送数据8’h41为例):

1.2完整代码

代码采用Modelsim仿真,编写了Verilog程序和testbench激励文件。

Verilog程序:

modulei2c (scl, sda, clk, rst);

inout scl;

inout sda;

input clk;

input rst;

reg i;

reg rscl = 1'bz;

reg rsda = 1'bz;

reg[7:0] temp, data;

reg[6:0] slave_addr_reg= 7'b1011010; //slave addr

parameter DATA0 = 8'h98;

parameter DATA1 = 8'h01;

parameter DATA2 = 8'h41;

parameter DATA3 = 8'hF0;

parameter DATA4 = 8'h60;

parameter DATA5 = 8'h80;

assign scl = rscl;

assign sda = rsda;

task start;

begin

@(posedge clk);

rsda = 1;

rscl = 1;

@(posedge clk);

rsda = 0;

@(posedge clk);

rscl = 0;

end

endtask

task stop;

begin

rsda = 0;

@(posedge clk);

rscl = 1;

@(posedge clk);

rsda = 1;

@(posedge clk);

rscl = 1'bz;

@(posedge clk);

@(posedge clk);

rsda = 1'bz;

end

endtask

task rw_slave_addr(input[6:0] slave_addr,input rw); begin

repeat(7) begin

@(posedge clk);

rsda = slave_addr[6];

slave_addr={slave_addr[5:0],slave_addr[6]};

temp = temp << 1;

temp[0] = rsda;

@(posedge clk);

rscl = 1;

@(posedge clk);

@(posedge clk);

rscl = 0;

end

data = temp;

@(posedge clk);

rsda = rw;

@(posedge clk);

rscl = 1;

@(posedge clk);

@(posedge clk);

rscl = 0;

@(posedge clk);

rsda = 1'bz;

@(posedge clk);

rscl = 1;

if(sda != 0) $display("ACKerror at time: %t", $time);

@(posedge clk);

@(posedge clk);

rscl = 0;

@(posedge clk);

end

endtask

task send_byte(input [7:0] send_byte);begin

repeat(8) begin

rsda = send_byte[7];

send_byte={send_byte[6:0],send_byte[7]};

temp = temp << 1;

temp[0] = rsda;

@(posedge clk);

rscl = 1;

@(posedge clk);

@(posedge clk);

rscl = 0;

@(posedge clk);

end

data = temp;

rsda = 1'bz;

@(posedge clk);

rscl = 1'b1;

if(sda != 0) $display("ACKerror at time: %t", $time);

@(posedge clk);

@(posedge clk);

rscl = 0;

@(posedge clk);

end

endtask

always@(posedge clk or negedge rst) begin

if(!rst) begin

rscl = 1'bz;

rsda = 1'bz;

end

else begin

start;

rw_slave_addr(slave_addr_reg,0);

send_byte(DATA0);

send_byte(DATA1);

send_byte(DATA2);

send_byte(DATA3);

send_byte(DATA4);

send_byte(DATA5);

stop;

#20;

$stop;

end

end

endmodule

testbench程序:

`timescale1us/1us

modulei2c_test;

wire scl, sda;

reg clk, rst;

initial begin

clk=0;

forever #1 clk=~clk;

end

initial begin

rst=0;

#20 rst=1;

end

i2c u1(scl, sda, clk);

endmodule

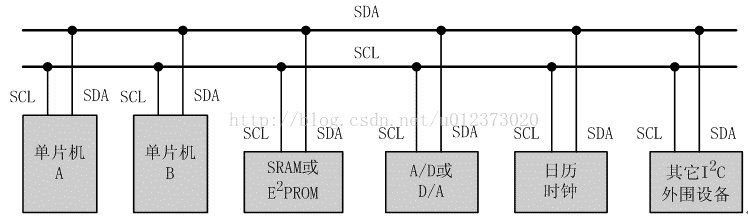

2.I2C概述

常用的串行扩展总线有:I2C(InterICBUS)总线、单总线(1-WIREBUS)、SPI(SerialPeripheralInterface)总线及Microwire/PLUS等。

I2C总线是PHLIPS公司推出的一种串行总线,是具备多主机系统所需的包括总线裁决和高低速器件同步功能的高性能串行总线。

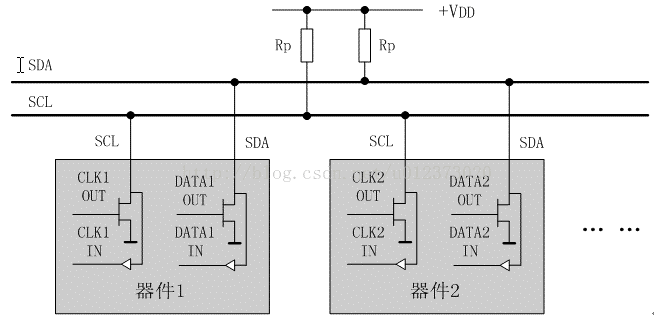

I2C总线只有两根双向信号线。一根是数据线SDA,另一根是时钟线SCL。

I2C总线通过上拉电阻接正电源。当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线“与”关系。

每个接到I2C总线上的器件都有唯一的地址。主机与其它器件间的数据传送可以是由主机发送数据到其它器件,这时主机即为发送器。由总线上接收数据的器件则为接收器。

3.I2C总线的数据传送

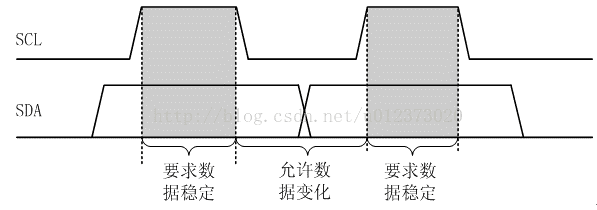

3.1数据位的有效性规定

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

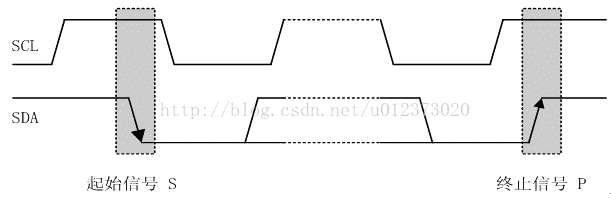

3.2起始和终止信号

SCL线为高电平期间,SDA线由高电平向低电平的变化表示起始信号;SCL线为高电平期间,SDA线由低电平向高电平的变化表示终止信号。

起始和终止信号都是由主机发出的,在起始信号产生后,总线就处于被占用的状态;在终止信号产生后,总线就处于空闲状态。

连接到I2C总线上的器件,若具有I2C总线的硬件接口,则很容易检测到起始和终止信号。对于不具备I2C总线硬件接口的有些单片机来说,为了检测起始和终止信号,必须保证在每个时钟周期内对数据线SDA采样两次。

接收器件收到一个完整的数据字节后,有可能需要完成一些其它工作,如处理内部中断服务等,可能无法立刻接收下一个字节,这时接收器件可以将SCL线拉成低电平,从而使主机处于等待状态。直到接收器件准备好接收下一个字节时,再释放SCL线使之为高电平,从而使数据传送可以继续进行。

3.3数据传送格式

(1)字节传送与应答

每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。

由于某种原因从机不对主机寻址信号应答时(如从机正在进行实时性的处理工作而无法接收总线上的数据),它必须将数据线置于高电平,而由主机产生一个终止信号以结束总线的数据传送。

如果从机对主机进行了应答,但在数据传送一段时间后无法继续接收更多的数据时,从机可以通过对无法接收的第一个数据字节的“非应答”通知主机,主机则应发出终止信号以结束数据的继续传送。

当主机接收数据时,它收到最后一个数据字节后,必须向从机发出一个结束传送的信号。这个信号是由对从机的“非应答”来实现的。然后,从机释放SDA线,以允许主机产生终止信号。

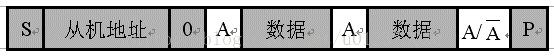

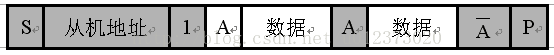

(2)数据帧格式

I2C总线上传送的数据信号是广义的,既包括地址信号,又包括真正的数据信号。

在起始信号后必须传送一个从机的地址(7位),第8位是数据的传送方向位(R/),用“0”表示主机发送数据(T),“1”表示主机接收数据(R)。每次数据传送总是由主机产生的终止信号结束。但是,若主机希望继续占用总线进行新的数据传送,则可以不产生终止信号,马上再次发出起始信号对另一从机进行寻址。

在总线的一次数据传送过程中,可以有以下几种组合方式:

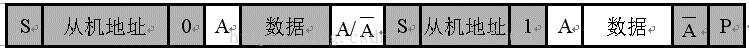

a、主机向从机发送数据,数据传送方向在整个传送过程中不变:

b、主机在第一个字节后,立即由从机读数据

c、在传送过程中,当需要改变传送方向时,起始信号和从机地址都被重复产生一次,但两次读/写方向位正好反相。