《硬件架构的艺术》第3章精华梳理

多时钟处理技术

- 1. 时钟关系

- 2. 面临问题

- 3. 处理技术

- 3.1 时钟命名规则

- 3.2 分模块设计

- 4 跨时钟域信号传输

- 5 跨同步时钟域问题

- 5.1 同频0相位差clk(单时钟设计)

- 5.2 同频恒定相位差clk(反相clk or 对上级clk相位移动)

- 5.3 非同频、可变相位差clk(整数 or 有理数倍时钟)

- 6.标准化传输数据技术

- 6.1 握手信号方法

- 6.2 FIFO

- 6.2.1 同步FIFO

- 6.2.1 异步FIFO

1. 时钟关系

2. 面临问题

3. 处理技术

3.1 时钟命名规则

为了保证综合脚本可以使用通配符来对所有时钟进行操作。

在同步时钟中,可以用以下的命名规则:系统时钟 sys_clk、发送时钟 tx_clk、接受时钟 rx_clk。

不同步时钟中,一个时钟域的信号应该有同样的前缀,比如系统时钟驱动的信号:sys_rom_addr、sys_rom_data。

3.2 分模块设计

4 跨时钟域信号传输

- 控制信号(同步器)

控制信号直接传输可能会导致多个并行触发器进入亚稳态,常用的解决方法是多级同步器(两级及以上)

只有在时钟频率非常高的设计中才要求使用三级同步器电路,一般两级即可。

缺点:增加了电路整体delay - 数据信号(①握手信号; ②异步FIFO)

5 跨同步时钟域问题

起源于同一时钟的多个时钟,相位和频率之间的关系是固定的,可以分为以下类型:

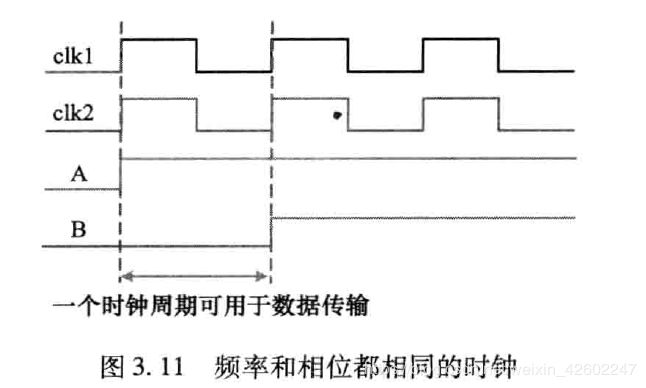

5.1 同频0相位差clk(单时钟设计)

(个人理解同频是period一致)

进行STA分析就可以保证数据正确传输

5.2 同频恒定相位差clk(反相clk or 对上级clk相位移动)

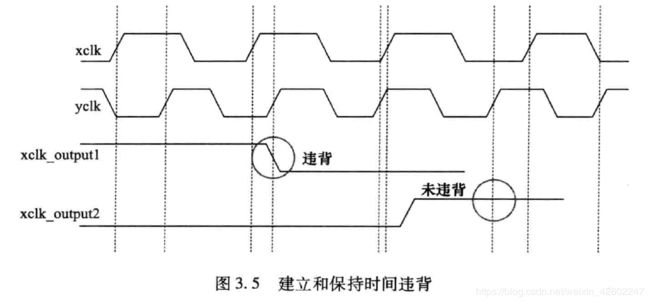

delay约束会变紧,保证组合逻辑的延时满足su和hold即可

5.3 非同频、可变相位差clk(整数 or 有理数倍时钟)

a. 整数倍时钟

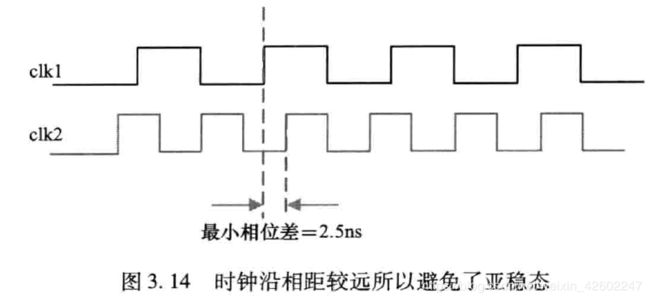

时钟最小相位差=频率较快的时钟period,快时钟传输数据,且满足最小相位差下的su/hold,就不必使用同步器。

为了避免快时钟的数据丢失,源数据至少保持一个目的时钟周期的稳定状态,可以使用有限状态机(FSM)来满足这一要求

b. 有理数倍时钟

①同源时钟有效沿(例如上升沿)最小相位差满足su/hold,不会产生亚稳态。下图为同一个时钟clk的二分频(clk2)和三分频(clk1)

在跨越两个时钟的位置避免使用组合逻辑,以免带来亚稳态,对于增加的任何组合逻辑,需要使用同步器来避免亚稳态。

总结:慢时钟域传递到快时钟域,增加逻辑以保证快时钟只采样一次数据;快时钟传递给慢时钟时,源数据保持至少一个目标时钟的周期,以保证数据不丢失的传递

②两个时钟有效沿间隔性的非常接近(当前有效沿接近,则下一个时钟的裕量一定充足),一定会出现亚稳态,必须使用同步器。

慢时钟域传递给快时钟域,数据不会丢失,但可能会不连贯

快时钟域传递给慢时钟域,数据可能丢失,可以通过FSM来保证源数据保持至少一个目标是中国周期不变。

图中B1为期望输出, B2为实际输出。

③两个时钟有效沿在连续周期中非常接近

源时钟clk1周期10ns,目标时钟clk2周期9ns,4个圈为连续周期接近

源时钟在前(且与目标时钟较近)可能违背su(前两个圈);目标时钟在前可能会违背hold(后两个圈)

策略:为了不丢失数据(不论快-慢还是慢-快),数据至少在两个目的时钟周期稳定,可以使用简单的FSM完成这一任务?,但数据不连贯问题仍然存在。

已标准化的(握手/FIFO)等技术能够解决数据不连贯的问题。

6.标准化传输数据技术

6.1 握手信号方法

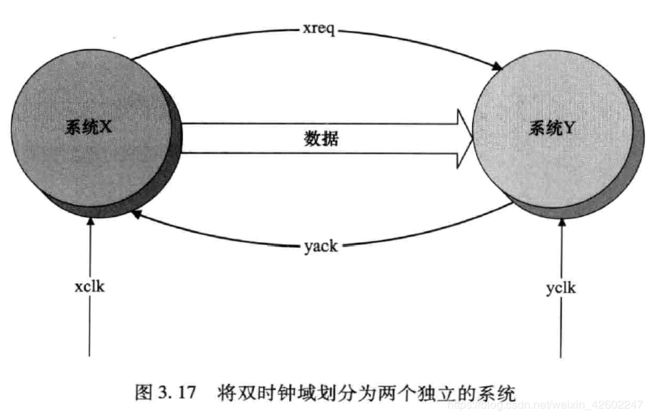

将双时钟域分割成两个独立的系统,使用握手信号xreq和yack发送数据。

总结:

(1)X发送数据和请求(xreq)

(2)xreq请求信号同步至yclk时钟域,生成Y域请求信号yreq2

(3)Y接受数据总线上锁存的信号

(4)Y发出接收信号yack,表明数据接受完毕

(5)X系统同步yack信号为xack2

(6)X系统发送下一个数据

要求:

数据和请求信号,在发送时钟内至少稳定2个时钟上升沿(保证Y域同步器采集到)

缺点:

传递单数据的延时远远大于FIFO,如下图所示时序图,安全传输一个数据需要消耗5个时钟周期

6.2 FIFO

6.2.1 同步FIFO

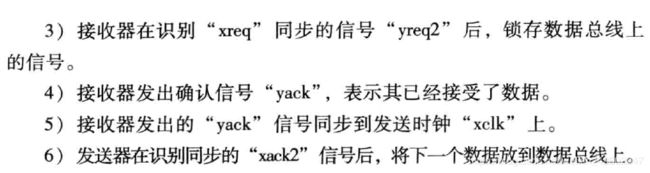

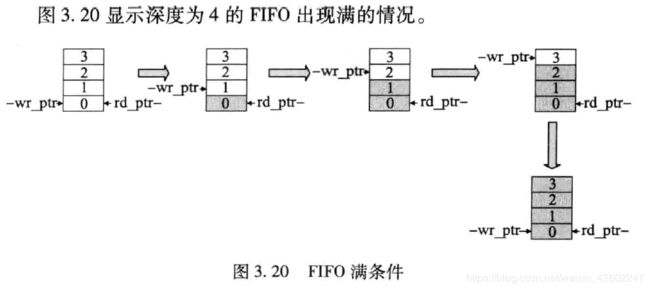

工作方式:

读写指针均在[0:RAM_SIZE-1]内循环,

复位时,读写指针都=0,FIFO空信号有效;

当写指针从RAM_SIZE-1回滚到0时,fifo满信号有效。

读写指针相等时,FIFO要么空要么满,重点是如何将这两种情况区分开。

同步FIFO空满判别 法1

满信号:当写指针+1 == 读指针,且写信号为1时,产生FIFO满信号

![]()

空信号:当读指针+1 == 写指针,且读信号为1时,产生FIFO空信号

![]()

//同步FIFO空满信号

//信号描述:

//wr_ptr、rd_ptr地址指针

//

//产生满信号fifo_full

always@(posedge clk or negedge reset_n) begin:fifo_full_gen

if(~reset_n)

fifo_full <= 1'b0;

else if(wr_fifo && rd_fifo)//读写同时操作,不会发生错误

;//do nothing

else if(rd_fifo)//只有读操作时,fifo不可能满,fifo_full=0

fifo_full <= 1'b0;

else if(wr_fifo && (rd_ptr = wr_ptr + 1'b1))//只有写操作,且读写地址在下一个状态相等

fifo_full <= 1'b1;//满信号警告

end

//产生空信号fifo_empty

always@(posedge clk or negedge reset_n) begin:fifo_empty_gen

if(~reset_n)

fifo_empty <= 1'b0;

else if(wr_fifo && rd_fifo)//读写同时操作,不会发生错误

;//do nothing

else if(wr_fifo)//只有写操作时,fifo不可能空,fifo_empty=0

fifo_empty <= 1'b0;

else if(rd_fifo && (wr_ptr = rd_ptr + 1'b1))//只有读操作,且读写地址在下一个状态相等

fifo_empty <= 1'b1;//空信号警告

end

同步FIFO空满判别法2:计数器

用宽度=FIFO深度的计数器,计数器值=FIFO深度时,满状态;复位时计数器为0(空状态)。写操作递增+1,读操作递增-1。

但在同步器中,法2需要额外的硬件:序列比较器,而且计数器随着FIFO深度的增加而增大,会降低FIFO操作的最高频率。

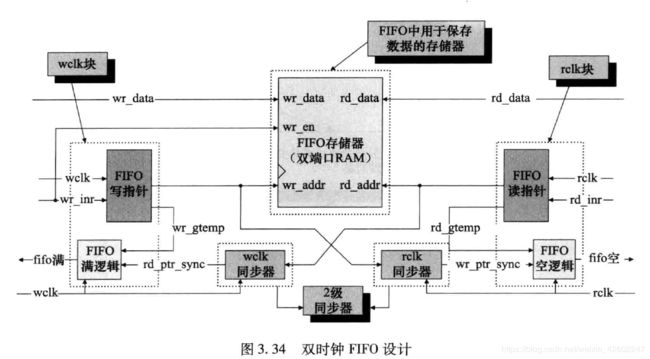

6.2.1 异步FIFO

和握手/同步FIFO比较

和握手信号的区别:握手耗费大量时钟,异步FIFO用在对时钟延时要求更高的环境中

和同步的区别:同步FIFO使用双端口RAM,读写信号一个时钟,异步FIFO的原理差不多,但要注意产生FIFO空/满信号时避免亚稳态现象。

二进制计数器实现指针的弊端

读写时钟分别和各自的时钟同步,彼此异步,使用二进制计数器实现指针,在空满信号指针比较的时候,由于计数器的值发生多位翻转,提高了亚稳态的可能性,错误的指针会带来错误的数据传输。

因此,强烈避免使用二进制计数器实现读写指针。

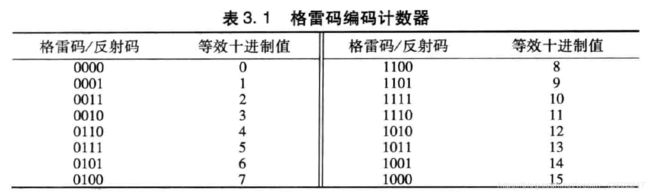

格雷码

同步格雷码计数器很少会导致取样计数器值出现亚稳态,取样后的值最多出现一位错误。例如:

计数器从1010变为1011,只有最后一位翻转,取样逻辑要么读到“1010”旧值,要么读到1011正确值。

相反,二进制计数器1011变为1100的过程有3位发生翻转,取样到错误值的概率也增大了。

格雷码计数器

FIFO空满信号的产生

法一

2^n深度的FIFO指针宽度为n+1

用二进制码来表述,当最高有效位MSB不一样时,FIFO为满,当指针完全一样时,FIFO为空。

例如图3.29,是一种FIFO满情况

由于读写指针以格雷码保存,比较用二进制码进行,

该空满方案缺点:需要4个格雷码二进制码转换器

优点:简单易懂吧

法二:

双时钟FIFO设计,直接对格雷码进行比较,

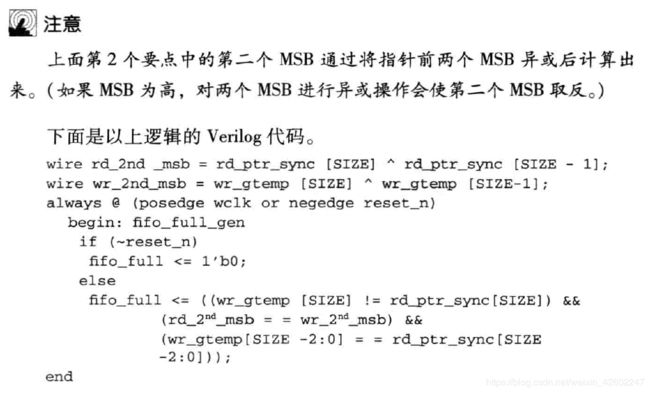

二元n位格雷码,将4bit格雷码最高两位异或,得到n-1位格雷码。

直接通过对格雷码对比产生空满信号的双时钟FIFO电路结构如下

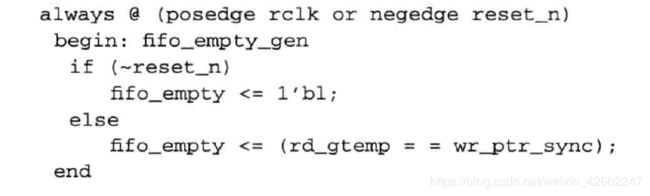

在读clk下判定FIFO空,当同步后的写指针和下一个读指针相同时(rd_gtemp = rd_inr为rd_addr+1)

根据格雷码特性,4bit格雷码的上面8个和下面8个的MSB位相反,次MSB位呈相反,LSB的两位完全相同,据此,判定FIFO满为真的判定条件如下:

首先,理论上来讲,FIFO满时的情况,写指针应该比读指针大FIFO深度的距离,这里也就是8。

因此满FIFO的第一个条件就是读写指针的MSB位不同,为了继续判定双方差距是否够8(即满条件),判定次MSB位,下一个写指针应该与当前读指针取反的数相同(实际操作是将两个MSB位异或,判定是否一致,原理参见表3.3,4bit-Gary码转3bit-Gary码后,高位一致),再判定剩下的两个LSB位,应该相同。

此时,FIFO为满。