AMBA总线—APB总线协议详解

文章目录

- 一、APB总线介绍

- 1.1.什么是APB总线

- 1.2.典型的基于 AMBA 总线的系统架构

- 1.3.APB信号列表(重点)

- 二、APB总线传输(时序)

- 2.1.APB 状态机

- 2.2.写操作(重要)

- 2.3.读操作(重要)

- 2.4.APB模块接口(重要)

- 2.4.1.APB Bridge框图

- 2.4.2.APB Slave框图

- 三、APB到AHB的接口

- 3.1.读操作

- 3.2.写操作

- 3.3.读写交替传送

一、APB总线介绍

关于总线的一些概念:

总线:计算机内部和计算机之间传输数据的共用通道。

总线位宽:总线能够一次性传送的二进制数据位数,例如8bit、16bit、32bit、64bit等。

总线工作频率:即时钟频率(时钟是系统的心脏)。

总线带宽:总线数据的传输速率(单位时间内,总线上传送的数据量。即每秒钟传送MB的最大稳态数据传输率)。

1.1.什么是APB总线

APB的全称:Advanced Peripheral Bus,即先进外设接口 。AMBA 中的 APB 总线主要用在低速且低功率消耗的外围,在 APB 总线中,唯一的 M 为 APB bridge,其它一些低速和低功率的外围皆为 S。因此 APB 总线不需要有一个像 AHB 一样的仲裁器及其它复杂的线路,也就是说 APB 总线的整个架构较 AHB 简单许多。

为了使APB容易被整合进大部分的设计流程中, APB规订所有信号必须在时钟上升沿触发时进行传递。

通常APB总线的组成可看做是由APB Bridge和APB上的从设备两部分组成。

- APB Bridge可以所存总线所有地址、数据和控制信号;并进行二级译码来产生APB从设备选择信号。

- APB上所有的其他模块都是APB从设备。

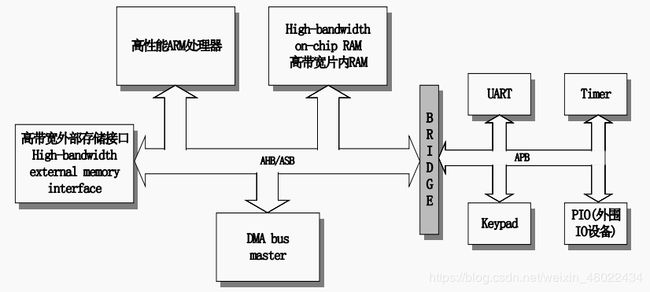

1.2.典型的基于 AMBA 总线的系统架构

APB 总线是 AHB 或者 ASB 系统总线的扩展,便于外设链接到系统总线上。AHB 和 APB 之间有一条桥来链接。

1.3.APB信号列表(重点)

由上表可以看出,APB信号主要有系统信号(PCLK、PRESETn)、地址信号(PADDR[31:0])、方向信号(PWRITE)、数据信号(WDATA[31:0]、PRDATA[31:0])和传输阶段控制信号(PSELx、PENABLE)五部分组成。

二、APB总线传输(时序)

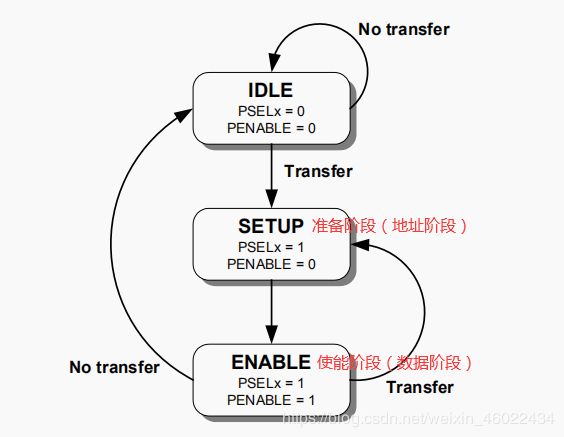

2.1.APB 状态机

从状态机看,APB对每一笔数据的传送,均需花 2 个周期的时间,且 APB 的数据传递不适用在有流水线架构的模块设计中。

2.2.写操作(重要)

在 T1 时,有限状态机进入预设的 IDLE 状态;

在 T2 时,数据地址、读写控制信号和写入的数据会在频率正沿触发时,开始作写的数据传递准备,这个周期也就是刚才所提及SETUP状态。译码电路在此状态会根据数据地址去译码出所要写入APB Slave,此时所对应到 S 的 PSEL 信号将由 0 变 1;

在 T3 时,有限状态机会进入 ENABLE 状态,PENABLE 信号在此状态会被设成 1;

在 T4 频率正沿触发时,PENABLE 信号将由 1 变 0,而 PSEL 信号在若没有其它数据的写入动作时,也将由 1 变 0。为了减少功率的消耗,APB 的数据地址和读写控制信号在下一笔数据传递前,将不会作任何改变。

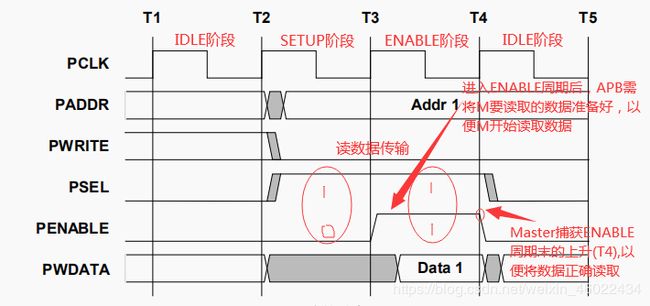

2.3.读操作(重要)

由图中可发现除了写信号是倒过来有效外,APB 读操作时序图和写操作时序图非常相似,在这里我们就不再作详细的解释。

要特别注意的是,在 T3 后,也就是在进入 ENABLE 周期后,APB 从必须要将 M 所要读取的数据准备好,以便 M 可以在 ENABLE 周期末被 T4 正时钟沿触发时正确的将数据读取。

2.4.APB模块接口(重要)

上文中已经提到,APB由APB Bridge和APB上的从设备两部分组成。

2.4.1.APB Bridge框图

APB桥为AHB的一个从设备,但它在APB中是唯一的主设备,而APB中其它低速和低功率消耗的外围皆为APB桥的从设备。下图是 APB 桥的信号接口:

APB桥将系统总线传送转换成APB方式的传送,它具备一些这些功能:

- 锁存地址,在传送过程中保持地址有效。锁存读写控制信号

- 对锁存的地址进行译码并产生选择信号PSELx,在传送过程中只有一个选择信号可以被激活。也就是选择出唯一一个APB从设备以进行读写动作.

- 写操作时: 负责将AHB送来的数据送上APB总线。

- 读操作时: 负责将APB的数据送上AHB系统总线。

- 产生一时序选通信号PENABLE作为数据传递时的启动信号

关于APB Bridge的时序图在此不做详述。

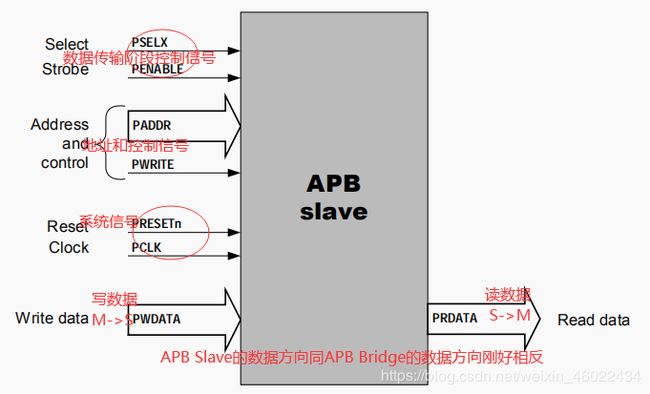

2.4.2.APB Slave框图

如前面所提及,APB 总线中除了 APB bridge 为 M 外,其它的外围皆为 S。因此,APB 从设备比 AHB从设备接口较为简单且非常具弹性: 例如

a. APB 少了仲裁器及复杂的译码电路,APB 进行写操作时,从设备可以决定:

: 在 PCLK 上升沿触发, 且 PSEL 为高时锁存数据

:或在 PENABLE 上升沿, 且 PSEL 为高时锁存数据

b. PSELx,PADDR和PWRITE信号的组合可以决定哪个寄存器会被写操作更新。

c. 在读操作的时候,数据可以 PWRITE 在=0,PSELx 和 PENABLE=1 的时候被送到总线上,而PADDR 用于决定哪个寄存器会被读。

三、APB到AHB的接口

3.1.读操作

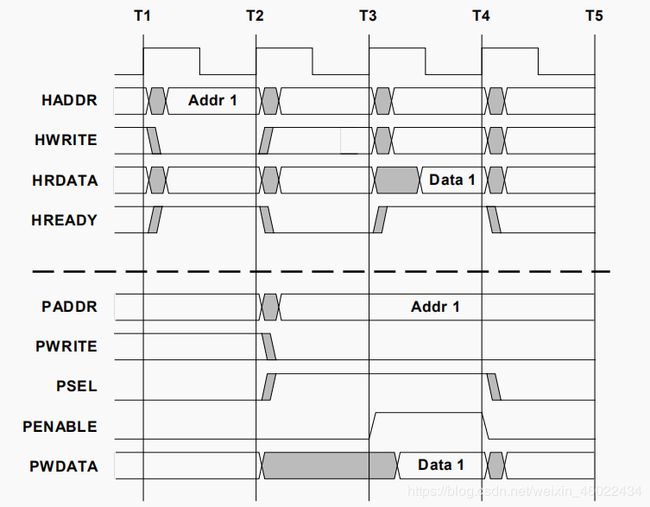

在频率很高的情况下,在ENABLE CYCLE中可能数据不能够直接映射到AHB总线,需要在APB桥中在T4的时候打一下锁住,并在T5的时候才被AHB主采样。虽然需要多一个等待周期(一共2个,HREADY反压两拍),但是由于频率提升了因此总的性能也提升了。

T1:在 AHB 总线开始传送;

T2:地址被 APB 总线采样。如果该传送是针对外设的话,这个地址就会被译码成选择信号发往外设。T2就是 AHB 的SETUP CYCLE。

T3:APB 的 ENALBE CYCLE,PENABLE 拉高,数据被读出。

T4:读出的数据直接映射到 AHB 总线上,在上升沿被 AHB 主采样。

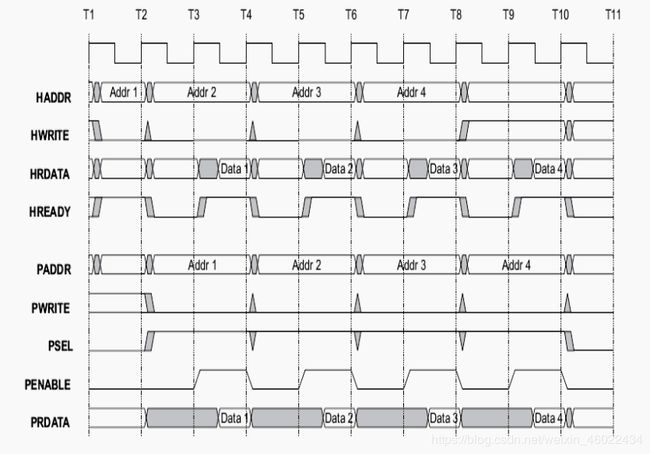

下图是批量读操作(非高频),每一组数据都只需要一个等待周期:

3.2.写操作

以下进一步说明 AHB 和 APB 之间数据传递的情形, 如图 所示:

APB总线上的单块数据写操作不需要等待周期。APB桥的责任是对地址和数据进行采样,并在写操作的过程中保持它们的值。

T1:AHB 开始作数据地址和读写控制信号的传递(HADDR 和 HWRITE)

T2:APB bridge 栓取住 AHB 送来的数据地址及读写控制信号,同时进入到 APB 有限状态机的 ENABLE状态

T3~:其后的读和写动作跟之前所介绍的 APB 读写动作一模一样,在这里我们不再加以详述。

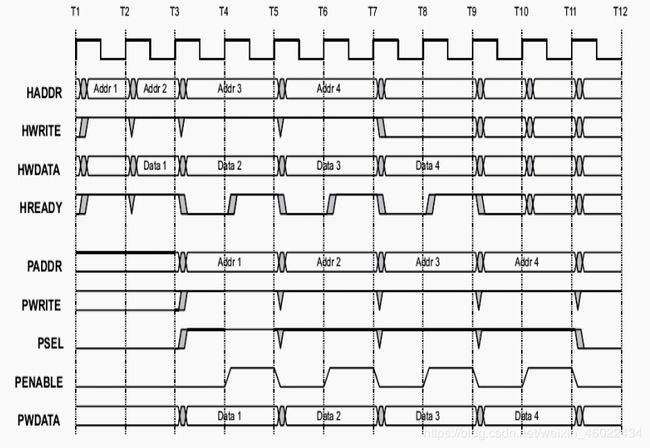

下图是批量写操作的图:

当批量写操作的时候,第一块数据不需要等待周期,之后的每一块数据都需要一个等待周期。 APB桥中需要有 2 个地址寄存器,当处理一个数据块写操作时,可以寄存下一个数据块的地址。

3.3.读写交替传送

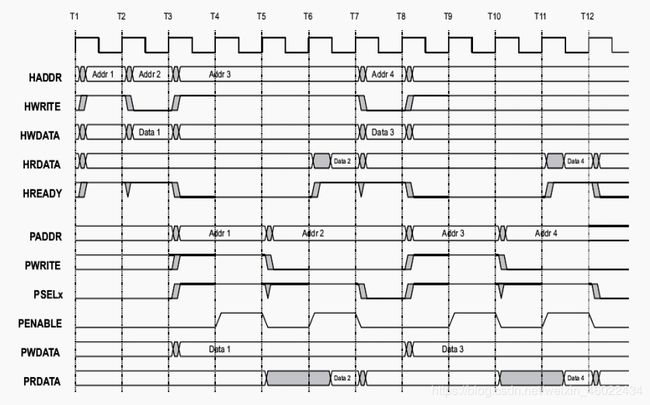

下图画出了读写交替传送的时序,先是写,再读,再写,再读。

如果写操作之后跟随着读操作,那么需要 3 个等待周期来完成读操作。通常的情况下,不会有读操作之后紧跟着写操作的发生,因为两者之间 CPU 会进行指令读取。