Vivado_IDE(2)使用Vivado进行工程设计综合【上】

(2)使用Vivado进行工程设计综合【上】

作者:毛茏玮 / Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

知乎:https://www.zhihu.com/people/saint-80-61/columns

2.1编译仿真库

Vivado支持第三方仿真工具,如ModelSim或者QuetaSim,例如ModelSim仿真工具,我们要对Xilinx自带的库文件进行仿真,确保后续工程出现问题不是因为库文件的兼容问题所导致的,同时保证当设计包含Xilinx IP时,ModelSim能够识别出来。

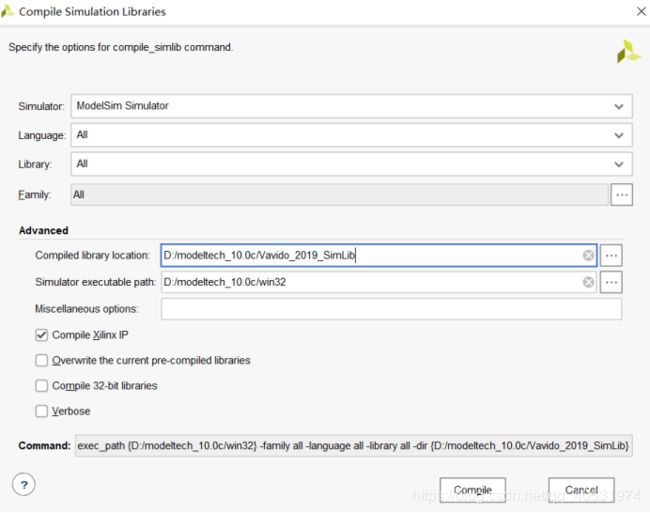

1)新建仿真库,一般设置在ModelSim的安装目录下,即直接新建一个空的文件夹,路径如:D:/modeltech_10.0c/Vavido_2019_SimLib。

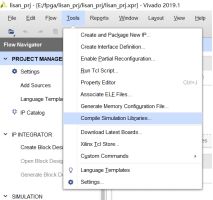

2)点击菜单中的Tools->Compile Simulation Libraries

3)在弹出的对话框中,Simulatior选择ModelSim,Compile Libraries path选择步骤1建立的空文件夹路径,这是仿真完自带的库后的文件存储的位置,Simulatior executable path选择ModelSim可执行文件的目录,如D:/modeltech_10.0c/win32,其余选项默认既可。

4)点击compile。

2.2逻辑综合

2.2.1运行综合

软件窗口左侧Flow Navigator上单击Synthesis->Run Synthesis,在Message窗口的Design Runs会显示综合的进度。逻辑综合设计下有很多选项,这些对应不同的功能,比如约束文件向导,时钟约束,设置debug,生成静态时序报告总结,时钟网报告等,此处需重点掌握Report Timing Summary,在后面三种工况下静态时序分析测试时会用到。

Open Synthesized Design下有11个功能,以下将以此介绍不同的功能

1)Constraints Wizard:约束向导,向导会自动帮你生成XDC文件,而这个文件就是约束文件,约束文件也可以自己编写代码,同时在新建工程时定义各引脚时就会自动关联XDC文件,在综合阶段可以不加激励,仿真添加测试。

2)Edit Timing Constraints:添加时钟约束文件,只需要在Timing Constraints中选择对应的约束类型,右键新建一个类型,然后自定义设置参数既可添加到XDC文件中形成完整的约束文件。例如:在Timing Constraints中选择Create Clock,右键新建一个周期为1Mhz时钟脉冲。

Add Clock勾选,点击Apply,点击保存,系统提示约束文件过期需要更新,选中OK,双击XDC文件,点击Reload重新更新约束文件,再次进入XDC文件,文件已更新了时钟约束文件。

此外可以知道Timing Constraints可以增加6种类别的时钟约束:时钟、输入约束、输出约束、数据交互约束、异常情况约束、其他约束:case语句,总文件路径等。

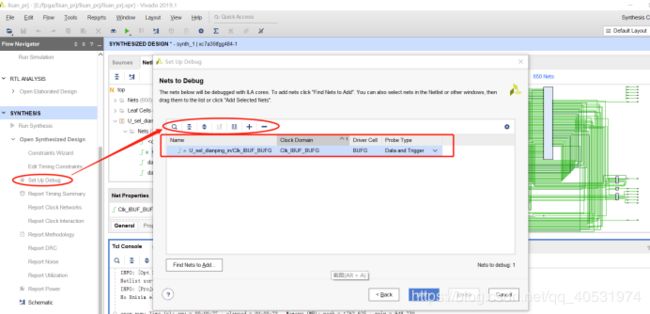

3)Set up Debug设置Debug参数:Vivado提供多种Debug的方式,现在只介绍通过网表标记Debug的方法,后期会在Vivado专栏剖析各项功能,大家可以关注我其他的blog。

当我们工程进行逻辑综合后,生成网表,选择某个线网络右击,在网表中设置Debug:Mark Debug,其实就等于选择了需要debug的信号。例如:Clk_IBUF_BUFG信号,TCL console显示:set_property mark_debug true [get_nets [list U_sel_dianping_in/Clk_IBUF_BUFG]]

然后在综合设置里设置Debug参数:根据向导,选择需要Debug的信号,设置时钟域以及触发方式等,选择ILA IP核采样深度。

然后,重新综合,实现生成bit流文件即可完成debug。

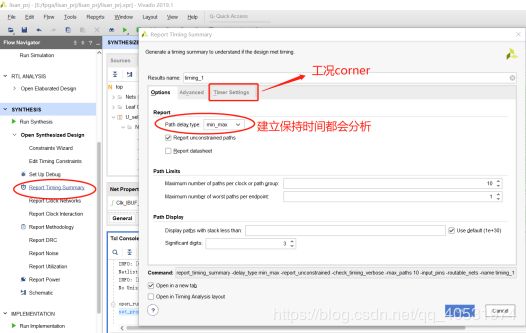

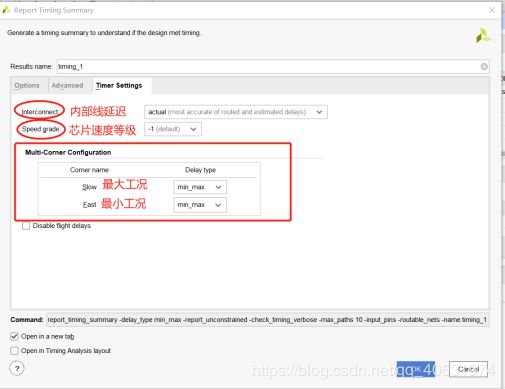

4)Report Timing Summary,时钟网络分析

A、单击report timing summary,在弹出界面options中的Path delay type有3个可选值,分别为min、max、min_max,通常选择min_max,,这是因为min对应保持时间,max对应建立时间,min_max表示建立时间和保持时间都会分析。

B、Timing Settings界面中,Interconnect有三个可选值,分别为actual,estimated和none。通常选择actual,表示线延迟会足够的精确,接近布局布线后的真实线延迟。有时也会选择none,说明线延迟为0,可以快速报告出逻辑延迟较大的路径,注意:如果此种情况下仍出现时序违例,那就说明需要对组合逻辑优化以减小组合逻辑延迟。

C、Timing Settings界面中,Speed Grade为芯片速度等级,如果需要尝试当前设计能否在其他速度等级下实现时序收敛,只需在此处切换芯片速度等级既可,而无需重新创建工程。

D、Timing Settings界面中,corner name有Slow最大工况,Fast最小工况之分,有min、max、min_max以及none四种方式可以选择。

实际上我们需要了解工况的概念,其实可以理解为在不同的工作环境下测试器件的静态时序。而工况一般分为三种:最大工况:最大温度,最小电压;典型工况:平均温度,平均电压;最小工况:最小温度,最大电压。做静态测试时需要对建立保持时间进行三工况的仿真,看FPGA在三种不同工况下的建立保持时间是否都大于0。建立保持时间是时序分析的一项很重要指标。Vivado里面对最大工况的约束是Slow最大工况选择min延迟,Fast最小工况选择max延迟;对最大工况的约束是Slow最大工况选择max延迟,Fast最小工况选择min延迟;典型工况的约束是Slow最大工况选择max_min延迟,Fast最小工况选择max_min延迟。

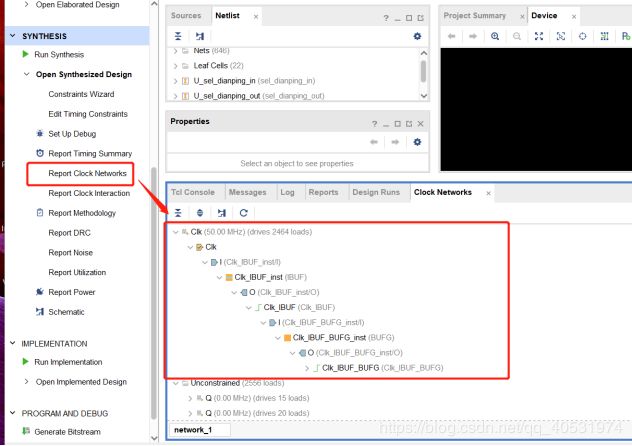

5)时序不满足约束会出现以下问题:编译时间极长、运行结果不稳定。report_clock_networks时钟网络分析反应了时钟引脚进入FPGA后在FPGA内部的传播路径。

报告时钟网络提供设计中时钟树的树视图。每个时钟树显示从源到端点的时钟网络,端点按类型排序。

时钟树:

显示由用户定义或由工具自动生成的时钟。

报告从I / O端口加载的时钟。

可用于查找驱动其他BUFGs的BUFGs。

显示驱动非时钟负载的时钟。

时钟Clk从输入引脚输入之后,经过IBUF,再通过BUFG生成时钟。如果我们未添加时钟约束,报告将显示Unconstrained(未约束的时钟,root clock).可以选中未约束的时钟右击选择Create Clock创建时钟。

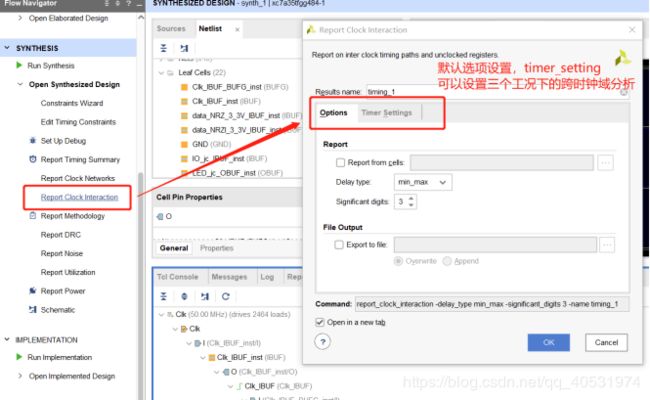

6)Report Clock Interaction跨时钟域路径分析

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。跨时钟域路径分析报告有助于识别可能存在数据丢失或亚稳态问题的情况。跨时钟域是安全测试中的一项重要指标。

时钟交互报告显示如下:

① No Path --用黑色框来表示:没有从源时钟到目标时钟的定时路径。在这种情况下,没有时钟交互,也没有任何报告。

② Timed – 用绿色框来表示:源时钟和目标时钟具有同步关系,并安全地被约束在一起。当两个时钟具有共同的主时钟和简单的周期比时,该状态由定时引擎确定。

③ User Ignored Paths–用深蓝色框来表示:用户定义的假路径或时钟组约束涵盖从源时钟到目标时钟的所有路径。

④ Partial False Path–用淡蓝色框来表示:用户定义的伪路径约束覆盖了从源时钟到目标时钟的一些时序路径,其中源时钟和目标时钟具有同步关系。

⑤ Timed (Unsafe)–用红色框来表示:源时钟和目标时钟具有异步关系。在这种情况下,没有共同的主时钟或没有可扩展的时段。

⑥ Partial False Path (Unsafe)–用橘橙色框来表示:此类别与Timed(Unsafe)相同,只是由于伪路径异常,从源时钟到目标时钟的至少一条路径被忽略。

⑦ Max Delay Datapath Only --用紫色框来表示:set_max_delay -datapath_only约束涵盖从源时钟到目标时钟的所有路径。

Report_clock_interaction呈现的报告并不是根据时序约束生成的,但是和时序约束有关,它反映出用户定义的伪路径,我们可以查看报告中的表格。

① Source Clock: 路径源时钟域。

② Destination Clock: 路径终端的时钟域。

③ Edges (WNS):用于计算最大延迟分析(设置/恢复)的最差裕度的时钟边缘。

④ WNS (Worst Negative Slack):为跨越指定时钟域的各种路径计算的最差裕度时间。负裕量时间表示路径违反了所需的建立(或恢复)时间的问题–这个是建立保持时间,之前我们提到了静态仿真的重要指标就是建立保持时间满不满足>0的情况。

⑤ TNS (Total Negative Slack):属于跨越指定时钟域的路径的所有端点的最差松弛违规的总和。

⑥ Failing Endpoints (TNS): 交叉路径中的端点数量无法满足时序要求。违规的总和对应于TNS。

⑦ Total Endpoints (TNS):交叉路径中端点的总数。

⑧ Path Req (WNS):定时路径要求对应于WNS列中报告的路径。如果两个时钟中的至少一个时钟的上升沿和下降沿都有效,则在任何时钟对之间可能存在若干路径要求,或者在两个时钟之间的路径上应用了一些时序异常。

⑨ Clock Pair Classification: 提供有关公共节点和时钟对之间的公共周期的信息。从最高优先级到最低优先级:忽略,虚拟时钟,无公共时钟,无公共周期,部分公共节点,无公共节点和清除。

⑩ Inter-Clock Constraints: 显示源时钟和目标时钟之间所有路径的约束摘要。

上述10条中,其实只需要关心WNS、WHS,因此我们在后面将更新一篇讨论如何增加建立保持时间使得其静态测试符合标准的博客,大家有兴趣的可以关注一下。其他的参数可以作为判断是否存在数据丢失或亚稳态问题的问题,结合实际程序去证明程序的稳定性和可靠性。