计算机组成原理 课后作业2(第4章)

一.填空题

1 .Cache、主存、和 辅存 组成三级存储器系统,分级的目的是 提高访存速度,扩大存储容量 。

2.半导体静态RAM依据 触发器原理 存储信息,半导体动态RAM依据 电容存储电荷原理 存储信息。

3.动态半导体存储器的刷新一般有 集中刷新 、分散刷新 和 异步刷新 三种方式,之所以刷新是因为 存储电荷的电容放电 。

4.半导体静态RAM进行读写操作时,必须先接受 地址 信号,再接受 片选 和 读写 信号。

5.欲组成一个64K×16位的存储器,当分别选用32K×8位,16K×1位,1K×4位的三种不同规格的存储芯片时,各需 4 、 64 和 256 片。

6. 用1K×4位的存储芯片组成容量为64K×8位的存储器,共需 128 片,若将这些芯片分装在几块板上,设每块板的容量为16K×8位,则该存储器所需的地址线总位数是 16 ,其中 2 位用于选板, 4 位用于选片, 10 位用于存储芯片的片内地址。

7. 使用高速缓冲存储器是为了解决 CPU和主存的速度匹配问题提高访存速度 ,使用虚拟存储器是为了解决 扩大存储器容量 问题。

8. 由容量为16KB的缓存和容量为16MB的主存构成的存储器系统的总容量为 16MB。

9. 高位交叉编址的存储器能够提高访存速度的原因是 各个体分别响应不同请求源的请求实现多体并行 ,其地址的高位部分用于 选择体号 ,地位部分用于 选择存储体内的字 。

10.低位交叉编址的存储器能够提高访存速度的原因是 不改变每个体的存取周期的前提下增加存储器的带宽 ,其地址的高位部分用于 选择存储体内的字 ,地位部分用于 选择体号 。

二.简答题

1.试比较静态RAM和动态RAM。

动态RAM集成度高、功耗低、价格低。但由于它是以电容上的电荷存储信息的,必须定时刷新,所以接口电路比较复杂。

静态RAM速度快,但由于用双稳电路存储信息,集成度较低、功耗较大、成本较高。

2.什么叫刷新?为什么要刷新?说明刷新有几种方法。

刷新:对DRAM定期进行的全部重写过程:

刷新原因:因电容泄漏而引起的DRAM所存信息的衰减需要及时补充,因此安排

了定期刷新操作:

常用的刷新方法有三种:集中式、分散式、异步式。

集中式:在最大刷新间隔时间内,集中安排一段时间进行刷新,存在CPU访存死

时间。

分散式:在每个读/写周期之后插入一个刷新周期,无CPU访存死时间。

异步式:是集中式和分散式的折衷。

3.计算机中设置Cache的作用是什么?能否将Cache的容量扩大,最后取代主存,为什么?

计算机中设置Cache的作用是解决CPU和主存速度不匹配问题。

不能将Cache的容量扩大取代主存,原因是:

(1)Cache容量越大成本越高,难以满足人们追求低价格的要求;

(2)如果取消主存,当CPU访问Cache失败时,需要将辅存的内容调入Cache再由CPU访问,造成CPU等待时间太长,损失更大。

4.简要说明提高访存速度可采取的措施。

提高访存速度可采取三种措施。

(1)采用高速器件选用存取周期短的芯片可提高存储器的速度。

(2)采用CacheCPU将最近期要用的信息先调入Cache而Cache的速度比主存快得多这样CPU每次只需从Cache中取出(或存入)信息从而缩短了访存时间提高了访存速度。

(3)调整主存结构如采用单体多字结构(在一个存取周期内读出多个存储字可增加存储器的带宽)或采用多体结构存储器。

三.计算题

1.已知收到的汉明码(按配偶原则配置)为1100100、1100111、1100000、1100001,检查上述代码是否出错?第几位出错?

假设接收到的汉明码为:c1’c2’b4’c3’b3’b2’b1’

纠错过程如下:

P1=c1’⊕b4’⊕b3’⊕b1’

P2=c2’⊕b4’⊕b2’⊕b1’

P3=c3’⊕b3’⊕b2’⊕b1’

如果收到的汉明码为1100100,则p3p2p1=011,说明代码有错,第3位(b4’)出错,有效信息为:1100

如果收到的汉明码为1100111,则p3p2p1=111,说明代码有错,第7位(b1’)出错,有效信息为:0110

如果收到的汉明码为1100000,则p3p2p1=110,说明代码有错,第6位(b2’)出错,有效信息为:0010

如果收到的汉明码为1100001,则p3p2p1=001,说明代码有错,第1位(c1’)出错,有效信息为:0001

2.假设CPU执行某段程序时共访问Cache命中4800次,访问主存200次,已知Cache的存取周期为30ns,主存的存取周期为150ns,求Cache的命中率以及Cache-主存系统的平均访问时间和效率,试问该系统的性能提高了多少倍?

Cache被访问命中率为:4800/(4800+200)=24/25=96%

则Cache-主存系统的平均访问时间为:ta=0.96*30ns+(1-0.96)*150ns=34.8ns

Cache-主存系统的访问效率为:e=tc/ta100%=30/34.8100%=86.2%

性能为原来的150ns/34.8ns=4.31倍,即提高了3.31倍。

3.设主存容量为256K字,Cache容量为2K字,块长为4。

(1)设计Cache地址格式,Cache中可装入多少块数据?

(2)在直接映射方式下,设计主存地址格式。

(3)在四路组相联映射方式下,设计主存地址格式。

(4)在全相联映射方式下,设计主存地址格式。

(5)若存储字长为32位,存储器按字节寻址,写出上述三种映射方式下主存的地址格式。

(1)Cache容量为2K字,块长为4,Cache共有2K/4=211/22=29=512块,

Cache字地址9位,字块内地址为2位

因此,Cache地址格式设计如下:

Cache字块地址(9位)

字块内地址(2位)

(2)主存容量为256K字=218字,主存地址共18位,共分256K/4=216块

主存字块标记为18-9-2=7位。

直接映射方式下主存地址格式如下:

主存字块标记(7位)

Cache字块地址(9位)

字块内地址(2位)

(3)根据四路组相联的条件,一组内共有4块,得Cache共分为512/4=128=27组,

主存字块标记为18-7-2=9位,主存地址格式设计如下:

主存字块标记(9位)

组地址(7位)

字块内地址(2位)

(4)在全相联映射方式下,主存字块标记为18-2=16位,其地址格式如下:

主存字块标记(16位)

字块内地址(2位)

(5)若存储字长为32位,存储器按字节寻址,则主存容量为256K*32/4=220B,

Cache容量为2K32/4=214B,块长为432/8=16B,字块内地址为4位,

在直接映射方式下,主存字块标记为21-9-5=7位,主存地址格式为:

主存字块标记(7位)

Cache字块地址(9位)

字块内地址(4位)

在四路组相联映射方式下,主存字块标记为21-7-4=9位,主存地址格式为:

主存字块标记(9位)

组地址(7位)

字块内地址(4位)

在全相联映射方式下,主存字块标记为20-4=16位,主存地址格式为:

主存字块标记(16位)

字块内地址(4位)

4.某8位微型机地址码为18位,若使用4K×4位的RAM芯片组成模块板结构的存储器,试问:

(1)该机所允许的最大主存空间是多少?

(2)若每个模块板为32K×8位,共需几个模块板?

(3)每个模块板内共有几片RAM芯片?

(4)共有多少片RAM?

(5)CPU如何选择各模块板?

(1)该机所允许的最大主存空间是:218 × 8位 = 256K×8位 = 256KB

(2)模块板总数 = 256K×8 / 32K×8 = 8块

(3)板内片数 = 32K×8位 / 4K×4位 = 8×2 = 16片

(4)总片数 = 16片×8 = 128片

(5)CPU通过最高3位地址译码输出选择模板,次高3位地址译码输出选择芯片。地址格式分配如下:

![]()

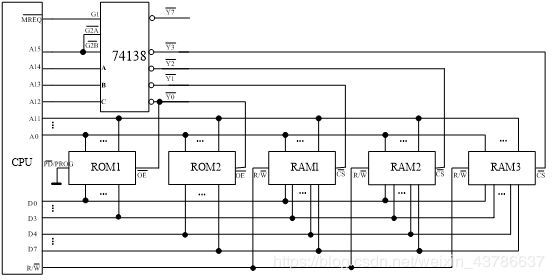

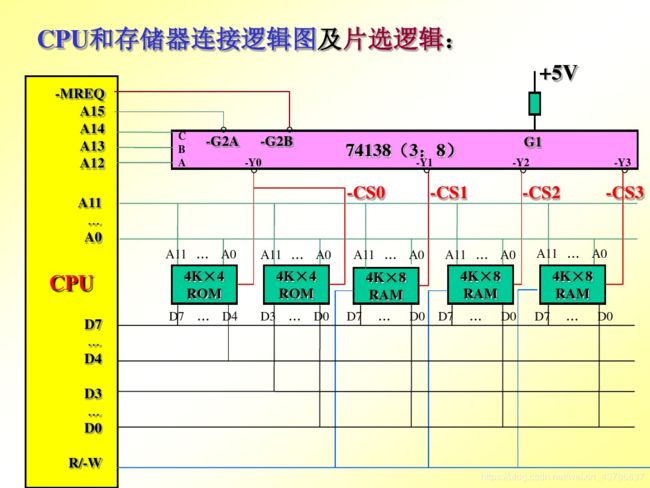

5.设CPU共有16根地址线,8根数据线,并用MREQ(低电平有效)作访存控制信号,R/W作读写命令信号(高电平为读,低电平为写)。

现有下列存储芯片:ROM(2K×8位,4K×4位,8K×8位),RAM(1K×4位,2K×8位,4K×8位),及74138译码器和其他门电路(门电路自定)。试从上述规格中选用合适芯片,画出CPU和存储芯片的连接图。要求:

(1)最小4K地址为系统程序区,4096~16383地址范围为用户程序区。

(2)指出选用的存储芯片类型及数量。

(3)详细画出片选逻辑。

第一步,根据题目的地址范围写出相应的二进制地址码。

A15… A12A1 … AgA7 … AgA3 … Ao

0000000000000000

最小4KX 8位系统程序区

0000111111111111

0001000000000000

相邻12KX 8位用户程序区

0011111111111111

第二步,根据地址范围的容量及其在计算机系统中的作用,确定最小

4KB最小系统程序区选择2片4K X 4位ROM;与其相邻的12KB用户程

序区选择3片4K X 8位RAM。

第三步,分配CPU地址线

将CPU的低12位地址线A11~A0与2片4K X 4位ROM和3片4K X 8位

RAM的地址线相连。

第四步,形成片选信号。

将74138译码器的控制端G1接+5V, -G2A,-G2B分 别接A15和-MREQ.

CPU的A14.A13,A12分别接在译码器的C.B,A端。-Y0作为并联的

两片ROM的片选信号,-Y1,-Y2,-Y3分 别作为串联的3片RAM的片选信

号。

6.设CPU共有16根地址线,8根数据线,并用MREQ(低电平有效)作访存控制信号,R/W作读写命令信号(高电平为读,低电平为写)。现有8片8K×8位的RAM芯片与CPU相连,试回答:

(1)用74138译码器画出CPU与存储芯片的连接图;

(2)写出每片RAM的地址范围;

(3)如果运行时发现不论往哪片RAM写入数据后,以A000H为起始地址的存储芯片都有与其相同的数据,分析故障原因。

(4)根据(1)的连接图,若出现地址线A13与CPU断线,并搭接到高电平上,将出现什么后果?

(1)

(2)地址空间分配图:

RAM0:0000H-1FFFH

RAM1:2000H-3FFFH

RAM2:4000H-5FFFH

RAM3:6000H-7FFFH

RAM4:8000H-9FFFH

RAM5:A000H-BFFFH

RAM6:C000H-DFFFH

RAM7:E000H-FFFFH

(3)如果运行时发现不论往哪片RAM写入数据后,以A000H为起始地址的存储

芯片(RAM5)都有与其相同的数据,则根本的故障原因为:该存储芯片的片选输入

端很可能总是处于低电平。假设芯片与译码器本身都是好的,可能的情况有:

1)该片的CS端与WE端错连或短路:

2)该片的CS端与CPU的MREQ端错连或短路:

3)该片的CS端与地线错连或短路。

(4)如果地址线A13与CPU断线,并搭接到高电平上,将会出现A13恒为“1”

的情况。此时存储器只能寻址A13=1的地址空间(奇数片),A13=0的另一半地址

空间(偶数片)将永远访问不到。若对A13=0的地址空间(偶数片)进行访问,

只能错误地访问到A13=1的对应空间(奇数片)中去。