数字电子技术之逻辑门电路

逻辑门电路是指用于实现各种各样的基本逻辑运算、常用复合逻辑运算的电子电路,简称门电路。

这部分的内容也是数字电子技术比较难的内容,按集成度划分,可分为分立元件门电路和数字集成电路:

- 分立元件门电路:用若干分立的半导体器件和电阻、电容等元件连接形成。

- 数字集成电路:将大量的分立元件和门电路单元集成在一块很小的半导体基片上,形成一个微缩化的 “片上系统”

目前,应用最广泛的集成门电路有CMOS和TTL两大类:

- TTL集成逻辑门: 功耗较大,不适于制造大规模、超大规模集成电路。

- CMOS集成逻辑门:功耗非常低,发热量小,易于集成。

下面是本篇文章的结构:

- 逻辑门电路概述

- 分立元件门电路

- 数字集成电路

- 多余输入端的处理

1. 逻辑门电路概述

正逻辑和负逻辑

- 基本的逻辑规定: 1 - "真”; 0 - “假”

在实际中,不可能直接输入0和1,因此引入了正逻辑和负逻辑:

- 正逻辑和负逻辑:在实际的数字系统中,用数字信号(逻辑电平Ui、Uo)

表示"真(1)"、"假(0)"的约定。

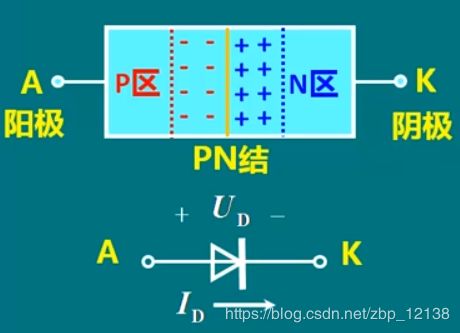

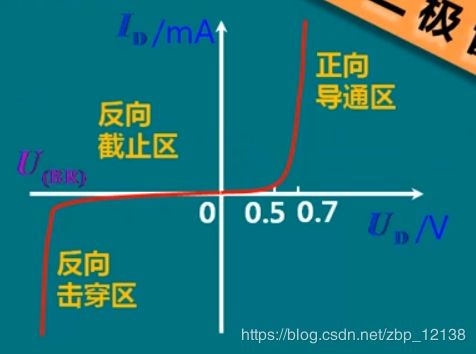

二极管和晶体管的基本特性

二极管

- 外加正向电压(正偏) :二极管导通 Un≈0.7 V

- 外加反向电压(反偏) :二极管截止 Un <0.5V, In≈0

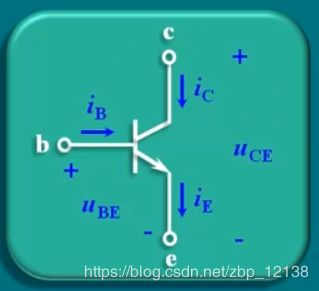

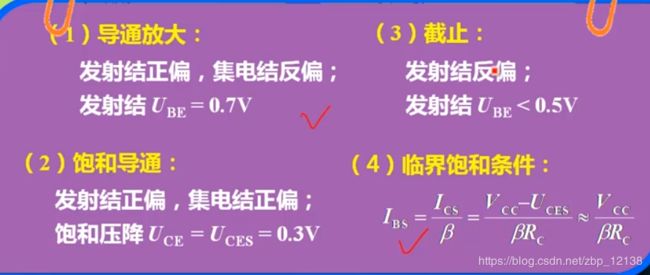

晶体管(三极管)

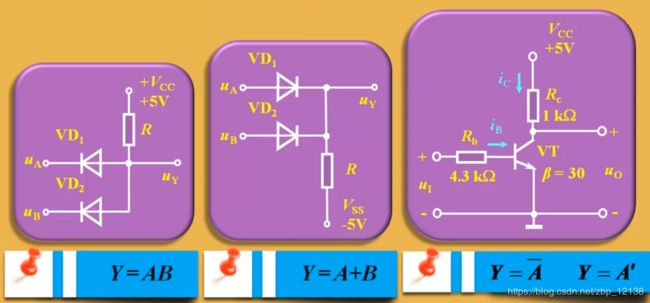

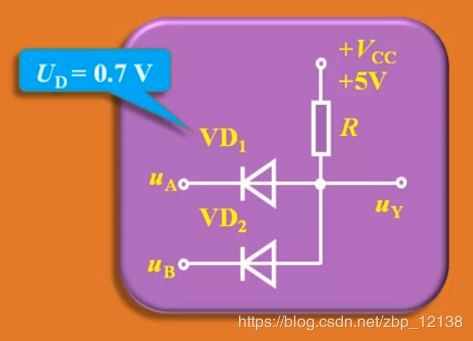

2. 分立元件门电路

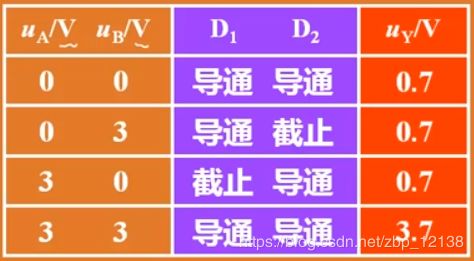

二极管与门

- 0 - 0.7V表示低电平

- 0.7 - 3.7V表示高电平

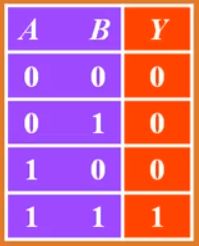

完成了两输入与的功能

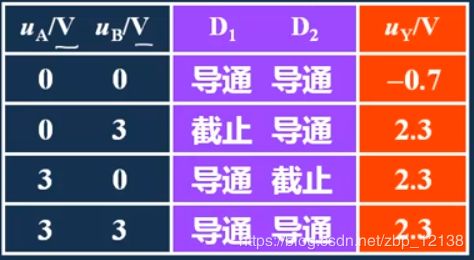

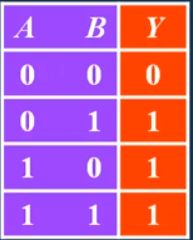

二极管或门

这里的电压源变成了负数(方便计算):

根据正逻辑转换成真值表:

根据正逻辑转换成真值表:

- -0.7 - 0V表示低电平

- 2.3 - 3V表示高电平

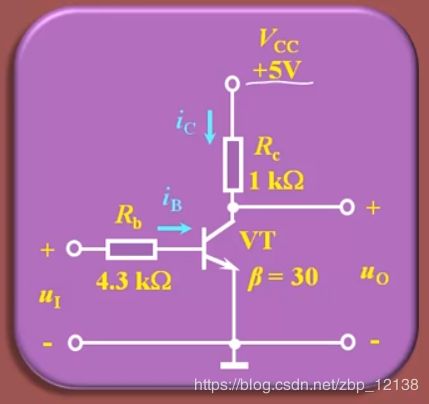

晶体管非门

3. 数字集成电路

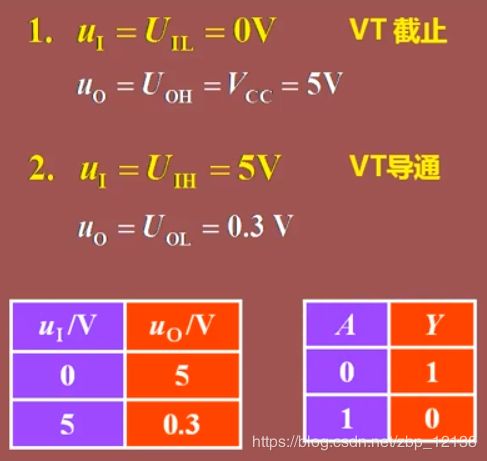

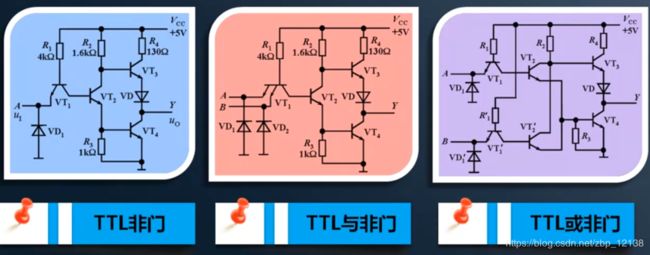

TTL逻辑门

TTL集成电路:

晶体管-晶体管逻辑电路( Transistor- Transistor Logic )

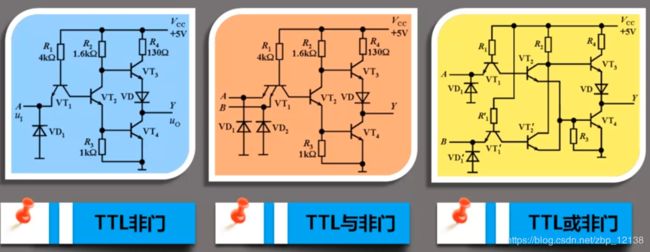

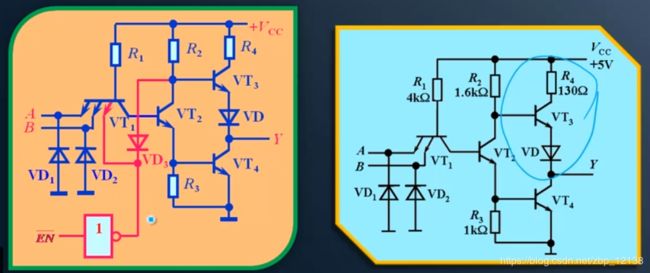

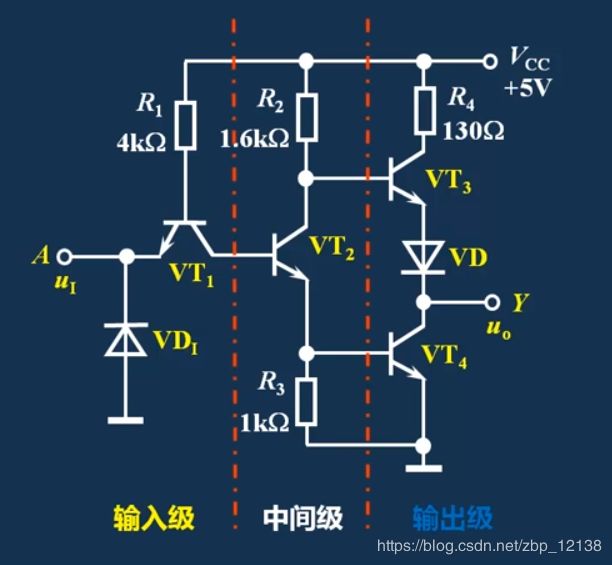

TTL非门

电路结构

输入极有一个二极管,是用来防止输入电压过低,即防止出现大电流的:

输入极有一个二极管,是用来防止输入电压过低,即防止出现大电流的:

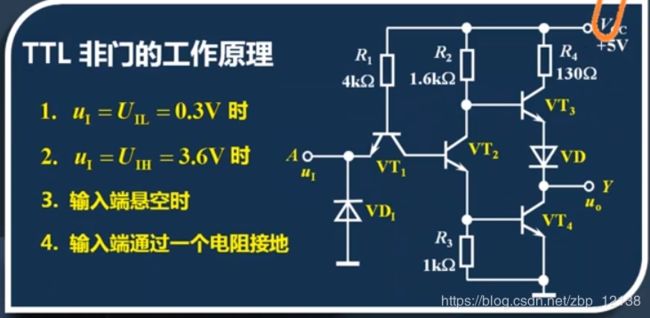

工作模式

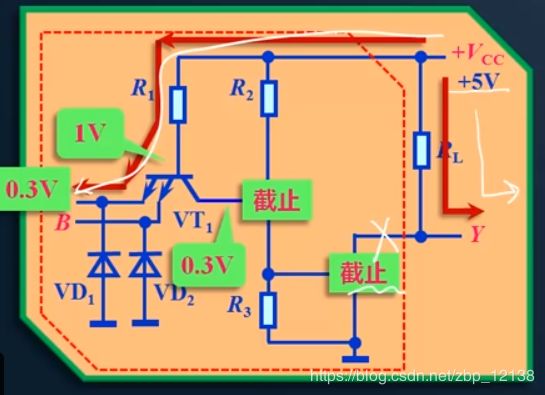

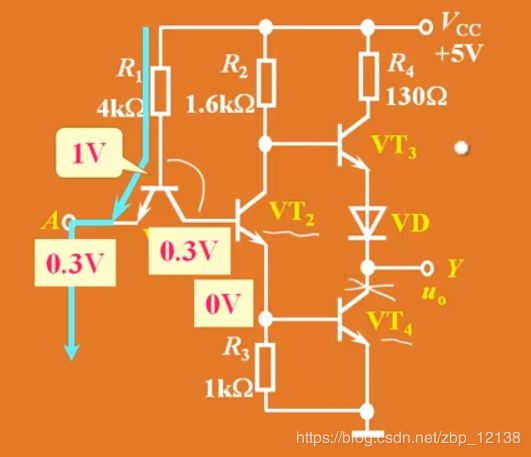

- ui =UiL=0.3V时

- ui=UiH= 3.6V时

- 输入端悬空时

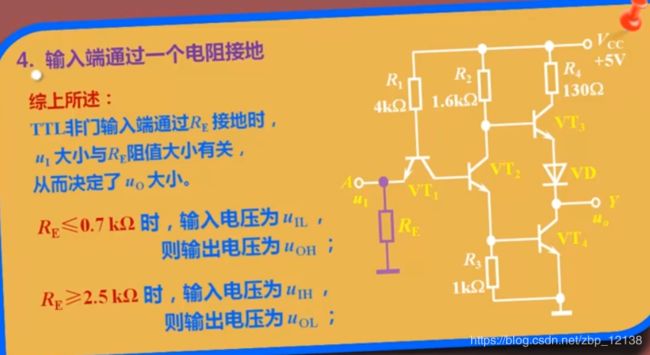

- 输入端通过一个电阻接地

输入电压为输入低电平时

先看最外围的回路:

VT1的基极电压无法使VT2和VT4的发射结导通

接下来再看下一个回路:

完全可以突破两个PN结到达输出,为3.6V

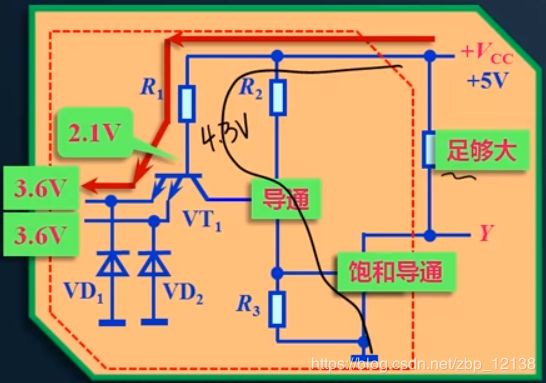

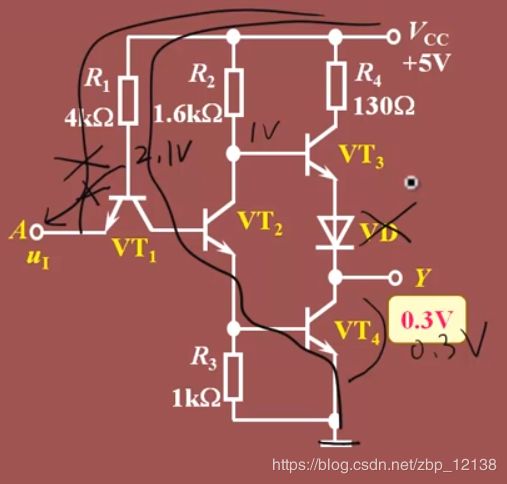

输入电压为输入高电平时

输入为3.6V,则VT1为4.3V,下面的三个PN结均可导通

故VT1基极电位被钳制在2.1V,VT2和VT4饱和导通

于此同时Uc2 = Ub3 = 0.3+0.7 = 1V,二极管VD必然截止

输入端悬空时

输入级电路不构成回路,则VT1的发射结自然是截止的。后续分析与输入高电平时基本一致

TTL电路的某输入端悬空,等效于该端接入逻辑高电平。

悬空易引入干扰,故应对不用的输入端作相应的处理。

输入端通过一个电阻接地时

-

只要输入端电阻Re >= 2.5 千欧

就可以使得u1 达到1.4V ,从而使非门输出电压Uo = UoL = 0.3V -

只要输入端电阻Re <= 0.7 千欧

则非门输出电压Uo = UoH = 3.6V

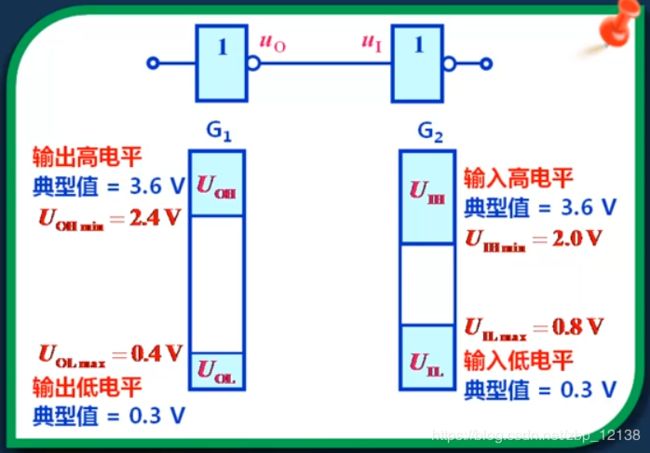

输入、输出的特性参数

这里的高低电平都不是一个确定的数,而是一个范围

输入信号

-

输入高电平 :

对应于逻辑"1"的输入电平,典型值3.6V,TTL规定最小输入高电平为2.0V,即开门电平 -

输入低电平 :

对应于逻辑"0"的输入电平,典型值0.3V,TTL规定输入低电平的上限为0.8V,即关门电平

输出信号

-

输出高电平:

门电路处于关门状态(截止状态)时的输出电平,此时输出信号对应逻辑"1",典型值3.6V,规定输出高电平的下限为2.4V -

输出低电平:

门电路处于开门状态(导通状态)时的输出电平,此时输出信号对应逻辑"0",典型值0.3V,规定输出低电平的上限为0.4V

开门状态

门电路输出为输出低电平时(对应逻辑“0”),称逻辑门处于开门状态,又称导通状态

关门状态

门电路输出为输出高电平时(对应逻辑“1”),称逻辑门处于关门状态,又称截止状态

开门电平

为了保证非门工作在开门状态的输入电平

开门电平指此时允许输入的高电平的最小值(2.0V )

关门电平

为了保证非门工作在关门状态的输入电平

开门电平指此时允许输入的低电平的最大值(0.8V )

开门电阻

开门电阻 :

为了使非门可靠地工作在开门状态,输入电阻所允许的最小阻值(2.5 千欧)

即输入端大电阻的下限

关门电阻

关门电阻 :

为了使非门可靠地工作在关门状态,输入电阻所允许的最大阻值(0.7 千欧)

即输入端小电阻的上限

TTL电平规范

输入高电平:

- 典型值为3.6V

- 最小值为2.0V

输入低电平 :

- 典型值为0.3V

- 最大值为0.8V

输出高电平:

- 典型值为3.6V

- 最大值为2.4V

输出低电平:

- 典型值为0.3V

- 最大值为0.4V

输入端噪声容限

接着上面的内容,细心的你应该已经看出来,输入高/低电平的最小值与输出高/低电平的最小值之间有一段间隔:

数字电路工作时,如果输入信号上叠加有噪声电压(干扰信号),则可能造成信号逻辑混乱,使得电路工作错误。

但是,逻辑高电平、低电平并不是一个固定值,而是一个电压范围。因此,只要输入端存在的噪声电压幅度不超过允许的范围,输入信号就不会发生逻辑混乱。

从上图也可以看出,输入高/低电平时的噪声容限都为0.4V

逻辑门的速度指标

TTL逻辑门电路工作时,当输入信号变化后,需要经过一定的时延后,输出端才能建立起相应的稳定输出信号。

- 传输延迟时间:

输出信号波形滞后于输入信号波形的时间,是衡量门电路工作速度的重要性能指标。

指标为纳秒级

导通传输延迟时间

输出电压由高电平变为低电平的传输延迟时间

用来描述门电路开门的速度

截止传输延迟时间

输出电压由低电平变为高电平的传输延迟时间

用来描述门电路关门的速度

平均传输延迟时间

用来描述门电路工作的平均速度

特殊TTL逻辑门

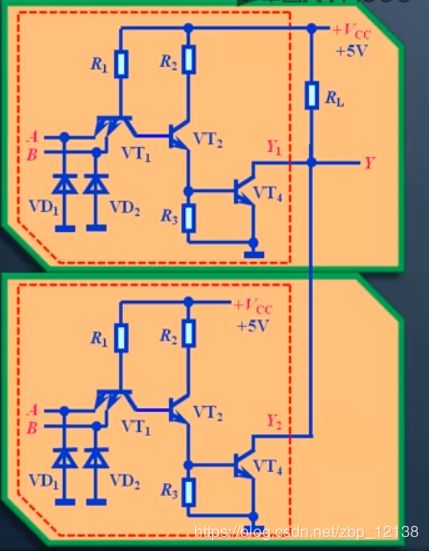

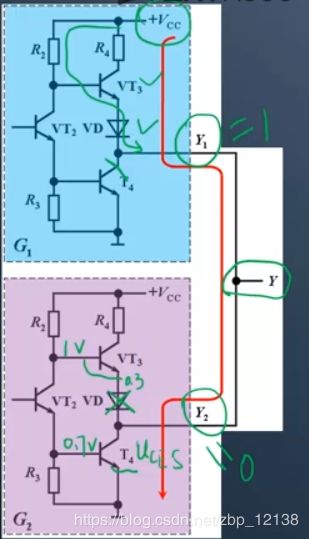

普通TTL逻辑门的缺陷

- 普通TTL逻辑门的缺陷主要在输出级上:

多个普通TTL门的输出端不能共接在同一根导线上

- Y1和Y2同为高电平或者低电平时:

输出端共接对电路工作状态、逻辑关系不会有任何影响,输出Y对应为高电平或低电平。 - Y和Y2一个高电平、一个低电平时:

输出端共接会带来严重危害。

- Y1为高电平: 门G1的T3管饱和导通、T4 管截止;

- Y2为低电平: 门G2的T3管截止,而T4管饱和导通。

这时,由上至下会产生通路,产生大电流,带来严重危害,而输出端会输出一个非1非0的量,从而造成混乱

总线和总线上的分时复用

-

总线( Bus ):

总线是数字信息的一组公共通道,多个前级单元、设备的输出端和

后级单元、设备的输入端共接其上,采用分时复用的方式,使多个前级单元的输出信号通过公共总线,输出给相应的后级单元,以完成数据的传输。

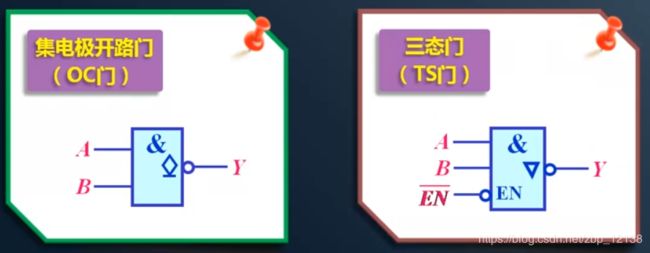

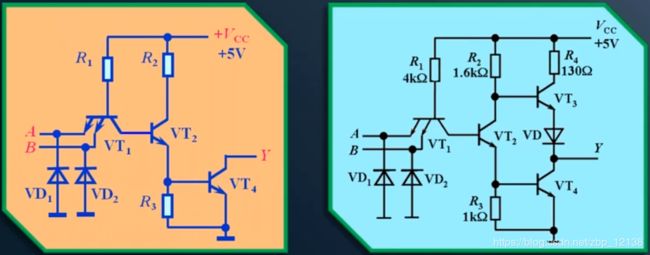

集电极开路门

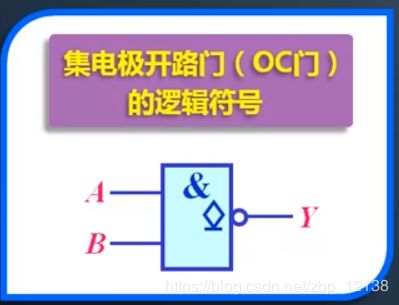

1. OC门的电路结构和逻辑符号

左边的OC门是将右边的TTL门VT4晶体管上面的负载去掉而得来的

2. OC门的功能分析

OC门使用时,输出端要外接一个上拉电阻R,和正电源+Vcc相连

当输入中有低电平时

当输入全为高电平时

3. OC门的工作特点

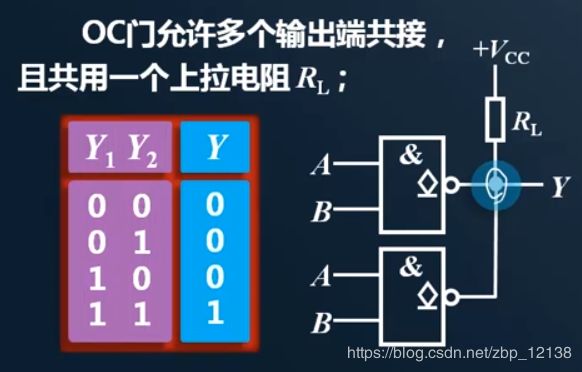

OC门允许多个输出端共接,且共用一个上拉电阻R:

外接电阻会影响了OC门的开关速度,所以OC门一般用于对工作速度要求不高的场合。

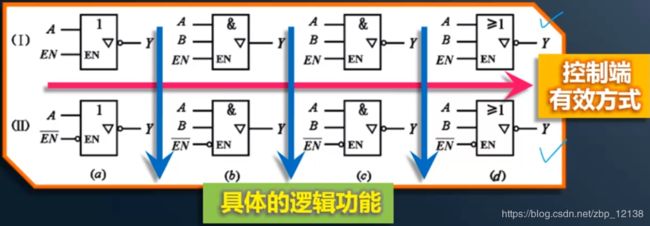

三态门

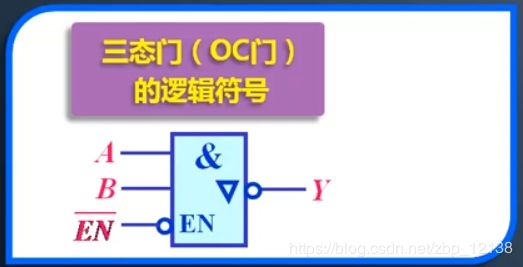

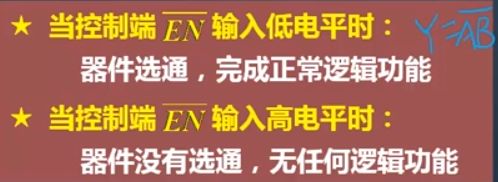

1. 三态门的电路结构和逻辑符号

下面是三态门的逻辑符号:

这种控制方式为控制端低有效方式,想要做到控制端高有效方式,也很简单:

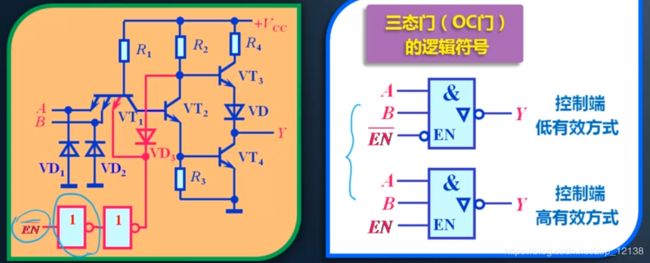

2. 三态门的分类和符号阅读

举个例子:

举个例子:

(II)( c )控制端低有效的两输入与非三态门

(I) ( d )控制端高有效的两输入或非三态门

OC门和三态门的性能比较

- 三态门的开关速度比OC门快

- 在总线结构中:

允许接入总线的三态门的个数,原则上不受约束。

允许接入总线的OC门要受到外用的上拉电阻的取值范围的限制。 - OC门输出端可以实现“线与”逻辑功能,而三态门不行。

CMOS逻辑门

MOS场效应管

CMOS逻辑门的由来

采用P沟道和N沟道增强型M0S管组成耳补电路实用性最广,是目前应用最广泛的集成电路之一。

CMOS集成逻辑的工作特点

★功耗极低

★芯片集成度高

★温度稳定性好

★电路结构简单,器件制作成本低

★输入阻抗高,可达10的8次方,扇出能力强

★电源电压范围宽

★输出逻辑摆幅大

★抗干扰能力强

- 输入高、低电平大小受电源电压的限制。

- CMOS电路的工作速度比TTL电路稍慢,

CMOS电平规范

- TTL器件大都采用+5V电源供电

- CMOS器件电源电压范围广泛

4. 多余输入端的处理

多余输入端悬空所带来的问题

- 容易引入外界干扰

- 引起逻辑运算的错误

解决方法:

在保证逻辑功能正确的前提下,给多余输入端接入确定电平

TTL逻辑门电路

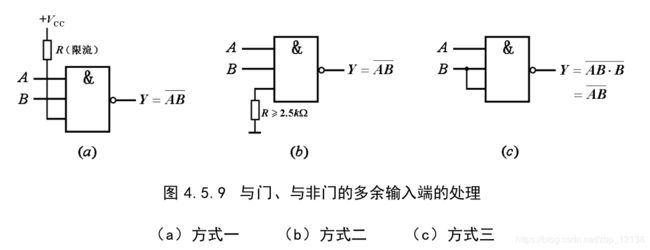

与门、与非门

对于与门、 与非门,多余输入端应接入高电平。

例如,3输入与非门Y= ABC ‾ \overline{\text{ABC}} ABC,C输入端多余,意味着实际要完成的功能是Y= AB ‾ \overline{\text{AB}} AB,此时C端接入高电平,Y= ABC ‾ \overline{\text{ABC}} ABC= AB.1 ‾ \overline{\text{AB.1}} AB.1= AB ‾ \overline{\text{AB}} AB,不影响逻辑功能。

具体方式:

- 将其通过电阻R (约几千欧,限流作用)接正电源;

- 通过大于2.5千欧的电阻接地;

- 在前级门的带载能力有富余的情况下,可以和有用输入端共接。

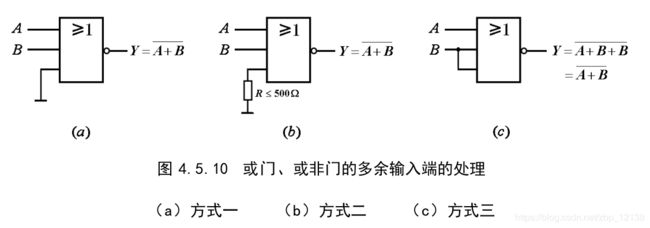

或门、或非门

对于或门、或非门,多余输入端应接入低电平。

例如,3 输入或非门Y= A+B+C ‾ \overline{\text{A+B+C}} A+B+C ,C 输入端多余,意味着实际要完成的功能是Y= A+B ‾ \overline{\text{A+B}} A+B 。

此时 C 端接入低电平,Y= A+B+C ‾ \overline{\text{A+B+C}} A+B+C= A+B+0 ‾ \overline{\text{A+B+0}} A+B+0= A+B ‾ \overline{\text{A+B}} A+B ,不影响逻辑功能。

具体方式:

- 将其直接接地;

- 通过小于 500Ω 的电阻(关门电阻 700Ω,为了保证安全,

阻值降至 500Ω)接地; - 在前级门的带载能力有富余的情况下,可以和有用输入端

共接。

与或非门

对于与或非门,则又要分为两种情况:

已知与或非表达式为Y= AB+CD ‾ \overline{\text{AB+CD}} AB+CD

-

如果与或非逻辑中,某个与单元(例如 CD 单元)整个多余,意味着实际要完成的功能是Y= AB ‾ \overline{\text{AB}} AB 。则该与单元的所有输入端接入低平,Y= AB+00 ‾ \overline{\text{AB+00}} AB+00= AB ‾ \overline{\text{AB}} AB ,不影响逻辑功能,具体方式和“或门、或非门情况”类似,不再赘述。

-

如果与或非逻辑中,与单元的某个输入端(例如输入端 D)多

余,意味着实际要完成的功能是Y= AB+C ‾ \overline{\text{AB+C}} AB+C 。则该输入端接入高平,Y= AB+C.0 ‾ \overline{\text{AB+C.0}} AB+C.0= AB+C ‾ \overline{\text{AB+C}} AB+C ,不影响逻辑功能,具体方式和“与门、与非门情况”类似,不再赘述。

CMOS 门电路

CMOS 门电路的多余输入端的处理方法与 TTL电路的异同在于:

★ 首先,CMOS 器件的输入阻抗很大,对干扰信号的捕捉能力很强,很容易在悬空输入端引入。同时,输入端是 MOS 管的绝缘栅极,它与其他电极间的绝缘层很容易被击穿,虽然内部也设置有保护电路,但只适合防止稳态过压,对瞬间过压保护效果差。这意味着,外接干扰信号的引入,很容易损坏器件。

所以,CMOS 门电路的多余输入端不允许悬空,必须加以处理。而如果TTL 门电路的悬空输入端引入了干扰信号,虽然会造成逻辑错误,但一般不至于损坏器件。

★ 多余输入端的处理原则是保证电路要实现的逻辑功能正确,所以, 不论是 是 TTL 还是 CMOS 电路 ,处理原则和方法是一致的。简言之,多余输入端参与的是“与”运算,就接入高电平;参与的是“或”运算,就接入低电平。

★ 具体处理方式的差异在于:

TTL门电路输入端通过一个电阻接地,则该端输入电平和电阻值大小有关。但是,对于 CMOS 门电路,不论它的输入电平是高电平还是低电平,其输入电流都非常小,所以,CMOS门电路的多余输入端通过一个电阻接地时,不论电阻多大,该端都等效输入低电平。

除上述几点外,CMOS 门电路的多余输入端的处理方法,与 TTL

门相同。