基于FPGA数字混频器的设计(1)

基于FPGA数字混频器的设计

1 混频原理

混频即两个不同频率之间的混合,得到第三个频率。数字混频器的设计也是FPGA数字信号处理中基础入门的设计之一,混频便是两个信号相乘得它们的和频率和差频率。数字混频在通信的调制、解调、DUC(数字上变频)、DDC(数字下变频)等系统中广泛应用。通常把其中一个信号称为本振信号(local oscillator),另一个信号称为混频器的输入信号。

2 设计目标

1) 在采样频率为44.1KHZ下通过DDS产生2KHZ的本振信号和3KHZ的外部输入信号。对两个信号分别进行相加处理和相乘处理。使用matlab分析信号频域和时域的变化。

2)在1)的基础上完成2khz*3khz滤除相乘后的直流分量设计。

3 matlab设计验证

clear all

close all

clc

FS = 44100;%采样率

fc = 2000; %本振信号 2khz

fe = 3000; %外部输入信号 3khz

N = 1024;%1024点一个正玄周期

Q = 32; %量化32bit

t =0:2*pi/FS:2*pi*N/FS;

sin_osc =sin(t*fc);

sin_e =sin(t*fe);

sin_mult = sin_osc.*sin_e;

sin_add = sin_osc+sin_e;

f_osc =fft(sin_osc,N);

f_osc=20*log(abs(f_osc))/log(10); %换算成dBW单位

ft=[0:(FS/N):FS/2]; %转换横坐标以Hz为单位

f_osc=f_osc(1:length(ft));

f_e =fft(sin_e,N);

f_e=20*log(abs(f_e))/log(10); %换算成dBW单位

f_e=f_e(1:length(ft));

f_add =fft(sin_add,N);

f_add=20*log(abs(f_add))/log(10); %换算成dBW单位

f_add=f_add(1:length(ft));

f_mult =fft(sin_mult,N);

f_mult=20*log(abs(f_mult))/log(10); %换算成dBW单位

f_mult=f_mult(1:length(ft));

figure,

hold on

subplot(221),plot(t(1:128),sin_osc(1:128),'-');

legend('sinosc');title('2K HZ');

subplot(222),plot(t(1:128),sin_e(1:128),'-');

legend('sine');title('3K HZ');

subplot(223),plot(t(1:128),sin_add(1:128),'-');

legend('sinadd');title('add ');

subplot(224),plot(t(1:128),sin_mult(1:128),'-');

legend('sinmult');title('mult ');

grid;

hold off

figure,

hold on

subplot(221);plot(ft,f_osc);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图 2KHZ','fontsize',8);legend('sinosc');

subplot(222);plot(ft,f_e);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图3KHZ','fontsize',8);legend('sine');

subplot(223);plot(ft,f_mult);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图1KHZ 和 6','fontsize',8);legend('sinmult');

subplot(224);plot(ft,f_add);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图2KHZ 和 3KHZ','fontsize',8);legend('sinadd');

hold off

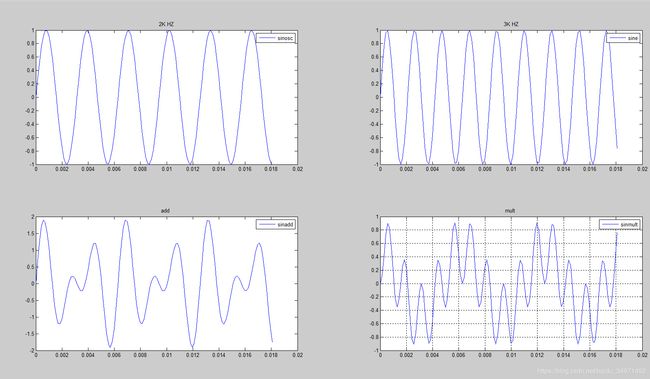

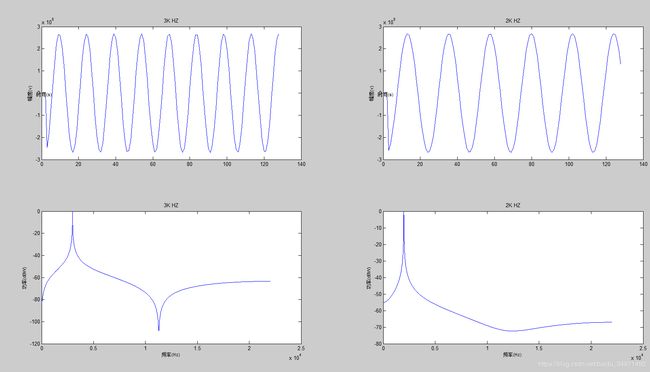

如上图1所示,图1左上1为2khz本振信号sin波,图1右上2为3khz外部输入sin波,图1左下1为2khz+3khz时域波形,图1右下1为2KHZ*3KHZ时域波形。

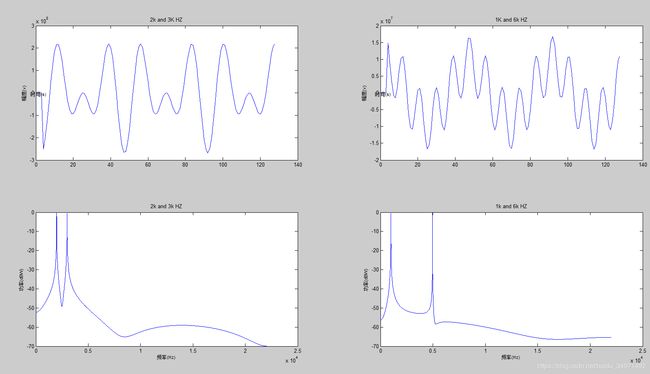

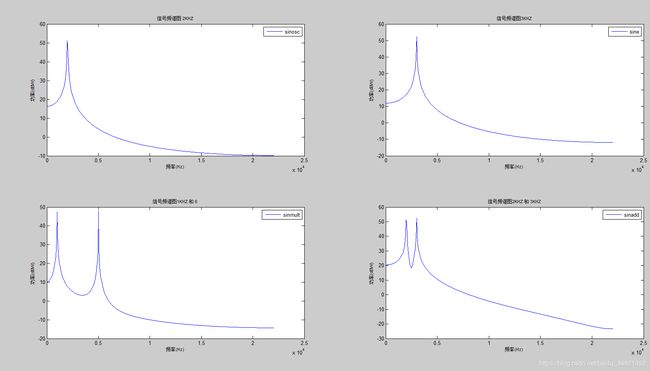

如上图2所示,左下1为两个信号相乘所得频域图形,分析可知2KHZ*3KHZ得到了1KHZ和6KHZ,右下1为两个信号相加所得频域图像,分析可知2khz+3khz得到了2khz 和 3khz。

4 FPGA的程序设计

1) 相加模块设计

`timescale 1ps/1ps

module digital_add(

input mclk,//45.1584MHZ

input reset_n,

input signed[31:0] pcm_in1,

input signed[31:0] pcm_in2,

output signed[31:0] pcm_out

);

localparam LAST_CYCLE = 1023;

reg [9:0] i;

reg signed [32:0] pcm_r;

assign pcm_out = pcm_r[32:1];

always @(posedge mclk or negedge reset_n) begin

if(!reset_n) begin

i<= 0;

pcm_r <= 33'b0;

end

else begin

i <= i + 1;

if(i == 0) pcm_r <= pcm_in1 + pcm_in2;//add

end

end

endmodule

相加会产生位扩展。

2)相乘模块设计

timescale 1ps/1ps

module digital_mult(

input mclk,//45.1584MHZ

input reset_n,

input signed[31:0] pcm_in1,

input signed[31:0] pcm_in2,

output signed[31:0] pcm_out

);

localparam LAST_CYCLE = 1023;

reg [9:0] i;

reg signed [63:0] pcm_r;

assign pcm_out = pcm_r[63:32];

always @(posedge mclk or negedge reset_n) begin

if(!reset_n) begin

i<= 0;

pcm_r <= 0;

end

else begin

i <= i + 1;

if(i == 0) pcm_r <= pcm_in1*pcm_in2;//mult

end

end

endmodule

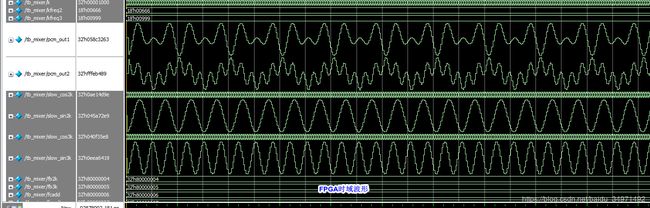

观察图3 可知matlab仿真基本和FPGA时域波形一致,设计成功。接下来对FPGA设计处理的数据进行分析。

由图4和图5与图1和图2对比,FPGA设计成功。

欢迎关注FPGA开源工作室微信公众号,学习了解更多FPGA知识。