ARM_Instruction_Set_Encoding_hacking(ARM指令集编码格式解读)

原地址:https://www.cnblogs.com/zengjfgit/p/4377243.html 作者:zengif

说明:

1、本文参考的书籍《ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition》中的Chapter A5: ARM Instruction Set Encoding.

2、本人对本文最终效果中的表格缩进没有对齐的现象表示歉意,因为目前本人解决不了 :)

3、本文的解读流程如下:

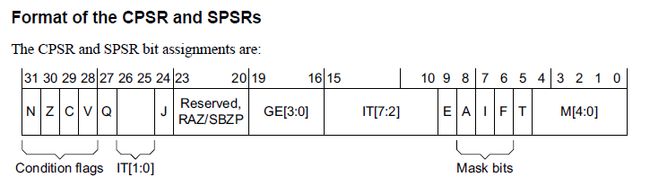

1、Format of the CPSR and SPSRs:因为CPSR中有影响指令执行的条件标志;

2、The major subdivisions of the ARM instruction set:这里细分ARM指令为7个种类;

3、The condition code field:对指令中的条件位域进行了解读;

4、Data-processing and miscellaneous instructions:针对the major subdivisions of the ARM instruction set中的7中ARM指令种类,对第一种“Data-processing and miscellaneous instructions”进行了解读;

5、Data-processing (register):针对Data-processing and miscellaneous instructions中的14种指令,对第一种“Data-processing (register)”进行了解读;

6、AND (register):针对Data-processing (register)中的22种指令,对第一种“AND (register)”进行了解读;

4、如您在3中看到的,本文仅仅是对32位的ARM指令的一种简单的理解性解读;

********************************目录******************************

一、为什么要解读ARM指令编码?

二、Format of the CPSR and SPSRs(CPSR and SPSRs格式):

三、The major subdivisions of the ARM instruction set(细分ARM指令集):

四、The condition code field(条件位域):

五、Data-processing and miscellaneous instructions(数据处理和杂项指令):

六、Data-processing (register)(数据处理(寄存器)):

七、AND (register):

****************************************************************

一、为什么要解读ARM指令编码?

以前每次当我看到或者听说汇编指令的时候,我都会觉得很好奇:

1、汇编指令入是如何组成的?

2、mov r2, 0x33: 这条ARM汇编指令是如何保存指令中的mov,r2,0x33各部分?

3、bic r1, r1, r2:这条ARM汇编指令是如何保存指令中的bic,r1,r1,r2各部分?

4、一条ARM汇编指令那么长,怎么可能32位就能包含?而且还包含了判断条件在里面;

虽然很多时候好奇,但是毕竟个人知识水平有限,并没有能够理解这里面的原理,也许今天解读完这章英文文档能够从中得知玄机.

二、Format of the CPSR and SPSRs(CPSR and SPSRs格式):

1、以下是CPSR and SPSRs的位域格式图:

2、由于本文仅仅需要用Condition flags,所以不对其他位域进行解读:

Condition flags, bits[31:28]

Set on the result of instruction execution(设置的指令执行结果). The flags are:

1、N, bit[31] Negative condition flag (负数标志)

2、Z, bit[30] Zero condition flag (0标志)

3、C, bit[29] Carry condition flag (进位标志)

4、V, bit[28] Overflow condition flag (溢出标志)

The condition flags can be read or written in any mode.( 在任何模式下可以对条件标志读取或写入)

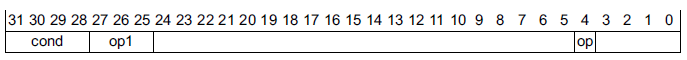

三、The major subdivisions of the ARM instruction set(细分ARM指令集):

1、ARM 指令流是一连串的字对齐的四字节指令流。每个 ARM 指令是一个单一的 32 位字(4字节)。ARM 指令细分编码格式如下图:

2、以下是对细分ARM指令集的位域分布,以及细分出的指令种类说明:

| cond |

op1 |

op |

Instruction classes(指令分类) |

| not 1111 |

00x |

- |

数据处理和杂项指令(本文只对这部分进行分析,其他部分类似) |

| 010 |

- |

加载/存储字或无符号的字节 |

|

| 011 |

0 |

加载/存储字或无符号的字节 |

|

| 1 |

媒体指令 |

||

| 10x |

- |

分支、带链接分支、块数据传输 |

|

| 11x |

- |

协处理器指令或软中断,包括浮点指令和先进SIMD数据传输 |

|

| 1111 |

- |

- |

如果cond字段为0b1111,只能无条件地执行指令 |

| 表格中的op1、op字段中的x、-表示可以是0,也可以是1 |

|||

3、本文后续部分只对Instruction classes(指令分类)中的“数据处理和杂项指令”部分进行解读,其他部分类似,没必要全部解读,毕竟不是为了翻译。

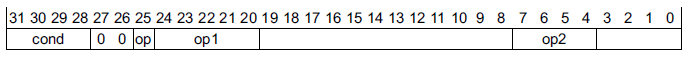

四、The condition code field(条件位域):

1、每一条可条件执行的条件指令都有4位的条件位域(记住,只有四位) ,条件位域的值在0b0000-0b1110之间,如下是条件位域在32位ARM指令中的位置:

2、以下是对条件位域的值的列表,可条件执行指令执行受CPSR的condition flags中对应的位影响:

2、以下是对条件位域的值的列表,可条件执行指令执行受CPSR的condition flags中对应的位影响:

| cond |

助记符 |

意义(整数) |

意义(浮点数) |

条件标志 |

| 0000 |

EQ |

Equal(相等) |

Equal(相等) |

Z == 1 |

| 0001 |

NE |

Not equal(不相等) |

Not equal, or unordered |

Z == 0 |

| 0010 |

CS |

Carry set(进位) |

Greater than, equal, or unordered |

C == 1 |

| 0011 |

CC |

Carry clear(借位) |

Less than(小于) |

C == 0 |

| 0100 |

MI |

Minus, negative(负数) |

Less than(小于) |

N == 1 |

| 0101 |

PL |

Plus, positive or zero |

Greater than, equal, or unordered |

N == 0 |

| 0110 |

VS |

Overflow(溢出) |

Unordered(无序) |

V == 1 |

| 0111 |

VC |

No overflow(没有溢出) |

Not unordered(非无序) |

V == 0 |

| 1000 |

HI |

Unsigned higher (无符号大于) |

Greater than, or unordered |

C == 1 and Z == 0 |

| 1001 |

LS |

Unsigned lower or same |

Less than or equal |

C == 0 or Z == 1 |

| 1010 |

GE |

Signed greater than or equal |

Greater than or equal |

N == V |

| 1011 |

LT |

Signed less than |

Less than, or unordered |

N != V |

| 1100 |

GT |

Signed greater than |

Greater than(大于) |

Z == 0 and N == V |

| 1101 |

LE |

Signed less than or equal |

Less than, equal, or unordered |

Z == 1 or N != V |

| 1110 |

None (AL) |

Always (unconditional) |

Always (unconditional) |

Any |

| 1、Unordered means at least one NaN operand. 无序的意思是至少有一个非数字操作数 2、HS (unsigned higher or same) is a synonym for CS. HS(无符号大于或相同)是同义词CS. 3、LO (unsigned lower) is a synonym for CC. LO(无符号更低)是同义词CC. 4、AL is an optional mnemonic extension for always, except in IT instructions. AL是always的助记符,IT指令除外. |

||||

3、汇编语言中溢出和进位的不同:

1、对于非符号数来说,不存在溢出的问题,它的进位就相当于符号数中的溢出;

2、而对于符号数来说,不存在进位的问题:

1、两个正数相加(或一个正数减一个负数)得到负数;

2、两个负数相加得到正数,就是溢出了;

3、一个正数和一个负数相加不可能溢出。

五、Data-processing and miscellaneous instructions(数据处理和杂项指令):

1、数据处理和杂项指令的位域分布图如下:

| op |

op1 |

op2 |

Instruction or instruction class |

Variant |

| 0 |

not |

xxx0 |

Data-processing (register) |

- |

| 0xx1 |

Data-processing (register-shifted register) |

- |

||

| 10xx0 |

0xxx |

Miscellaneous instructions |

- |

|

| 1xx0 |

Halfword multiply and multiply accumulate |

- |

||

| 0xxxx |

1001 |

Multiply and multiply accumulate |

- |

|

| 1xxxx |

1001 |

Synchronization primitives |

- |

|

| not |

1011 |

Extra load/store instructions |

- |

|

| 11x1 |

Extra load/store instructions |

- |

||

| 0xx1x |

1011 |

Extra load/store instructions, unprivileged |

- |

|

| 11x1 |

Extra load/store instructions |

- |

||

| 1 |

not |

- |

Data-processing (immediate) |

- |

| 10000 |

- |

16-bit immediate load, MOV (immediate) |

v6T2 |

|

| 10100 |

- |

High halfword 16-bit immediate load, MOVT |

v6T2 |

|

| 10x10 |

- |

MSR (immediate), and hints |

- |

3、本文后续部分只对Instruction or instruction class中的“Data-processing (register)(数据处理(寄存器))”部分进行解读,其他部分类似,没必要全部解读,毕竟不是为了翻译。

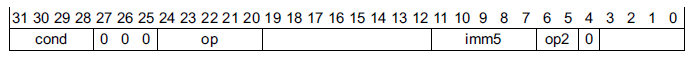

六、Data-processing (register)(数据处理(寄存器)):

1、数据处理(寄存器)位域分布如下图所示:

2、这对数据处理(寄存器)位域的说明表,本人就不对内容进行翻译了,如果有困难,可以使用bing,google翻译,不建议使用其他的翻译软件,不解释原因 :)

| op |

op2 |

imm5 |

Instruction |

See |

| 0000x |

- |

- |

Bitwise AND (本文只对该指令进行解读) |

AND (register) on page A8-326 |

| 0001x |

- |

- |

Bitwise Exclusive OR |

EOR (register) on page A8-384 |

| 0010x |

- |

- |

Subtract |

SUB (register) on page A8-712 |

| 0011x |

- |

- |

Reverse Subtract |

RSB (register) on page A8-576 |

| 0100x |

- |

- |

Add |

ADD (register, ARM) on page A8-312 |

| 0101x |

- |

- |

Add with Carry |

ADC (register) on page A8-302 |

| 0110x |

- |

- |

Subtract with Carry |

SBC (register) on page A8-594 |

| 0111x |

- |

- |

Reverse Subtract with Carry |

RSC (register) on page A8-582 |

| 10xx0 |

- |

- |

See Data-processing and miscellaneous instructions on page A5-196 |

|

| 10001 |

- |

- |

Test |

TST (register) on page A8-746 |

| 10011 |

- |

- |

Test Equivalence |

TEQ (register) on page A8-740 |

| 10101 |

- |

- |

Compare |

CMP (register) on page A8-372 |

| 10111 |

- |

- |

Compare Negative |

CMN (register) on page A8-366 |

| 1100x |

- |

- |

Bitwise OR |

ORR (register) on page A8-518 |

| 1101x |

00 |

00000 |

Move |

MOV (register, ARM) on page A8-488 |

| not 00000 |

Logical Shift Left |

LSL (immediate) on page A8-468 |

||

| 01 |

- |

Logical Shift Right |

LSR (immediate) on page A8-472 |

|

| 10 |

- |

Arithmetic Shift Right |

ASR (immediate) on page A8-330 |

|

| 11 |

00000 |

Rotate Right with Extend |

RRX on page A8-572 |

|

| not 00000 |

Rotate Right |

ROR (immediate) on page A8-568 |

||

| 1110x |

- |

- |

Bitwise Bit Clear |

BIC (register) on page A8-342 |

| 1111x |

- |

- |

Bitwise NOT |

MVN (register) on page A8-506 |

3、本文后续部分只对Instruction中的“Bitwise AND”部分进行解读,其他部分类似,没必要全部解读,毕竟不是为了翻译。

七、AND (register):

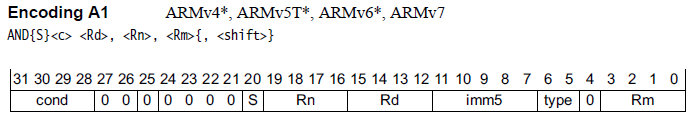

1、本文只对AND (register)中的Encoding A1 ARMv4*, ARMv5T*, ARMv6*, ARMv7指令进行解读,以下是位域分布图:

2、指令编码位域意义:

1、cond: 是条件码

2、S: 代表该指令是否会影响CPSR的状态标志

3、Rn: 是保存第一个操作数的寄存器

4、Rm: 保存第二个操作数的寄存器

5、Rd: 保存运行结果的寄存器

6、imm5: 保存Rm中的数据要被移多少位

7、type: 移位的类型,向左移还是向右移,以及是否是循环移位等等

3、汇编语法:

1、AND{S}{} {

2、解析:

1、S: 如果有S标志,指令运行结果会更新CPSR状态标志。否则,该CPSR状态标志不会更新;

2、: See Standard assembler syntax fields on page A8-287.

3、

4、

5、

6、

3、AND指令Demo:

1、ADD R0,R2,R3,LSL#1 ; R0 = R2 + (R3 << 1)

2、解析:

1、S:有S标志,说明运算结果会影响CPSR寄存器的状态标志位;

2、

3、

4、

5、

6、