2016年12月7日,采用三星10nm工艺制造的高通骁龙835跑分遭到曝光。

8日,采用台积电10nm工艺制造的华为麒麟970也遭到媒体曝光。

此前,英特尔宣称,将于2017年发布采用自家10nm工艺制造的移动芯片。

格罗方德也声称自研10nm工艺。

…………

几个月前,GlobalFoundries宣布将会推进7nm FinFET工艺。

三星也购买了ASML的NXE3400光刻机,为生产7nm芯片作准备,并计划在2018年上半年实现量产。

近日,台积电又声称,将在2017年初开始7nm的设计定案,并在2018年初量产,对5nm、3nm和2nm工艺的相关投资工作也已开始。

…………

从14nm到10nm,从10nm到7nm,还有所谓的5nm、3nm和2nm,芯片工艺的竞争程度不断升级。那么,芯片界的这场“战争”会结束吗?芯片工艺的未来又在哪里呢?

现阶段的芯片工艺

技术上,近年来除了FinFIT技术外,三星、英特尔等芯片厂商纷纷投入到FD-SOI(全耗尽绝缘体硅)工艺、硅光子技术、3D堆叠技术等的研究中,以求突破FinFET的制造极限,拥有更多的主动权。各种新技术中,犹以3D堆叠技术为研究重点。

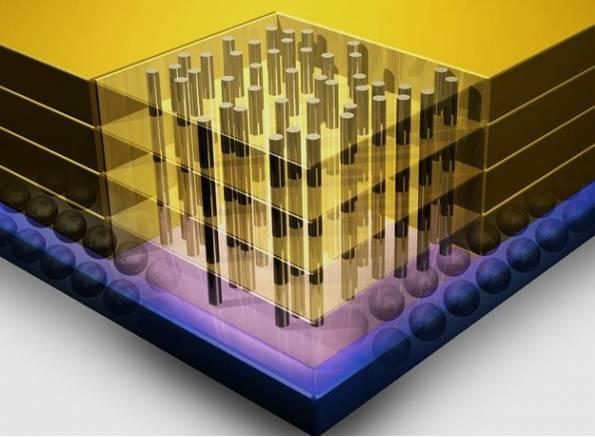

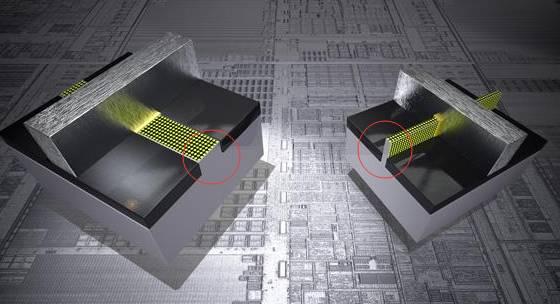

3D堆叠技术通过在存储层上叠加逻辑层,将芯片的结构由平面型升级成立体型,大大缩短互连线长度,使得数据传输更快,所受干扰更小。

目前,这样的3D技术在理论层面已有较大进展,并在实践中得到初步应用。2013年,三星推出了3D圆柱形电荷捕获型栅极存储单元结构技术,垂直堆叠可达24层。同年,台积电与Cadence合作开发出了3D-IC的参考流程。2015年,英特尔和美光合作推出了3D XPoint技术,使用该技术的存储芯片目前已经量产。

材料上,目前制造芯片的原材料以硅为主。不过,硅的物理特性限制了芯片的发展空间,正在逐渐被弃用。

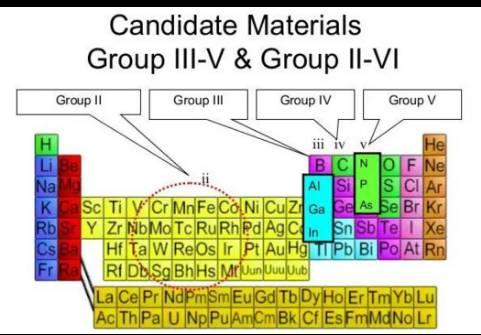

2015年,IBM及合作伙伴三星、GlobalFoundries展示7nm工艺芯片时,使用的是硅锗材料。使用这种材料的晶体管开关速度更快,功耗更低,而且密度更高,可以轻松实现200亿晶体管,晶体管密度比目前的硅基半导体高出一个量级。2015年4月,英特尔也宣布,在达到7nm工艺之后将不再使用硅材料。

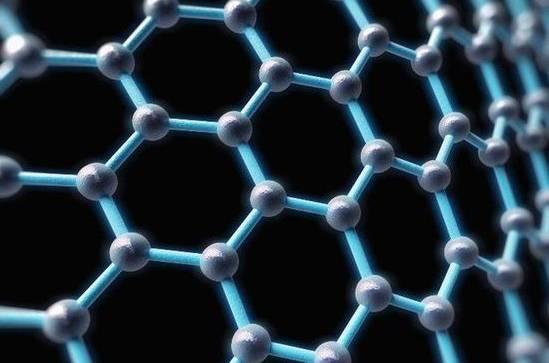

III-V族化合物、石墨烯等新材料为突破硅基芯片的瓶颈提供了可能,成为众多芯片企业研究的焦点,尤其是石墨烯。

相比硅基芯片,石墨烯芯片拥有极高的载流子速度、优异的等比缩小特性等优势。IBM表示,石墨烯中的电子迁移速度是硅材料的10倍,石墨烯芯片的主频在理论上可达300GHz,而散热量和功耗却远低于硅基芯片。麻省理工学院的研究发现,石墨烯可使芯片的运行速率提升百万倍。

并且,随着制作工艺已逐渐成熟,石墨烯原本高昂的成本开始呈下降趋势。2011年底,宁波墨西科技建成年产300吨的石墨烯生产线,每克石墨烯销售价格只要1元。2016年4月,华讯方舟做出了石墨烯太赫兹芯片。

芯片工艺的发展和影响

*摩尔定律

说到芯片的发展,就不得不提先一下主宰半导体发展的摩尔定律。

1965年,仙童半导体公司的工程师戈登·摩尔撰文指出,半导体电路集成的晶体管数量将每年增加一倍,性能提升一倍;之后又修正为每两年增加一倍,这就是著名的摩尔定律。

半导体工业的发展已经符合摩尔定律超过半世纪了,虽然近几年有放缓迹象,但是摩尔定律依然会持续下去。

1971年,Intel发布了第一个处理器4004,它采用10微米工艺生产,仅包含2300多个晶体管。

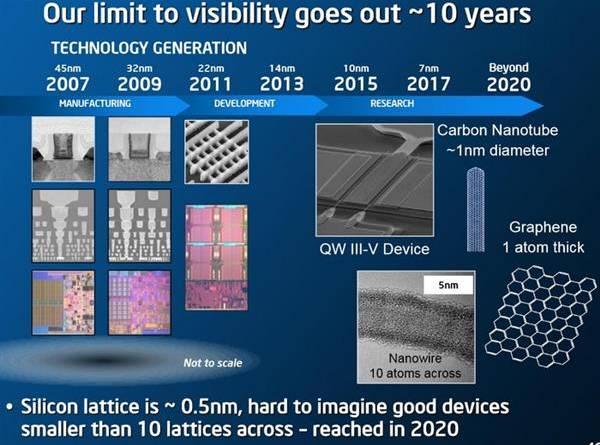

1995年起,芯片制造工艺从0.5μm、0.35μm、0.25μm、0.18μm、0.15μm、0.13μm,发展到90nm、65nm、45nm、32nm、22nm、16nm、14nm,再到目前最新的10nm。

随着芯片的制程工艺不断发展,集成度不断提高,电子产业得以高速发展,每年腾出0.3左右的成本空间。半导体工艺制程变得越来越小,将会有哪些好处呢?

1.制程越小就能塞下更多的晶体管,成本下降

CPU的生产是需要经过7个工序的,分别是:硅提纯,切割晶圆,影印,蚀刻,重复、分层,封装,测试, 而当中的蚀刻工序是CPU生产的重要工作,也是重头技术,简单来说蚀刻就是用激光在硅晶圆制造晶体管的过程,蚀刻这个过程是由光完成的,所以用于蚀刻的光的波长就是该技术提升的关键,它影响着在硅晶圆上蚀刻的最小尺寸,也就是线宽。

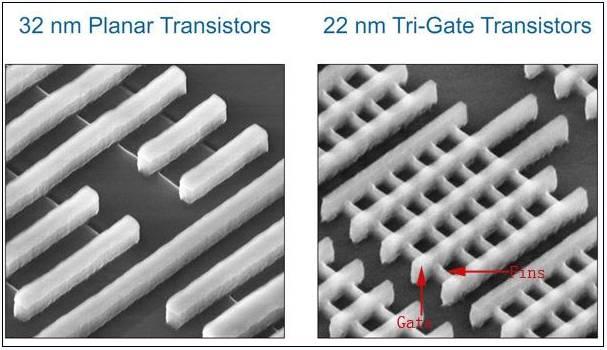

现在半导体工艺上所说的多少nm工艺其实是指线宽,也就是芯片上的最基本功能单位门电路的宽度,因为实际上门电路之间连线的宽度同门电路的宽度相同,所以线宽可以描述制造工艺。缩小线宽意味着晶体管可以做得更小、更密集,而且在相同的芯片复杂程度下可使用更小的晶圆,于是成本降低了。

2.频率更高,电压更低

更先进的半导体制造工艺另一个重要优点就是可以提升工作频率。缩减元件之间的间距之后,晶体管之间的电容也会降低,晶体管的开关频率也得以提升,从而整个芯片的工作频率就上去了。

另外晶体管的尺寸缩小会减低它们的内阻,所需导通电压会降低,这代表着CPU的工作电压会降低,所以我们看到每一款新CPU核心,其电压较前一代产品都有相应降低。另外CPU的动态功耗损失是与电压的平方成正比的,工作电压的降低,可使它们的功率也大幅度减小。

尽管制程变小有许多好处,但并不是无限制的,漏电流问题是当中一个重要因素。

在场效应晶体管的门与通道之间是有一层绝缘的二氧化硅的,作用就是防止漏电流的,这个绝缘层越厚绝缘作用越好。然而随着工艺的发展,这个绝缘层的厚度被慢慢削减,原本仅数个原子层厚的二氧化硅绝缘层变得更薄,进而导致泄漏更多电流,泄漏的电流又增加了芯片额外的功耗。

到了10nm之后,就不能像以往的节点一样,通过简单的缩小栅极宽度来推进工艺制程。往7nm的迁移势必需要昂贵的全新晶体管架构、沟道材料和内部连接。同时还需要全新的Fab工具和材料。

芯片工艺的未来和猜测

7nm以后,5nm 工艺到底有多少实现的可能和意义,更是成为业界的一个争论点。从目前来看,5nm节点前面横亘着若干技术和经济上的挑战,即使能够实现,它也可能会相当昂贵。

实际上,Gartner的分析师Bob Johnson认为,鉴于工艺技术日益严苛的成本和复杂性,7nm可能会跳票到2020年,比一些芯片制造商预期的路线图大约晚一到两年。而这又将反过来影响5nm的面世时间——如果行业决定向5nm继续迈进的话。

“我认为5nm肯定会面世,只是不会是2020年那么早。”Johnson说,可靠的5nm工艺可能会在2023年左右出现。

但芯片制造商比较乐观,他们认为5nm的应用只是时间早晚问题,正在重新评估5nm节点的晶体管技术,并重新修订路线图。根据之前的路线图,FinFET可以下探到7nm,然后寿终正寝,行业需要在5nm节点上选择一种新型的晶体管技术。而且,5nm的唯一选项是横向纳米线FET,也被称为围栅FET。这种材料静电性能很好,只是制造困难而且成本高昂。

IMEC工艺技术副总裁兼逻辑器件研发项目负责人Aaron Thean也表示“5纳米是一个昂贵的节点”。要启用5nm,半导体行业需要在晶圆技术上取得新的突破。光刻技术面临新的挑战,互连技术更是成为进军5nm的最大障碍。

而5nm以后,摩尔定律是否终结,哪些新工艺将诞生,就是更难以预测的事情了。未来,新的材料、新的结构、新的思想,一切都将迎来革命,而革命必将淘汰一些东西、洗刷一些东西、诞生一些东西。