Quartus-II 全加器的设计

Quartus-II 全加器的设计

一、全加器的实验原理

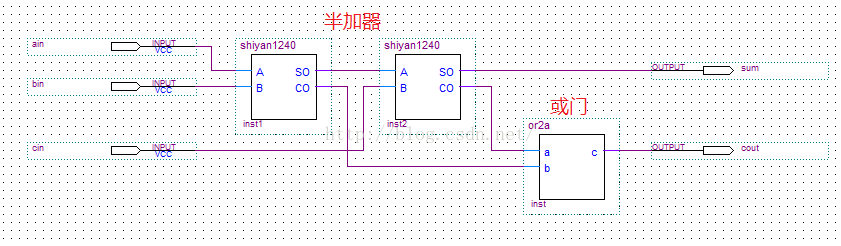

全加器可以由两个半加器和一个或门连接而成,这样得到的半加器电路称为顶层文件。

那么就要先设计好半加器和或门,全加器来调用半加器和或门就可以了。半加器的设计已经在前面提到过了。半加器设计过程链接:http://blog.csdn.net/zhengqijun_/article/details/53284245

下面全加器的设计采用层次结构的VHDL程序设计方法,采用元件例化语句。

二、全加器电路图

三、设计步骤

1. 建立工程。

2. 编写VHDL文件。

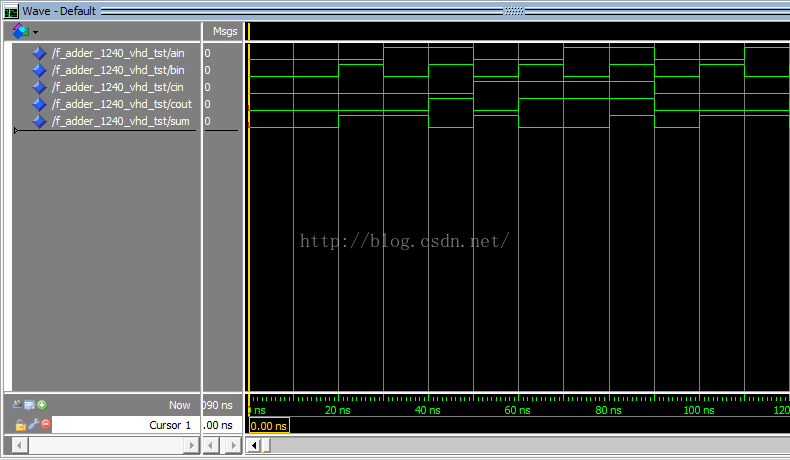

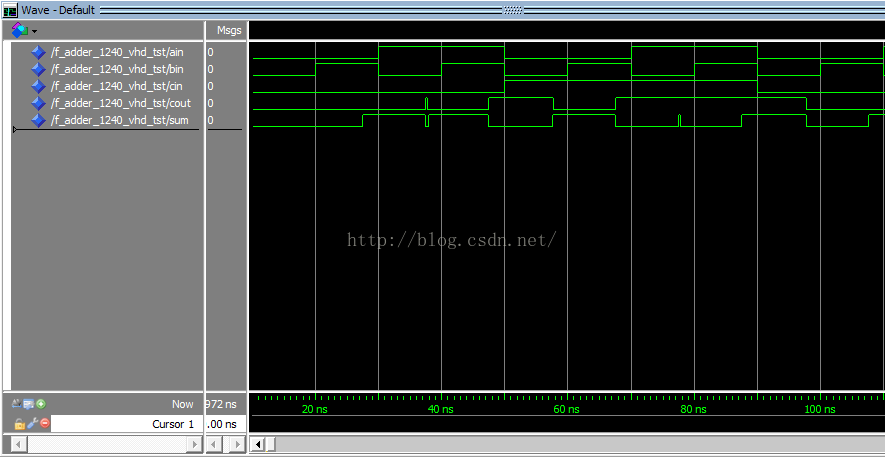

3. 仿真波形。(这里采用modelsim仿真波形)

四、参考程序

1. 半加器

LIBRARY IEEE; --库文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS --实体

PORT( --端口定义

A : IN STD_LOGIC;

B : IN STD_LOGIC;

SO : OUT STD_LOGIC;

CO : OUT STD_LOGIC

);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder IS --结构体

BEGIN

SO <= A XOR B;

CO <= A AND B;

END ARCHITECTURE fh1; LIBRARY IEEE; --库文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT(a, b : IN STD_LOGIC; c : OUT STD_LOGIC);

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b;

END ARCHITECTURE one;3. 全加器

LIBRARY IEEE; --库文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS --实体

PORT(ain,bin,cin : IN STD_LOGIC;

cout, sum : OUT STD_LOGIC);

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS --结构体

COMPONENT h_adder --元件例化语句

PORT(A,B : IN STD_LOGIC; CO,SO : OUT STD_LOGIC);

END COMPONENT;

COMPONENT or2a --元件例化语句

PORT(a,b : IN STD_LOGIC; c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL net1,net2,net3 : STD_LOGIC;

BEGIN

u1 : h_adder PORT MAP(A=>ain, B=>bin, CO=>net2, SO=>net1); --连接关系

u2 : h_adder PORT MAP(net1, cin, net3, sum);

u3 : or2a PORT MAP(a=>net2, b=>net3, c=>cout);

END ARCHITECTURE fd1;1. 时序仿真

2. 功能仿真

经过验证,时序仿真图和功能仿真图均符合要求,结果是正确的。